Fターム[5B018LA05]の内容

記憶装置の信頼性向上技術 (13,264) | 電源 (239) | 電圧比較、検出 (84) | 電源断の予告信号 (24)

Fターム[5B018LA05]に分類される特許

1 - 20 / 24

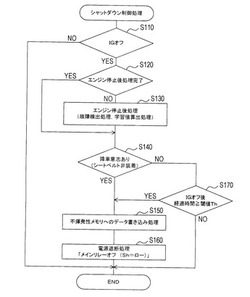

車両用電子制御装置

【課題】車両用電子制御装置において、車両がIG(イグニッション)オフ状態になってからの不揮発性メモリへのデータ書き込み回数を低減する。

【解決手段】車両がIGオフ状態になったこと(S110:YES)を条件に、バックアップ対象のデータを書き換え可能な不揮発性メモリに書き込む書込処理(S150)を行い、その書込処理が終了した後、自身への電源電圧の供給が停止されるようにするための電源遮断処理(S160)を行う電子制御装置では、車両がIGオフ状態になったことを検出すると(S110:YES)、運転者がシートベルトを装着しているか否かを示すシートベルト信号に基づいて、運転者が降車の意志を有しているか否かを判定する(S140)。そして、シートベルト信号が「非装着」を示す状態となり、運転者が降車の意志を有していると判定したなら(S140:YES)、書込処理(S150)を実施するようになっている。

(もっと読む)

記憶装置のデータ保護装置

【課題】キャッシュ領域に転送済みのデータが消失することを防止することが可能な記憶装置のデータ保護装置を提供すること。

【解決手段】制御装置10に備わった、データが格納される不揮発性データ記憶領域14と、不揮発性データ記憶領域14に格納されるデータを一時的に保存するキャッシュ領域15とを有する記憶装置13のデータ保護装置であって、入力電源から供給される電源の電圧を所定の電圧に変換する内部電源装置11と、入力電源から供給される電源の電圧を監視し該電圧の低下を検出した時に電圧低下信号を出力する電源監視回路12と、電圧低下信号を受信したときキャッシュ領域15に保存されたデータを不揮発性データ領域14に書き込む書き込み指令を出力する中央演算処理回路16と、前記書き込み指令が出力されたとき、キャッシュ領域15に保存されたデータを不揮発性データ記憶領域14に書き込むようにした記憶装置のデータ保護装置。

(もっと読む)

メモリ・バックアップのための電力分離

【課題】電力分離およびバックアップ・システムを開示すること。

【解決手段】電源異常状態が検出される時に、一時ストレージをSDRAMにフラッシュする。フラッシュの後に、インターフェースを停止し、電力を、SDRAMサブシステムを除くチップの大半から除去する。SDRAMサブシステムは、データをSDRAMからフラッシュ・メモリにコピーする。その途中で、データを暗号化し、かつ/またはデータ完全性署名を計算することができる。データを復元するために、SDRAMサブシステムは、データをフラッシュ・メモリからSDRAMにコピーする。その途中で、復元されるデータを暗号化解除し、かつ/またはデータ完全性署名をチェックすることができる。

(もっと読む)

ディジタル装置

【課題】メモリへのライト動作中に電源遮断されても、確実にデータバス上のライトデータ全ビットをメモリに記憶させて、電源遮断によるメモリの2ビット以上のエラーを防ぐ。

【解決手段】電力受給側回路としてデータを記憶するメモリ手段と、メモリ手段に対しライト及びリードを行うメモリ制御手段と、メモリ手段のビットエラーの訂正及び検出をするECC手段を備え、電力供給側回路として主電源遮断を検知しリセット信号を与える監視手段と、メモリ手段に対して主電源が遮断してもバックアップ補助電源に切換えて電力供給する電源切換手段とを有し、監視手段のリセット信号によるメモリ手段とメモリ制御手段とECC手段のリセット操作は、メモリ手段のライト終了後に実施する。

(もっと読む)

不揮発性記憶装置、アクセス装置及び不揮発性記憶システム

【課題】電源遮断時の書き込みモードとは別に、高速なデータ書き込みを実現するための書き込みモードを持ち、コンテンツデータの書き込み時間を短縮することができる不揮発性記憶装置を提供する。

【解決手段】メモリコントローラ103は、不揮発性メモリ104の物理ブロックに対するデータの書き込み及び読み出しを制御する読み出し/書き込み制御部110と、書き込み中の電源遮断に対してデータを保護する第1の書き込みモードと、第1の書き込みモードより高速にデータを書き込む第2の書き込みモードとのうち一方の書き込みモードを格納するための書き込みモードテーブル108と、アクセス装置100から受信した書き込みモードを書き込みモードテーブル108に設定する設定部とを備え、読み出し/書き込み制御部110は、書き込みモードテーブル108に設定された書き込みモードに基づいてデータの書き込みを行う。

(もっと読む)

記憶装置と半導体不揮発性メモリの記憶方法

【課題】不揮発性メモリのランダムライトアクセスの高速化を図る。

【解決手段】半導体不揮発性メモリは、複数の消去単位からなる初期割当領域及び初期未使用領域を有する。ホスト側論理アドレスが順次に並ぶ最小管理単位を設定し、入力されたデータをバッファに順次に書き込み、最小管理単位毎の論理アドレスと不揮発性メモリの物理アドレスとのアドレスの変換情報を生成する。バッファの全記憶容量に対して書き込まれたデータを、書き込み予定の第1の消去単位の未書き込み領域に順次に書き込む。第1の消去単位の未書込領域がなくなると、検索された第2の消去単位の有効データを予め準備されている消去済等の第3の消去単位に書き込んで変換情報を更新して新第1の消去単位に置き換える。第2の消去単位を一括消去して新第3の消去単位の生成準備と並行して新第2の消去単位を検索する。

(もっと読む)

車載機器用データ記録システム

【課題】 車両のバッテリ交換時に車載システムの電源系統が遮断される場合に、揮発性メモリに記録していた車載機器のデータを不揮発性メモリに書き換えるとき、不揮発性メモリへの書き換え回数を減少する「車載機器用データ記録システム」とする。

【解決手段】車両の現在位置を検出し、予め設定した車両のバッテリ交換場所近傍を走行していることを検出したとき、車載機器のデータを記憶している揮発性メモリのデータを不揮発性メモリに書き換える。その際、バッテリ交換場所近傍を走行していることを検出したときに、予め車載機器の揮発性メモリに記録しているデータの内不揮発性メモリに書き換えるデータを収集しておき、実際にバッテリ交換を行う操作信号を検出したときに、収集しておいたデータを不揮発性メモリに書き換えるようにする。また、その書き換え処理状態やバッテリ交換の操作状態等の種々の案内を行う。

(もっと読む)

電力損失を制御するための方法及びデバイス

【課題】不揮発性メモリを有するデバイスにおける電力損失を制御するための方法及び装置を提供すること。

【解決手段】電力損失を制御するための方法及びデバイスがここに説明される。1つの実施形態において、この方法は、コントローラにより制御された電力遮断コマンドを出すことを含む。この方法は、メモリデバイスがバックグラウンド動作を実行しているかどうかを判断することを含む。この方法は、メモリデバイスがバックグラウンド動作を実行している場合に、バックグラウンド動作を安全に一時停止すること、又は、バックグラウンド動作を完了することを含む。この方法は、供給電力を安全に除去することを含む。

(もっと読む)

記憶装置システムの論理ブロックアドレス割り当て解除管理およびデータハードニング

【解決手段】 記憶装置システムの論理ブロックアドレス(LBA)割り当て解除管理およびデータハードニングを行うことにより、当該システムの性能、効率、および実用性が改善される。選択的に、(例えば、第1のプロトコルに関連付けられた)第1のフォーマット形式のLBA割り当て解除情報は、(例えば、第2のプロトコルに関連付けられた)第2のフォーマット形式に変換される。前記第1のプロトコルの一例はスモール・コンピュータ・システム・インターフェース(SCSI)プロトコルであり、前記第2のプロトコルの一例はアドバンスド・テクノロジー・アタッチメント(ATA)プロトコルである。選択的にLBA割り当て解除ステータス情報はソリッドステートディスク(SSD)などの記憶装置により決定され、イニシエータ、エクスパンダ、またはブリッジなど別の装置に通信される。選択的にSSDに格納されたデータは、例えばSSDの電源がオフになるという決定に応答してハードニングされる。このハードニングは、スーパーキャパシタまたは電池などのエネルギー貯蔵要素から供給される電力により行われる。

(もっと読む)

不揮発メモリ装置、不揮発メモリの書込み方法、及び不揮発メモリ書込みプログラム

【課題】不揮発メモリの書込みエラーが発生しても、トータルの処理時間を変えずに、書込み処理を完了させることができるようにする。

【解決手段】共通のデータバス及びアドレスバスに、特性の異なる第1の不揮発メモリ(MLC−NANDメモリ)102と第2の不揮発性メモリ素子(SLC−NANDメモし)103が接続されている。二重化書込み回路106は、CPU101からの二重化信号(イネーブル信号)に基づいて、第1の不揮発メモリ102と第2の不揮発性メモリ素子103を同時に選択し、第1の不揮発メモリ102へデータを書込むときに、第2の不揮発性メモリ素子103へ二重化したデータを書込む。

(もっと読む)

不揮発性メモリを主記憶に用いた装置

【課題】主記憶が全て不揮発性メモリで構成された場合において、突発的な電源の遮断が発生すると電源再投入時にシステムが正常に動作を再開できない。

【解決手段】装置は、電源異常遮断判定部と、電源異常終了通知レジスタとを備え、電源異常遮断判定部は、装置の電源投入時に、電源異常終了通知レジスタを参照し、電源異常終了通知レジスタが装置の電源が異常に遮断されたことを示す情報を格納しており、プロセッサが不揮発性のプロセッサでない場合、装置の電源が遮断される前に実行されていたプロセスを再起動し、デバイスドライバを確認し、電源異常終了通知レジスタが装置の電源が異常に遮断されたことを示す情報を格納しており、プロセッサが不揮発性のプロセッサである場合、装置の電源が遮断される前に実行されていたプロセスを、プロセスが中断された処理から再開し、デバイスドライバを確認することを特徴とする。

(もっと読む)

メモリシステム

【課題】多値のメモリセルを使用したNAND型フラッシュメモリの書き込み回数を低減して、その寿命が短くなることを抑制することができるメモリシステムを提供すること。

【解決手段】管理情報保存部154は、スタンバイ、スリープ、またはリセット信号を受けた場合に、スナップショットを取り直して指示状態へ移行する場合(図12(b))と、取り直さないで指示状態へ移行する場合(図12(a))との選択が可能な構成とする。

(もっと読む)

画像処理装置、メモリ保護方法、プログラム、及び記録媒体

【課題】確実にメモリを保護することができる画像処理装置、メモリ保護方法、プログラム、及び記録媒体を提供する。

【解決手段】メモリへのデータの書き込み中に、主電源スイッチへの手の接近を検知するセンサが手の接近を検知すると、メモリへのデータの書き込みを中止することにより、データの書き込み中の主電源スイッチのOFFによるデータ及びメモリの破壊が確実に防止される。すなわち、主電源スイッチをOFFすることができてしまうが、主電源スイッチをOFFしたときにはすでにメモリへの書き込みを終了しているため、問題が発生しない。

(もっと読む)

情報処理装置及びプログラム

【課題】電源オフ時に揮発メモリから不揮発メモリへより多くのデータを退避させることのできる情報処理装置を提供する。

【解決手段】電源電圧が、瞬断判別閾値以下のとき瞬断検知信号PSを出力する瞬断検知回路40を設ける。プロセッサ11は、瞬断検知信号PSを検知したとき、システムメモリ14から不揮発メモリ16へのデータ退避を開始し、瞬断検知信号が出力されてから所定時間の経過後にも瞬断検知信号が出力されている場合は、データ退避を継続すると共に、装置のシャットダウン処理を行なう。

(もっと読む)

半導体処理装置

【課題】カード引き抜きによる電源遮断による不都合を比較的容易に解消することができるカード型電子装置等の半導体処理装置を提供する。

【解決手段】半導体処理装置は、インタフェース制御回路(4)と処理回路(5)を有し外部装置例えばカードスロット(11)に装着されて動作電源の供給を受ける。前処理回路は電気的に消去及び書き込み可能な不揮発性メモリである。カード引き抜きによる電源遮断による不都合を解消するために、前記インタフェース制御回路は、カードスロットから引き抜かれるときカードスロットからの電源供給遮断前にカードスロットの所定の端子(P1)から分離する第1外部端子(H1)に生ずる電位変化を検出し、動作状態の処理回路に終了処理を指示する。上記より、電源供給が完全に遮断される前に半導体処理装置は自らで終了処理を行うことができる。

(もっと読む)

メモリシステムおよび情報処理装置

【課題】アクセス速度の高速化と高信頼性とを実現することができるメモリシステムおよび情報処理装置を提供する。

【解決手段】メモリシステム10におけるキャッシュメモリ20のキャッシュ方式を、領域によってライトスルー方式(ライトスルーキャッシュ領域WT)またはライトバック方式(ライトバックキャッシュ領域WB)に切り替えると共に、情報処理装置11の電源部15に入力される電源電圧の低下を検出したとき、動作可能なうちにライトバック方式に割り当てた領域のデータを不揮発性メモリ19に書き戻すよう制御する。

(もっと読む)

キャッシュデータ保護装置およびキャッシュデータ保護方法

【課題】異常シャットダウン動作発生時にキャッシュメモリ内のデータ消失を防止する。

【解決手段】本発明にかかるキャッシュデータ保護装置は、ホストシステム1および記憶装置4とともにコンピュータシステムまたはサーバー装置を構成し、ホストシステム1から受け取った記憶装置4への書き込みデータを一時的に格納しておくためのキャッシュメモリ23と、ホストシステム1および記憶装置4へ電源を供給する電源装置3と、記憶装置4への電源供給停止を許可するか否かの判断結果を電源装置3へ通知するマイクロコンピュータ21とを備え、電源装置3は、電源遮断要求をホストシステム1から受けた場合、その旨をマイクロコンピュータ21へ通知し、マイクロコンピュータ21は、キャッシュメモリ23内に記憶装置4へ未だ書き込まれていないデータが存在しなければ電源遮断許可を電源装置3へ通知する。

(もっと読む)

情報処理装置及びプログラム

【課題】電源オフ時に揮発メモリから不揮発メモリへより多くのデータを退避させることのできる情報処理装置を提供する。

【解決手段】電源電圧が、瞬断判別閾値以下のとき瞬断検知信号PSを出力し、電源電圧が瞬断判別閾値より低い停電判別閾値以下のとき停電検知信号PDを出力する瞬断/停電検知回路32を設ける。プロセッサ11は、瞬断検知信号PSを検知したとき、システムメモリ14から不揮発メモリ16へのデータ退避を開始し、その後、停電検知信号PDを検知した場合は、データ退避を継続すると共に、装置のシャットダウン処理を行なう。

(もっと読む)

電子制御装置の情報記憶方法

【課題】不揮発性メモリの記憶情報更新回数を増大させつつ、記憶情報の信頼性と、有効な情報の読み出し可能性を向上させることが可能な電子制御装置の情報記憶方法を提供する。

【解決手段】複数の記憶領域を設けた電気的に消去可能な不揮発性メモリを備える電子制御装置において、各記憶領域内にデータ格納部8と、各領域の情報の新旧を相対的に判定可能なカウンタ7と、有効性検証用のチェックデータを格納するチェックデータ部9とを設ける。電源投入時にはチェックデータ部9に基づく情報の有効性検証結果とカウンタ7の値に基づいて、前記複数の記憶領域のうち一つを選択し、当該記憶領域の情報を読み出して使用する。電源遮断時にはカウンタ7を増加させた上でチェックデータの値を算出し、データ領域全体を一括して更新する。

(もっと読む)

オンチップ不揮発性メモリ書き込みキャッシュを使用するシステムおよび方法

オンチップ書き込みキャッシュを用いて不揮発性メモリアレイをプログラムする方法を開示する。メモリシステムによって受信された個々のデータパケットはキャッシュメモリ内に記憶される。このようにして2つ以上のデータパケットを記憶し、次に、不揮発性アレイの単一ページにプログラムすることができる。この結果、不揮発性アレイ内の記憶空間の使用を効率良くする。  (もっと読む)

(もっと読む)

1 - 20 / 24

[ Back to top ]