Fターム[5B018MA05]の内容

記憶装置の信頼性向上技術 (13,264) | 対象 (1,668) | 制御メモリ(CM) (80)

Fターム[5B018MA05]に分類される特許

1 - 20 / 80

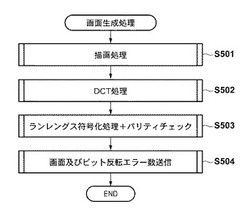

描画サーバ、センタサーバ、符号化装置、制御方法、符号化方法、及びプログラム

【課題】符号化処理を利用した効率的なメモリ検査を行う。

【解決手段】検査対象のメモリについてパリティ情報を付加したデータをメモリに書き込んだ後、該データをメモリから読み出してランレングス符号化処理を行って符号化データを生成する。符号化装置は、書き込まれたデータについてビット列を参照して符号化データを生成する際に、該ビット列と付加されているパリティ情報とを比較してビット反転エラーを検出する。

(もっと読む)

メモリー管理方法およびフィスカルプリンター

【課題】 信頼性を確保しつつ、冗長性の確保のためのコストを低減する。

【解決手段】 複数のメモリーに対してそれぞれ同一のフィスカル情報を順次書き込み、フィスカル情報の記録量が所定値に達した場合、複数のメモリーのうちの一つに記録された情報を消去し、情報を消去した前記メモリーのうちの一つに対してフィスカル情報の書き込みを続行する。

(もっと読む)

車両用電子制御装置

【課題】別の処理により使用されるメモリ領域に誤ってデータが書き込まれてしまう可能性を抑える。

【解決手段】電子制御装置が備えるCPUは、燃料噴射制御、点火制御及び電子スロットル制御処理を含む複数種類の制御処理を実行する。このCPUは、ベースレジスタが記憶する基準アドレスに、指定された相対アドレスを加算して実効アドレスを算出し、この実効アドレスに基づき、ストア命令及びロード命令に対応するRAMへのアクセスを行う構造を備える。各制御処理では、命令の発行時に、相対アドレスにより、アクセス先のメモリアドレスを指定する。また、各制御処理に対しては、異なる基準アドレスが割り当てられ、各制御処理の実行開始前には、ベースレジスタの値が、これから実行される制御処理に割り当てられた基準アドレスに更新される。この動作により、各制御処理に対しては、重複しない独立性の高いメモリ領域が割り当てられる。

(もっと読む)

車両用ドア駆動制御検査装置、車両用ドア駆動制御検査方法および車両用ドア駆動制御検査プログラム

【課題】簡易な装置にて異常個所をフィールドで特定することが可能な車両用ドア駆動制御検査装置を提供する。

【解決手段】書き込み指令手段202は、デュアルポートRAM101に接続されたCPU1、4に対してデュアルポートRAM101に対する書き込み指令を行い、読み出しデータ受信手段203は、CPU1、4にてデュアルポートRAM101から読み出された読み出しデータを受信し、故障診断手段204は、書き込み指令手段202にて指令された書き込みデータと、読み出しデータ受信手段203にて受信された読み出しデータとの比較結果に基づいて、デュアルポートRAM101の故障を診断する。

(もっと読む)

データ記憶装置及びテーブル管理方法

【課題】データ管理テーブルに対する整合性の確認処理を高速に行なことが可能なデータ記憶装置を提供することにある。

【解決手段】実施形態によれば、データ記憶装置は、第1の管理テーブルを格納する記憶デバイスと、第2の管理テーブルを格納する記憶デバイスと、カウンタテーブル格納モジュールと、コントローラとを具備する。前記第1の管理テーブルは、フラッシュメモリのデータの記録場所を示すアドレス情報を有する。前記第2の管理テーブルは、前記フラッシュメモリの記録データの中で有効なデータを示すアドレス情報を有する。前記カウンタテーブル格納モジュールは、有効なデータ数のカウント値をアドレス単位で示すカウンタテーブルを格納する。前記コントローラは、前記第1の管理テーブルを参照して取得されるアドレス単位の有効なデータ数と、前記カウンタテーブルのアドレス単位のカウント値とを比較し、当該比較結果に基づいて前記第1及び第2の管理テーブルの整合性を確認する整合性確認処理を実行する。

(もっと読む)

記憶装置、ホスト装置、回路基板、液体容器及びシステム

【課題】書き込み不要なデータを非書き込みとし、書き込み処理時間を短縮することができる記憶装置、ホスト装置、回路基板、液体容器及びシステム等を提供すること。

【解決手段】記憶装置100は、ホスト装置400との通信処理を行う制御部110と、ホスト装置400からのデータが書き込まれる記憶部120と、記憶部120のアクセス制御を行う記憶制御部130とを含む。制御部110は、ホスト装置400からコマンドパケット及びデータパケットを受信し、データパケットの書き込みイネーブルビットが書き込み許可状態に設定されている場合には、アドレス情報の更新指示を行うと共に、データパケットのデータの書き込み指示を行い、書き込みイネーブルビットが書き込み非許可状態に設定されている場合には、アドレス情報の更新指示を行う一方で、データパケットのデータの書き込み指示を行わない。

(もっと読む)

記憶装置、電子機器及び誤りデータの訂正方法

【課題】アドレス変換テーブルのエントリデータに誤り訂正符号を付与することなく、そのエントリデータに生じたビット異常の訂正を可能とする。

【解決手段】半導体記憶装置2は、論理アドレスに対応する物理アドレスへの変換にかかるアドレス変換テーブル31のエントリデータに付与された誤り検出符号をもとに、エントリデータに生じたビット異常を検出するアドレス変換テーブル異常検出部21と、ビット異常が検出されたエントリデータに含まれる所定のビットを反転させたデータが、正常なエントリデータであるか否かを検査するエントリデータ検査部22と、ビット異常が検出されたエントリデータを、検査された正常なエントリデータに置き換えるエントリデータ置換部23と、を備える。

(もっと読む)

シリアルパラレル変換システムの異常検出装置及び異常検出方法

【課題】シリアルパラレル変換システムにおけるシリアル信号の変換処理に影響を与えることなく短時間で確実にRAMの異常を検出する。

【解決手段】シリアル信号をパラレル信号に変換するシリアルパラレル変換回路101とRAM122の異常を検出する自己診断回路105と前記自己診断回路105で検出されたエラー情報が入力されるエラー制御部109とを備えたシリアルパラレル変換部100と、前記シリアルパラレル変換回路101で変換されたパラレル信号が書き込まれるRAM122とを有するシリアルパラレル変換システムの異常検出装置において、前記自己診断回路105は前記シリアルパラレル変換回路101におけるシリアルパラレル変換処理期間にRAM122の異常診断をおこなう。

(もっと読む)

プログラマブル論理回路のエラー訂正回路

【課題】コンフィギュレーションメモリのエラーの検出から修正、復旧までをプログラマブル論理回路に影響を与えることなくエラーを隠蔽した状態で動的に行うことが可能なプログラマブル論理回路のエラー訂正回路を提供する。

【解決手段】エラー訂正回路11は、プログラマブル論理回路の回路構成または配線構成を示す構成データおよびこの構成データの誤り検出符号化データが、ベースメモリMから読み出されて格納されるコンフィギュレーションメモリ12と、構成データと誤り検出符号化データとからエラー発生を検出するエラー検知部131、エラーが発生する前の構成データを保持する代替記憶部134、エラー通知により構成データを代替記憶部134が保持した構成データに切り替えるマルチプレクサ部133と、ベースメモリMから構成データを読み出し、コンフィギュレーションメモリ12に書き込み再構成する再構成制御部14とを備えた。

(もっと読む)

制御装置及びこれを備えた電子機器、認証処理装置

【課題】 制御データの安定性を担保して、安定的な動作制御の実現を可能にした制御装置を提供する。

【解決手段】 設定レジスタ13は、ドライバ4,5に対して行われる制御内容に対応したオリジナル制御データ7AをROM7から取得し、設定済制御データとして登録する。誤り検出検査符号作成回路15は、設定済制御データに基づき所定の規則に従って設定済誤り検出検査符号を作成する。比較回路16は、ノイズ検出回路14において設定レジスタ13の電源用電圧が所定の許可条件を逸脱する変動をした場合には、オリジナル制御データ7Aに基づいて前記所定の規則に従って作成されたオリジナル誤り検出検査符号7BをROM7から読み出し、前記設定済誤り検出検査符号との比較を行う。設定レジスタ13は、前記両符号に齟齬が存在すればオリジナル制御データ7Aを改めてROM7から取得して設定済制御データとして再登録する。

(もっと読む)

集積回路装置、電子機器

【課題】 回路規模の増加を抑えながら信頼性の高い故障検出を行う集積回路装置等を提供する。

【解決手段】 集積回路装置1であって、入力データ400が書き込まれる複数のブロック100、102を含む不揮発性メモリー10と、ブロックのそれぞれに対応付けられ、ブロックに書き込まれたデータ(メモリーデータ)のそれぞれが所与のタイミングで書き込まれる複数のレジスター20、22と、メモリーデータおよびレジスターに書き込まれたデータ(レジスターデータ)を受け取り、比較処理を行う比較部30とを含む。比較部30は、全てのメモリーデータが一致するか否か判定するための第1の比較処理と、複数のブロックの各ブロックについて当該ブロックのメモリーデータと当該ブロックに対応づけられたレジスターに書き込まれたレジスターデータとが一致するか否かを判定するための第2の比較処理を行う。

(もっと読む)

メモリ装置およびそのセルフチェック制御方法

【課題】メモリチェックで検出されるエラーが復旧不可能な故障であるかどうかを検出することができるメモリ装置およびそのセルフチェック制御方法を提供する。

【解決手段】2つのメモリ(101a、101b)にそれぞれ対応するエラー検出機能(102a、103a、102b、103b)が設けられた二重化メモリ部(100a、100b)と、二重化メモリ部のそれぞれのデータに対するエラー検出結果に基づいて、一方のメモリのデータでエラーが検出された場合に他方のメモリの対応したデータで修正するエラーチェック処理を各メモリの所定領域全体にわたって繰り返すセルフチェック部(110−112)と、エラーチェック処理を繰り返した際の異常判定回数CNT(X)が所定回数に達した時にデータ修正不可能と判定する判定部(110)と、を有する。

(もっと読む)

電子制御装置

【課題】データチェックによりエラーとなったメモリ領域に対して、不揮発性メモリの故障によるエラーなのか、電源の瞬断等により偶然生じたエラーなのか判別することが可能な電子制御装置を提供する。

【解決手段】中央演算処理装置10は、第2の不揮発性メモリ13の領域から制御データを読み出す場合、この制御データを読み出す領域の1つ前の領域のステータスデータを参照して、正常に記憶がされていないと判定したとき、1つ前の領域の故障履歴を参照して、故障の可能性があると判定したとき第2の不揮発性メモリ13が故障したと判定し、故障の可能性がないと判定したとき1つ前の領域の故障履歴に故障の可能性があることを書き込む。

(もっと読む)

データ書込装置、及び、データ書込方法

【課題】ユーザに制御結果を誤解させない学習制御の技術を提供する。

【解決手段】車両の電源から導かれる第1系統より電力の供給を受け、不揮発性の第1記憶部にデータを書き込むデータ書込装置は、書込要求に応答して、電源から導かれる第2系統より電力の供給を受け、データを記憶可能な第2記憶部に記憶された書き込みの対象データを、第1記憶部に書き込み、主電源からの電力供給が停止した後に開始する際は所定の初期表示を行う表示装置に、第1記憶部へのデータの書込結果を表示させ、第1記憶部に書込む際に、第1系統からの電力供給が停止された後に開始された場合は、第2記憶部に記憶された対象データを第1記憶部に書き込む第2書込手段は、書込要求を制御手段から受け付けたときに有効化し、書込要求をユーザから受け付けたときに有効化しない。このため、ユーザに制御結果を誤解させない学習制御を実現することができる。

(もっと読む)

記憶装置、基板、液体容器、システム及び記憶装置の制御方法

【課題】不揮発性の記憶部に記憶されたデータの破壊を抑止できる記憶装置、基板、液体容器、システム及び不揮発性の記憶部の制御方法等を提供すること。

【解決手段】記憶装置20は、不揮発性の記憶部60と、不揮発性の記憶部60を制御する制御部30と、を含む。制御部30は、電源異常状態を検出する検出回路32と、不揮発性の記憶部60に対する読み出し又は書き込みのアクセス制御を行い、検出回路32により電源異常状態が検出された場合に、不揮発性の記憶部60に対する読み出し又は書き込みのアクセス制御を停止するアクセス制御部36と、を有する。アクセス制御部36は、アクセスサイクルの開始後に検出回路32により電源異常状態が検出された場合には、そのアクセスサイクルにおける読み出し又は書き込みのアクセス制御については、停止せずに完了する。

(もっと読む)

情報記憶制御装置、電子機器、画像形成装置、プログラム

【課題】主制御部が正常に動作し得ない状態に陥っても情報退避処理を正常に行なうことができるようにする。

【解決手段】メインCPU212が電子機器の全体動作を制御する。メインCPU212が動作を制御するに当たって使用する情報をシステムメモリ222に記憶する。システムメモリ222とは別に情報退避用にブートメモリ224を用意する。情報退避処理を行なう機能部として、メインCPU212とは別に情報退避制御部260を設ける。メインCPU212の動作が正常であるか異常であるかを副監視部264で監視し、副監視部264がメインCPU212の異常な動作を検知したときには、情報退避処理部266は、システムメモリバス252と第1副データバス254の制御権をメインCPU212に解放させ、情報転送記憶部286を直接制御して、システムメモリ222の退避データ領域222aの情報をブートメモリ224に退避する。

(もっと読む)

コントローラ、及びデータ記憶装置

【課題】管理情報の保存中における性能の低下を防止できるコントローラ、データ記憶装置、及び復元方法を提供する。

【解決手段】揮発性の管理メモリ30は、フラッシュメモリ11の使用状態を管理する管理情報を記憶する。管理情報保存部53は、管理情報を複数の分割片に分割し、各分割片をフラッシュメモリに個別に保存する。主制御部32は、複数の分割片の保存中にホスト装置2から命令を受け付け、各分割片が保存される合間に命令に従ってフラッシュメモリに対するデータ処理を行い、管理情報をデータ処理の内容に応じて更新し、管理情報の更新内容を示すログを作成する。ログ保存部51はログをフラッシュメモリに保存する。復元部54は、フラッシュメモリに保存された複数の分割片を管理情報として管理メモリに読み出し、フラッシュメモリに保存されたログに従って管理情報を更新し、更新後の管理情報を復元する。

(もっと読む)

記憶装置、及び、ホスト回路に対し電気的に接続可能な記憶装置を含むシステム

【課題】記憶装置において、実データと誤り検出符号の読み出しと書き込みを効率化する。

【解決手段】記憶装置は、不揮発性のメモリーセルアレイと、Nビット(Nは2以上の所定の整数)のアクセス単位でメモリーセルアレイのデータ書き込みとデータ読み出しを実行するメモリー制御回路と、を備える。メモリーセルアレイは、書き換え可能領域と、読み出し専用領域と、を有する。書き換え可能領域は、アクセス単位を構成するNビットが実データと誤り検出符号の両方を含むように構成されている。読み出し専用領域は、アクセス単位を構成するNビットが実データのみを含む実データ領域と、アクセス単位を構成するNビットが誤り検出符号のみを含む誤り検出符号領域とに区分されている。

(もっと読む)

数値制御装置

【課題】故障診断プログラム自体にメモリエラーがある場合であっても、メイン処理の性能を低下させることなく短時間で主記憶装置の故障診断を行う簡易な構成の数値制御装置を得ること。

【解決手段】数値制御装置が、故障診断の対象となる領域として複数の故障診断領域を有した主記憶装置5と、故障診断を行う故障診断領域のデータを退避させおくECCテンポラリメモリ6Aと、故障診断領域の故障診断を行う故障診断部16と、主記憶装置5の故障診断を行う際に故障診断を行う故障診断領域のデータをECCテンポラリメモリ6Aにコピーして退避させる診断領域退避部15と、故障診断部16が主記憶装置5の故障診断を行なった後に、ECCテンポラリメモリ6Aに退避させておいた故障診断領域のデータを主記憶装置5に戻す診断領域復元部17と、を備える。

(もっと読む)

信号判定回路、集積回路装置及び電子機器

【課題】少なくとも4つ以上の信号線を介して受け取った信号の判定を行う、ロバスト性や冗長性を高めた信号判定回路を提供すること。

【解決手段】信号を判定する信号判定回路1は、少なくとも4つの信号線100を介して信号を受け取り、受け取った全信号のうち、信号同士が同じ値をとる信号数が半数を超えない場合にはエラー信号を出力するエラー信号生成回路10と、受け取った信号のいずれかの信号を選択し出力する出力選択回路30とを含む。

(もっと読む)

1 - 20 / 80

[ Back to top ]