Fターム[5B018NA08]の内容

記憶装置の信頼性向上技術 (13,264) | メモリの種類 (2,134) | ワンチップマイコン (19)

Fターム[5B018NA08]に分類される特許

1 - 19 / 19

半導体装置

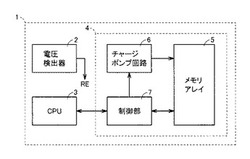

【課題】データの誤書換を防止することが可能な低消費電力の半導体装置を提供する。

【解決手段】マイクロコンピュータ1は、電源電圧VCCが正常範囲から外れた場合にリセット信号REを出力する電圧検出器2と、各々がデータを不揮発的に記憶する複数のメモリセルを含むメモリアレイ5と、イレーズコマンドまたはプログラムコマンドに応答して、電圧検出器2の応答時間TR以上の保留時間TSだけ経過した後にデータのイレーズまたはプログラムを実行し、リセット信号REに応答してリセットされる制御部7とを備える。したがって、電圧検出器2の応答時間TRが長い場合でも、データの誤書換を防止できる。

(もっと読む)

マイクロコンピュータ及び異常メモリアクセス検出方法

【課題】余計な命令コードを追加することなく、マイクロコンピュータにおける異常メモリアクセスの発生を検出すること。

【解決手段】メモリへのアクセス発生時、XOR処理器は、アクセス対象データのデータ幅に依存して異なる係数とアクセス対象データとのXOR演算を行う。パリティ生成回路は、XOR演算の演算結果に基づいて、アクセス対象データに関連するパリティビットを生成する。書き込みアクセス時、パリティ処理回路は、パリティ生成回路によって生成されたパリティビットをメモリに書き込む。読み出しアクセス時、パリティ処理回路は、パリティ生成回路によって生成されたパリティビットとメモリから読み出されるパリティビットとを比較し、それらが不一致である場合、割り込み信号をCPUに出力する。

(もっと読む)

情報処理装置

【課題】メモリにエラーが発生する度に装置の再起動を行うと平均故障間隔が短くなってしまうこと。

【解決手段】情報処理装置1は、メモリと、このメモリに接続されたマイクロプロセッサとを備える。マイクロプロセッサは、アプリケーションプログラムの実行中に上記メモリにエラーが発生したとき、上記エラーが発生したメモリ領域の使用用途が予め定められた使用用途か否かを判定し、上記エラーが発生したメモリ領域が上記予め定められた使用用途であれば、上記エラーが発生したメモリアドレスのメモリ領域を初期化して上記アプリケーションプログラムの実行を再開する、ようにプログラムされている。

(もっと読む)

不揮発性メモリの電源瞬断対応回路

【課題】小型・低コストのメリットを阻害することのない、マイコンと共通の電源電圧で動作する不揮発性メモリの電源瞬断対応回路であって、電源瞬断があっても確実なデータ保証が可能な不揮発性メモリの電源瞬断対応回路を提供する。

【解決手段】マイコン100のパワーオンリセット電圧VPORより上にある不揮発性メモリ94の動作保証電圧範囲VDD_MIN〜VDD_MAXにおいて、瞬断による電源電圧VDDの低下を検出し、瞬断検出信号を出力する瞬断発生検出回路40と、瞬断検出信号により、不揮発性メモリ94の書換え情報設定レジスタ94aにある書換え情報を該不揮発性メモリ94の外部で保持する書換え情報保持手段(ラッチレジスタ41)と、瞬断検出信号を保持する瞬断検出信号保持手段(瞬断検出フラグ42)とを有してなる電源瞬断対応回路とする。

(もっと読む)

データ処理用半導体装置

【課題】データ処理用半導体装置における不揮発性メモリの書き換え制御の信頼性を向上させる。

【解決手段】データ処理用半導体装置(1〜6)において、書き換え可能な不揮発性の記憶領域(11、91)のデータの読み出しとデータの書き込み及び消去とを制御する制御部(12、30、90、120、160)は、入力した温度のデータを参照して前記記憶領域のデータの読み出し可能な温度範囲よりもデータの書き込み及び消去を行う温度範囲を狭く制御する動作モードを有する。

(もっと読む)

マイクロプロセッサ及びモリ破損チェック方法

【課題】マイクロプロセッサに含まれるRAMの変数領域及びスタック領域の全領域の破損チェックを行い、破損が確認された場合は安全に復帰させる。

【解決手段】RAM12の変数領域とスタック領域を個別に破損チェックし、変数領域で破損が確認され、所定の処理ループの繰り返し回数が予め定められた回数以上になったとき、CPU11がI/O13を介して警告信号を外部に出力する。LED21がこの警告信号に応答して点灯する。スタック領域で破損が確認された場合は、スタック領域の内容が破壊されていることによるプログラムの暴走を防ぐために、直ちにリセット回路14がマイクロプロセッサ1のリセットを行う。

(もっと読む)

半導体装置及び電子機器

【課題】動作時間を短縮しつつ、半導体記憶装置のデータを修正する半導体装置及び電子機器を提供すること。

【解決手段】選択回路8は、CPU2及び誤り訂正回路5と、第1及び第2メモリMe1,Me2との間に配置される。選択回路8は、アドレスデータDaに基づいて、CPU2に指定された一方の第1又は第2メモリMe1,Me2に対応するメモリ書き込みデータDwmを第1又は第2メモリ書き込みデータDwm1,Dwm2として出力し、CPU2に指定されていない他方の第1又は第2メモリMe1,Me2に対応する訂正メモリデータDmtを第1又は第2メモリ書き込みデータDwm1,Dwm2として出力する。

(もっと読む)

データ書き込み装置及びプログラム

【課題】不正なデータが書き込まれた場合であってもデータの復旧を可能にする。

【解決手段】データ書き込み装置は、同一の書き込みデータを第1〜第3の記憶領域の夫々に所定の順序で書き込む書き込み部と、所定のタイミングで、第1〜第3の記憶領域に記憶されているデータの相互の異同を判定する異同判定部と、異同判定部の判定結果に基づいて、書き込みデータが正常に書き込まれていない第1〜第3の記憶領域のうちの少なくとも1つの記憶領域に、書き込みデータが正常に書き込まれている第1〜第3の記憶領域のうちの少なくとも1つの記憶領域に記憶されているデータを書き込むデータ復旧部と、を備える。

(もっと読む)

マイコン装置

【課題】電源電圧が基準電圧よりも低下したときに、揮発性メモリ内のデータを不揮発性メモリに速やかに退避できるマイコン装置を提供する。

【解決手段】CPU7と揮発性メモリ9と不揮発性メモリ11とがバス接続されてなるマイコン装置1Bにおいて、電源電圧Vddと第1基準電圧Vref1とを比較し、電源電圧Vddが第1基準電圧Vref1よりも低下した時に割込要求信号を出力する第1コンパレータ3と、電源電圧Vddと第2基準電圧Vref2とを比較し、電源電圧Vddが第2基準電圧Vref2よりも低下した時に割込要求信号を出力する第2コンパレータ4と、第1コンパレータ3からの前記割込要求信号と第2コンパレータ4からの前記割込要求信号に応じて起動し、バス13経由で揮発性メモリ9内のデータを不揮発性メモリ11に転送するDMA転送手段5とを備える。

(もっと読む)

マイクロコンピュータ

【課題】 マイクロコンピュータにおいてプログラムメモリとして使用される強誘電体メモリの寿命延長を使用効率の低下を伴うことなく実現する。

【解決手段】 分岐命令検出部は、CPUによりメモリから取得される命令コードと所定の分岐命令の命令コードとの一致を検出する。命令情報格納部は、分岐命令検出部により命令コードの一致が検出された場合、所定の分岐命令とそれに続いて実行される命令とに関して、CPUにより指定されるアドレスとCPUによりメモリから取得される命令コードとを格納する。アドレス比較部は、CPUにより指定されるアドレスと命令情報格納部に格納されているアドレスとの一致を検出する。メモリアクセス制御部は、アドレス比較部によりアドレスの一致が検出された場合、CPUによるメモリからの命令コードの取得を禁止し、CPUに命令情報格納部から命令コードを取得させる。

(もっと読む)

情報処理装置

【課題】消去又は書き換えられる不揮発性メモリのブロックに偏りを発生させない。

【解決手段】書き込み制御回路6には、カウンタ制御回路61とアドレス制御回路62が

設けられ、アドレス情報を入力し、CPU1からコマンド情報を入力する。カウンタ制御

回路61は、アドレス情報信号S23をアドレス情報格納ブロック21に出力し、カウン

ト情報信号S22をカウンタ情報格納ブロック22に出力し、アドレス情報格納ブロック

21から情報伝達信号S25と、カウント情報格納ブロック22から情報伝達信号S24

とを入力する。アドレス制御回路62は、カウンタ制御回路61から出力される情報伝達

信号S26を入力し、書き込み制御信号S21をフラッシュメモリ2に出力する。書き込

み制御信号S21により、フラッシュメモリ内蔵マイクロコンピュータ30にアクセスさ

れるフラッシュメモリ2のブロックに偏りが発生しないように情報が書き込まれる。

(もっと読む)

メモリ信頼性を向上させるシステム及び方法

【課題】メモリ信頼性を向上させるシステムを提供する。

【解決手段】メモリ・セルが動作する電圧とメモリ・セルをアクセスする論理回路素子が動作する電圧との間の相対的な変動から生じる不安定性と書込み性問題を減少させるシステムは、電圧が許容可能な動作範囲内にないときにメモリ・アクセスを禁止する。第1の電圧で電力を受ける論理回路素子を有するパイプライン方式のプロセッサ及び第2の電圧で電力を受けるSRAMセルのセットを備える。クリティカル状態検出器は、第1の電圧と第2の電圧をモニタするように、かつこれらの電圧の比が許容可能な範囲内であるかどうかを決定するように設定される。電圧が許容可能な範囲内にないときに例外が発生され、例外ハンドラは、SRAMセルへのアクセスを禁止するためにプロセッサ・パイプラインをストールする。電圧が許容可能な範囲に戻ると、パイプラインをレジュームし、例外の取り扱いを終了する。

(もっと読む)

クロック速度のマルチポートのメモリアレイのテスト方法および装置

2つまたはそれ以上の書き込みポートを介してアレイにデータを同時に書き込むこと、および/または2つまたはそれ以上の読み出しポートを介してアレイからデータを同時に読み出すことによる「内蔵自己テスト」(BIST)コントローラによって、マルチポートのメモリアレイがプロセッサの動作周波数でテストされる。アレイから読み出されたデータとアレイに書き込まれたデータとの比較は、直列的に実施されてもよいし、並列的に実施されてもよい。比較回路は、プロセッサの通常の動作の間、効果的に動作不能にされる。マルチポートを介したデータの書き込みおよび/または読み出しを同時に行うことによって、従来のテスト方法に比べて、潜んでいた電気的マージナリティをあらわにすることができ、テスト時間を減縮することができる。  (もっと読む)

(もっと読む)

独立してアドレス可能な副単位を有するデータ記憶装置用のデータステアリングロジックをテストするための方法および装置

メモリアレーのI/O内の読取および書込データステアリングロジックは、メモリアレー記憶場所の各アドレス可能な副単位にデータバスレーンを提供することによって、テストされる。各バスレーンは、比較器のデータインプットに接続される。BISTコントローラは、書込ステアリングロジックをテストするために、書込ステアリングロジックを介してメモリにテストパターンを書き込み、並列にテストパターンを読み取る。BISTコントローラは、読取ステアリングロジックをテストするために、並列にメモリにテストパターンを書き込み、読取ステアリングロジックを介してテストパターンを読み取る。いずれの場合も、各バスレーン専用の個別の比較器は、副単位データがデータバスレーンとメモリの記憶装置の副単位の間で適切に偏移されたことを検証する。比較器は、ロジックゲートの切り換えを防ぐために、通常の動作の間、効果的に動作不可能にされる。  (もっと読む)

(もっと読む)

フラッシュEEPROMのデータ正否判定方法

【課題】データ検証領域の先頭位置および末尾位置に同一内容の識別情報を格納することにより、識別情報間に挟まれたデータ空間内のデータの正否を判定可能とする。

【解決手段】まず、データ検証領域の先頭位置の先頭識別情報が期待値であるかどうかを判定する(ステップS1)。先頭識別情報が期待値であれば、データ検証領域の末尾位置の末尾識別情報が期待値であるかどうかを判定する(ステップS2)。末尾識別情報も期待値であれば、先頭識別情報と末尾識別情報とが同一内容であるかどうかを判定する(ステップS3)。先頭識別情報と末尾識別情報とが同一内容であれば、先頭識別情報と末尾識別情報とに挟まれたデータ空間内のデータが正しいと判定する(ステップS4)。それ以外の場合には、先頭識別情報と末尾識別情報とに挟まれたデータ空間内のデータが正しくないと判定する(ステップS5)。

(もっと読む)

マイクロコンピュータ

【課題】 メモリデバイスのアドレスデコーダを対象とする静止状態電源電流測定に要する時間を短縮することができるマイクロコンピュータを提供する。

【解決手段】 マイコンに搭載される4つのROM3A〜3Dを選択するためのアドレスデコーダ11は、IDDQテスト信号が与えられると、測定用のテストパターンとして与えられるアドレスがLSB側の16ビットに亘り連続する領域については、その領域に対応するROM3A〜3Dを同時に選択するようにデコード信号を出力する。

(もっと読む)

マージバッファのシステムキルエラーのプロセスキルエラーへの変換技術

【課題】 本発明の課題は、上記問題点に鑑み、マージバッファのシステムキルエラーをプロセスキルエラーに変換する方法、装置及びシステムを提供することである。

【解決手段】 上記課題を解決するため、本発明は、データ及び該データが格納されるアドレスを有し、1以上のプロセスに係るストア命令を収集するバッファと、第1プロセスに係るストア命令を、前記バッファが第2プロセスに係るストア命令を収集する前に前記バッファから常にドレイン処理するバッファ制御とから構成されることを特徴とする装置を提供する。

(もっと読む)

フラッシュメモリマイクロコンピュータのデータ保全方法および保全装置

【課題】 本発明は、マイクロコンピュータ内のフラッシュメモリに記憶させたプログラムに消滅等のデータ異常が発生した場合であっても、制御を可能にするためのフラッシュメモリマイクロコンピュータのデータ保全方法および保全装置に関するものである。

【解決手段】 マイクロコンピュータは、起動する際に、誤り訂正符号を基にして、フラッシュROMデータのサムチェックを行う。前記マイクロコンピュータは、前記サムチェックを行って一致しない場合、誤り制御プログラムを起動する。前記誤り制御プログラムは、前記フラッシュROMデータの異常箇所を割り出し、前記異常箇所を正常データに書き換える。前記フラッシュROMにおける全エリアのデータは、一旦、データが消滅または異常が発生しても、正常に書き換えられ、正しい制御が可能になる。

(もっと読む)

ブロッキングなく、キャッシュ参照間に直面するビットエラーを修正する方法および装置

本発明のある実施形態は、キャッシュメモリへの参照の間に直面するビットエラーを修正するシステムを提供する。アプリケーションの実行の間に、システムは、データアイテムおよび関連するエラー訂正コードをキャッシュメモリから取り出すことによって、キャッシュメモリへの参照を実行する。次に、システムは、エラー訂正コードを取り出されたデータアイテムから計算し、計算されたエラー訂正コード関連するエラー訂正コードと比較する。計算されたエラー訂正コードが関連するエラー訂正コードと整合しない場合、ビットエラーが生じる。この場合、システムは、ビットエラーが後の時間に修正され得るように、キャッシュメモリと関連する1つ以上のレジスタのセット内のあるレジスタに参照の識別子を格納する。このシステムはまた、アプリケーションが実行し続けることを可能にする。  (もっと読む)

(もっと読む)

1 - 19 / 19

[ Back to top ]