Fターム[5B045BB16]の内容

マルチプロセッサ (2,696) | 通信、転送方式 (1,368) | 系路の接続、切替方式 (844) | スイッチによるもの (138) | マトリックススイッチによるもの (36)

Fターム[5B045BB16]に分類される特許

1 - 20 / 36

データ転送システム、スイッチ及びデータ転送方法プロセッサ間ネットワーク

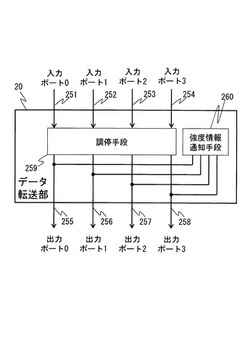

【課題】プロセッサ間で転送するパケットの転送時間の偏りを低減することができるデータ転送システム、スイッチ及びデータ転送方法を提供すること。

【解決手段】本発明にかかるデータ転送システムは、複数のプロセッサと、複数のプロセッサに含まれる一のプロセッサから他のプロセッサに対するデータ転送を複数の入力及び出力ポートを介して実行する複数のデータ転送部20を備える。データ転送部20は、次の転送先が同じ競合データについて調停を実行する調停手段259と、調停を行った競合データの競合数を示す強度情報を次の転送先に送信する強度情報通知手段260を有する。調停手段259は、調停を実行する場合には、複数の入力ポートの中でそれぞれの入力ポートを選択し、その入力ポートから競合データを入力する割合を示す選択割合を、各入力ポートから受信した強度情報が示す競合数の多さに関する入力ポート間の割合に応じて決定する。

(もっと読む)

並列計算機、計算機、通信方法およびプログラム

【課題】並列計算機において、全対全通信にかかる処理を効率化する。

【解決手段】相互結合網は、マルチキャストパケットを受信すると該パケットを該パケットが指定した送信先に送信する。複数の計算機は、計算機数未満の数のグループにグルーピングされ、計算機は、全対全通信時にグループ単位でグループ内の計算機に送信される特定データと、特定データのパケットへの搭載箇所をグループ単位で示す第1情報と、自計算機宛のデータがパケットに搭載された箇所を示す第2情報を記憶する記憶手段と、全対全通信時にグループ単位で特定データが第1情報の示す箇所に搭載され該グループを送信先としたマルチキャストパケットを生成し相互結合網に送信する送信手段と、マルチキャストパケットを受信すると第2情報を参照して該パケットから自計算機宛のデータを抽出する抽出手段を含む。

(もっと読む)

ネットワークシステム、情報処理装置及びネットワークシステムの制御方法

【課題】ネットワークシステム、情報処理装置及びネットワークシステムの制御方法において、レイテンシ及びバンド幅の両方を向上可能とすることを目的とする。

【解決手段】クロスバスイッチと、前記クロスバスイッチに接続されたポートを有する複数のクロスバインタフェースと、前記複数のクロスバインタフェースのうち、使用頻度が所定値以上のポートの組を形成するクロスバインタフェース同士を直接接続するバイパスルートを備えるようにする。

(もっと読む)

ルーティングテーブルの書き換え方法、データ転送装置およびプログラム

【課題】 ルーティングテーブルを書き換える書き換えデータの発行元ノードのパーティション以外に書き換えの影響が及ばないようにすることが課題である。

【解決手段】 書き換えデータの発行元ノードが属するパーティションを認識できず書き換えデータに含まれるポートがルーティングテーブルに登録済みか書き換えデータに含まれるパーティションがルーティングテーブルに登録済みなら書き換えを許可しないが、発行元ノードが属するパーティションを認識できず書き換えデータに含まれるポートも書き換えデータに含まれるパーティションもルーティングテーブルに登録されておらず発行元ノードが書き換え対象のデータに含まれるノードと一致するなら書き換えを許可する構成である。

(もっと読む)

ヘテロジニアスマルチコアプロセッサ

【課題】プロセッサコアとプロセッサエレメント間におけるデータ授受のためのオーバーヘッドを短縮するとともに、演算能力の向上させる。

【解決手段】プロセッサエレメント13は、各プロセッサコア2−A,2−B,2−Cからキャッシュ禁止に設定され、プロセッサコアおよび入出力インタフェース回路11から直接アクセス可能に設定され、入出力インタフェース回路11からメインメモリ17を介さずに直接転送された入力データおよびプロセッサエレメントの演算結果である出力データを格納するローカルメモリ14と、ローカルメモリ14とメインメモリ17との間でDMA転送するDMAC15とを備え、プロセッサエレメントは出力データをメインメモリ17へDMA転送後に転送完了の割り込みをプロセッサコアに通知し、プロセッサコアはこの通知に基づき次の処理を実行する。

(もっと読む)

マルチプロセッサシステム、ノードコントローラ、障害回復方式

【課題】ノードコントローラの障害によるシステム停止時間を短縮することが可能なマルチプロセッサシステムを提供することにある。

【解決手段】第一ノードコントローラと第二ノードコントローラは、リクエストに含まれるアクセス先のメモリアドレスに基づいて、リクエストの送信先の識別子を決定する第一、及び第二リクエスト制御部と、第一リクエスト制御部へリクエストを出力すべきリクエストの送信先の識別子を記憶する第一レジスタと、第二リクエスト制御部へリクエストを出力すべきリクエストの送信先の識別子を記憶する第二レジスタと、リクエストを受信すると、リクエストの送信先の識別子と、第一、及び第二レジスタに設定された識別子に基づいて、第一、第二リクエスト制御部のいずれかにリクエストの出力先を決定する第一ルーティングテーブルと、第一、第二リクエスト制御部の決定した送信先の識別子に基づいて、送信先の識別子に対応する信号線を選択して、リクエストを送信する第二ルーティングテーブルと、を備える。

(もっと読む)

マルチノードコンピュータシステム及びノード間接続装置

【課題】マルチノードコンピュータシステムにおける障害発生ノードの切り離し処理において、正常な運用ノードへの影響を抑えること。

【解決手段】マルチノードコンピュータシステムは、複数のノードと、ノード間のデータ転送を制御するノード間接続装置とを備える。各ノードは、障害が発生した場合に、切り離し要求コードをノード間接続装置へ送信する。ノード間接続装置は、コード検出手段と、変換手段とを備える。コード検出手段は、障害発生ノードから送信された切り離し要求コードを検出する。変換手段は、切り離し要求コードの検出後に送信元ノードから受け取る障害発生ノードへの命令を、その送信元ノードへの応答に変換する。

(もっと読む)

マルチノードシステム、異常処理方法、スイッチ、ノード及びプログラム

【課題】マルチノードシステム全体として統一されたステータスを認識することができるマルチノードシステム、異常処理方法、スイッチ、ノード及びプログラムを提供すること

【解決手段】本発明にかかるマルチノードシステムは、複数のノード2、3と、複数のノード2,3に含まれる任意のノード間でデータ転送用パス7を介してデータを転送するスイッチ1と、スイッチ1の異常を検出した場合に、検出した異常を通知する異常通知をデータ転送用パス7に出力するとともに、データ転送用パス7とは異なる診断用パス8に出力するスイッチ診断装置4と、異常通知をデータ転送用パス7もしくは診断用パス8から取得するノード診断装置5、6を備える。

(もっと読む)

コンピュータシステム

【課題】コンピュータシステムを構成するCPUや記憶装置などを異なる物理パーティションに割り当て、限られたリソースを効率良く利用する。

【解決手段】ネットワークを介して相互に接続されるCPUと記憶装置が複数の物理パーティションに割り当てられ得るシステムにおいて、CPUとネットワークの間に、物理パーティションの分割を制御するパーティション制御装置を配置する。パーティション制御装置は、CPU又は記憶装置が何れの物理パーティションに属するかを管理するパーティション番号マッピングテーブルと、CPUからのメモリアクセス要求に含まれるシステムアドレスをデコードして、要求中のシステムアドレスがアドレッシングされている記憶装置を特定するアドレスデコーダと、要求元を示す情報にパーティション制御装置を識別するIDを関係付け、システムアドレスを記憶装置内のアドレスに変換するメモリアクセス要求変換部とを有する。

(もっと読む)

欠陥誤り耐性機能付きクロスバーバス回路

【課題】クロスバーバス回路内に欠陥が生じるか、あるいは使用している間に故障が生じても、故障を回避することを可能にする。

【解決手段】バス間を接続する複数のトランジスタスイッチとを有し、データ伝送先部へのデータ転送を一対一に行うことのできるクロスバーバス10と、データに判定ビットを付加して、クロスバーバスに送る判定ビット付加装置6と、データ転送の結果が成功したか否かの判定を行う転送結果判定装置15と、データを保持するデータ保持装置17と、再転送要求を出力し、データ保持部に保持されているデータをデータ伝送先部に送出させる再転送判定装置19と、クロスバーバス内の転送経路を選択するとともにこの選択されたトランジスタスイッチの状態をメモリに記憶させ、転送経路に含まれるトランジスタスイッチをオンさせる選択信号を出力する転送経路選択回路11と、を備えている。

(もっと読む)

プロセッサアーキテクチャ

【目的】プロセッサアーキテクチャにおける電力消費を削減すること。

【解決手段】 以下のものを含むプロセッサアーキテクチャが提供される:少なくとも1つの入力ポートと少なくとも1つの出力ポートを持ち、各ポートは少なくともデータバスと有効データ信号線を持つ複数の処理要素と;ある時間間隔で、いずれかの第1の処理要素の出力ポートといずれかの第2の処理要素の入力ポートとが接続されるように配置された複数のスイッチを含むバス構造。各処理要素は、関連するデータバスが転送値を含む時には、有効なデータ信号線上の値を第1の論理状態に設定し、データバスが転送値を含まないときには第2の論理状態に設定することができ、各処理要素は更に、関連する入力ポートの有効なデータ信号線上の値が第2の論理状態にある時に、所定の時間間隔で待ち状態に入ることができる。

(もっと読む)

データ処理装置のための相互接続論理

【課題】相互接続論理に結合されたスレーブ論理ユニットによりトランザクションのリオーダを制御する装置と方法。

【解決手段】複数のマスタ論理ユニットと複数のスレーブ論理ユニットを相互接続する相互接続論理において、トランザクションの少なくとも1つのサブセットについて、IDエイリアシング論理が所定の識別子によりトランザクション識別子を置換えてから、スレーブ論理ユニットへアドレス転送を回送する。スレーブ論理ユニットからの応答転送のためには、IDエイリアシング論理が、除去済みの元のトランザクション識別子により所定の識別子を置換えてから、適当なマスタ論理ユニットへ返送する。相互接続論理内のデッドロックの発生を減少させる単純で効果的な機構である。

(もっと読む)

クロスバーのストールした出力キューの情報をクリアするためのシステム及び方法

【課題】クロスバーのストールした出力キューの情報をクリアするためのシステム及び方法を提供する。

【解決手段】各時限ポート204は、入力キュー302、出力キュー304、及びキュータイマ306を備える。入力キュー302及び出力キュー304は、1つ又は複数の情報キュー308、312をそれぞれ備える。各情報キュー308、312は、単一の情報を記憶するように構成されている。 情報キュー308、312は直列に接続されて、1つの情報が情報キュー308、312の最初のものに到着するようにされている。その後、この1つの情報は、直列に又は順次、情報キュー308、312の最後のものへ伝播される。この1つの情報が出口キューに存在している時、次に、その情報をそのキューに結合された出力接続部上へ通信することができる。

(もっと読む)

共有メモリ装置

【課題】メモリまでの配線を簡単化でき、面積増加と長距離配線による性能低下を防止でき、メモリアクセスの高速化を図ることができる共有メモリ装置を提供する。

【解決手段】処理モジュール21の入出力ポート211と、各メモリインタフェース222,232と、各メモリバンク221−1〜221−n,231−1〜231−nとは、複数のメモリマクロ221,231の配置領域(の上層)にY方向(第1方向)およびX方向(第2方向)にマトリクス状(格子状)に配線された接続配線により接続されている。接続配線は、指示情報配線(コマンドアドレス配線)とデータ配線(ライト配線とリード配線、あるいは共用配線)が多層配線される。

(もっと読む)

共有メモリ装置

【課題】メモリまでの配線を簡単化でき、面積増加と長距離配線による性能低下を防止でき、システムのスケーラビリティーの拡張性を向上できる共有メモリ装置を提供する。

【解決手段】各メモリシステム11−1〜11−nは、データを記憶するたとえばDRAM等のメモリマクロ12、並びに、メモリマクロ12のアクセスを行って所定のデータ処理を行うプロセッサ13を含み、メモリマクロ12は、データ転送が可能なメモリインタフェース15を少なくとも一つ有し、少なくともメモリセルおよびメモリインタフェースを含む領域が2次元的な高さを揃えて並列に配置され、異なるメモリシステムの2次元的な高さを揃えたメモリマクロのメモリインタフェース同士が接続されている。

(もっと読む)

非均一クロスバースイッチプレーントポロジのためのシステム及び方法

【課題】非均一クロスバースイッチプレーントポロジを利用するシステム及び方法を提供する。

【解決手段】

本発明にかかるシステムは、対称型マルチプロセシング(SMP)システムであって、複数のプロセッサグループと、複数の経路を備える非均一クロスバースイッチプレーンシステムと、を備え、Nをプロセッサグループの個数に等しいとすると、前記プロセッサグループのそれぞれは、多くとも(N−1)個に等しい複数の経路によって他のプロセッサグループに通信接続されるようになる、SMPシステムである。

(もっと読む)

分散メモリ型マルチプロセッサシステムのシフト通信方法および分散メモリ型マルチプロセッサシステム

【課題】シフト通信を、対象配列・次元や方向が変化したり異なる手続きにまたがっていても、高速に行うことができる技術を提供する。

【解決手段】シフト通信を行う配列の分割配置方法を解析するステップと、その解析結果に基づいて、同一の分割配置に対するシフト通信スケジュールテーブル(7)が存在するかどうかを検索するステップと、前記同一の分割配置に対するシフト通信スケジュールテーブル(7)が存在する場合、必要な次元の必要な方向に対するシフト通信スケジュール(71〜7n)が既に生成されているかどうかを検索するステップと、生成されていないシフト通信スケジュール(71〜7n)が存在する場合、必要な分割配置方法、次元、方向に対応したシフト通信スケジュール(71〜7n)を新たに生成し、前記新たなシフト通信スケジュール(71〜7n)を含む新たなシフト通信スケジュールテーブル(7)を生成して、シフト通信を実行する。

(もっと読む)

マルチプロセッサシステムおよびメモリアクセス方法

【課題】本発明の目的は、入力ポート内の同一メモリのアクセス順序を守りながらクロスバ性能を向上させるマルチプロセッサシステムを提供することにある。

【解決手段】 複数の中央処理装置と複数の主記憶装置とを備えるマルチプロセッサシステムは、複数の出力部と、複数の入力ポートと、クロスバ部と、出力先情報比較部とを具備する。複数の出力部は、主記憶装置に内蔵されるメモリをアクセスする。複数の入力ポートは、中央処理装置と接続され、中央処理装置がメモリをアクセスするために発行するメモリアクセスリクエストを保持する複数の入力部を備える。クロスバ部は、メモリアクセスリクエストを複数の出力部のうち中央処理装置により指定される指定出力部に出力する。出力先情報比較部は、複数の入力ポートのうち第1入力ポートに保持されるメモリアクセスリクエストを、複数の入力ポートのうち未使用の入力部を有する第2入力ポートに移動させる。

(もっと読む)

情報処理システムとJOB実行方法

【課題】マルチノードJOBの高速実行を可能とするシステム及び方法の提供。

【解決手段】ノードは、CPU11と転送制御部12を有し、リクエスト元ノードの転送制御部がCPUから発行されたMPI専用命令を受け取り、専用命令待合せバッファ13に情報を格納し、クロスバースイッチ20に対して、マスク情報を通知し、クロスバースイッチではデータ通知フラグレジスタ22にマスク情報を設定し、ブロードキャスト通信により、全ノードに対して演算実行指示を通知し、演算実行する全てのノード間の演算が終了すると、通知終了部26は演算結果を、全ノードにブロードキャスト通知し、各ノードでは、返却データJID比較部18で要求した演算結果に対応するものであるかチェックし、要求したデータの場合にはCPUに返却し、そうでない場合には受け取った演算結果を廃棄する。

(もっと読む)

マルチプロセッサシステム装置

【課題】コンパイラが容易に静的スケジューリングを行うことができ、一般的な同時アクセスパターンに対して無衝突なパケット転送を実現することができるマルチプロセッサシステム装置を得る。

【解決手段】各プロセッサエレメント間を、階層構造の多段結合網で接続し、該多段結合網を構成する各スイッチエレメントに対して、あらかじめコンパイラによって静的にスケジューリングを行い、階層構造の多段結合網を無衝突でエミュレーションするようにした。更に、階層構造の多段結合網の基本網にクロス網を使用して1つのクロス網内でパケット転送を行う場合、レベル1のエクスチェンジャのスイッチエレメントSE0〜SE3に対するスケジューリングを行った際、調停に負けたパケットをスイッチエレメントSE0〜SE3の他のスイッチエレメントにおける空きスイッチを使用して転送するようにようにした。

(もっと読む)

1 - 20 / 36

[ Back to top ]