Fターム[5B045EE07]の内容

Fターム[5B045EE07]に分類される特許

1 - 20 / 23

相互接続装置、および、相互接続装置の制御方法ならびに当該方法をコンピュータに実行させるプログラム

【課題】相互接続装置においてデッドロックを回避しつつ、レイテンシを低減する。

【解決手段】リクエスト管理部は、複数のマスタのいずれかから複数のスレーブのいずれかに対して発行されたリクエストがそのリクエストに先行して発行された先行リクエストの複数のスレーブのいずれかへの出力を待つべき待機リクエストである場合にはその待機リクエストに先行リクエストを対応付けて管理する。調停部は、複数のマスタから発行された複数のリクエストを調停して調停したリクエストを複数のスレーブのうち調停したリクエストの宛先である応答デバイスに出力する。リクエスト待機制御部は、待機リクエストを待機させて、その待機リクエストに対応する先行リクエストが複数のスレーブのいずれかに出力された後に待機リクエストを調停部へ出力する。

(もっと読む)

情報処理装置及び画像形成装置

【課題】一つのチップの機能ブロックから別のチップの機能ブロックへデータを転送する場合に、予め定められた機能ブロックからのデータについては、転送遅延が生じないようにする。

【解決手段】監視部37は、第1の送信バッファ25に蓄積されているデータ量が、所定のしきい値を超えていれば、第1のチップ11と第2のチップ13との間でデータの転送遅延が発生するとみなす。しきい値を超えれば、第2にチップ13に配置された複数の第2の機能ブロックのうち予め定められた第2の機能ブロックについては、第2のチップ13において、第2の送信バッファを経由させずに第2の追越用ラインを経由させ、第1のチップ11において、第1の受信バッファ35を経由させずに第1の追越用ライン39を経由させて、宛先となる第1の機能ブロック19へ転送させる。

(もっと読む)

データ転送装置、並列計算機システムおよびデータ転送装置の制御方法

【課題】データの転送効率を低下させることなく各計算ノード間における通信に対して帯域を適切に分配できない。

【解決手段】1つの側面では、ルータ10は、受信した複数のデータを調停して転送する転送装置である。このルータ10は、複数のデータを受信した場合には、データが受信されるまでに調停の相手になった他のデータの累積数を取得する。また、ルータ10は、取得したデータの数に基づいて、各データから取得した累積数を更新する。そして、ルータ10は、更新した各データの累積数に基づいて、受信したデータを調停して、計算ノード2aへ送信するデータを選択する。その後、ルータ10は、選択したデータに更新した累積数を格納し、更新した累積数を格納したデータを計算ノード2aへ送信する。

(もっと読む)

データプロセッサ

【課題】プロセッサコアのローカルメモリや共有メモリの所要のアドレスに対して小さな回路規模で排他制御を行うことができるデータプロセッサを提供する。

【解決手段】要求に従ってバスロック設定と解除が可能にされるシステムバス(5)を共有する複数個のプロセッサコア(20,40)が相互に互いの内部リソース(22,42)を共有するデータプロセッサ(1)において、プロセッサコアが内部リソースの第1アドレス(ロック変数割り当てアドレス)へアクセスを行うときバスロックの要求を伴って当該アクセス要求をシステムバスに出力することによりシステムバスにバスをロックさせると共にシステムバスから当該プロセッサコアに帰還されるのを待って当該アクセス要求を処理し、プロセッサコアが内部の第2アドレスへアクセスを行うとき当該アクセス要求をプロセッサコアの内部で処理する。

(もっと読む)

インターコネクト内のバリアトランザクション

データ処理装置のためのインターコネクト回路機構が開示される。このインターコネクト回路機構は、少なくとも1つのイニシエータデバイスが、少なくとも1つの受信デバイスにアクセスする際に経由することができる、データルートを提供するように構成され、このインターコネクト回路機構は、少なくとも1つのイニシエータデバイスからトランザクション要求を受信するための、少なくとも1つの入力と、少なくとも1つの受信デバイスにトランザクション要求を出力するための、少なくとも1つの出力と、少なくとも1つの入力と少なくとも1つの出力との間でトランザクション要求を送信するための、少なくとも1つの経路と、受信されたトランザクション要求を、少なくとも1つの入力から少なくとも1つの出力へルーティングするための制御回路機構とを含み、この制御回路機構が、バリアトランザクション要求に応答して、少なくとも1つの経路のうちの1つに沿って通過するトランザクション要求のストリーム内部のバリアトランザクション要求に対しての、少なくとも一部のトランザクション要求の順序付けを、トランザクション要求のストリーム内のバリアトランザクション要求の後に発生する少なくとも一部のトランザクション要求に対しての、トランザクション要求のストリーム内のバリアトランザクション要求の前に発生する少なくとも一部のトランザクション要求の順序変更を許可しないことによって、維持するように構成され、このバリアトランザクション要求は、トランザクション要求のストリーム内部のトランザクション要求のうちのいずれが、順序付けが維持されるべき少なくとも一部のトランザクション要求を含むかを指示する、指示子を含む。  (もっと読む)

(もっと読む)

分散システム内の種々のコンポーネントの活動を同期させること

インターコネクトを介して受信側デバイスにトランザクション要求を発行するイニシエータデバイスが開示される。イニシエータデバイスは、前記インターコネクトから要求を受信し、前記インターコネクトに要求を発行する少なくとも1つのポートと、バリアトランザクション要求を生成するバリア発生器とを備え、バリアトランザクション要求は、インターコネクトを通過するトランザクション要求のストリーム内の少なくともいくつかのトランザクション要求の順序付けが、バリアトランザクション要求に関してトランザクション要求のストリームにおいてバリアトランザクション要求の前に発生するトランザクション要求の少なくともいくつかの再順序付けを可能にしないことによって維持されるべきであることを、インターコネクトに示し、トランザクション要求の少なくとも部分集合の進捗を問い合わせる同期要求の受信に応答して、イニシエータデバイスは、トランザクション要求の少なくとも部分集合内の任意の保留中のトランザクション要求を実行し、バリア発生器においてバリアトランザクション要求を生成し、少なくとも1つのポートを介してインターコネクトにバリアトランザクション要求を発行し、バリアトランザクション要求に対する応答を受信することに応答して、同期要求に対する応答としてアクノリッジ信号を発行するように応答する。  (もっと読む)

(もっと読む)

インターコネクト内の低減されたレイテンシのバリアトランザクション要求

データ処理装置のためのインターコネクト回路機構が開示される。このインターコネクト回路機構は、少なくとも1つのイニシエータデバイスが、少なくとも1つの受信デバイスにアクセスする際に経由することができる、データルートを提供するように構成され、このインターコネクト回路機構は、少なくとも1つのイニシエータデバイスからトランザクション要求を受信するための、少なくとも1つの入力と、少なくとも1つの受信デバイスにトランザクション要求を出力するための、少なくとも1つの出力と、少なくとも1つの入力と少なくとも1つの出力との間でトランザクション要求を送信するための、少なくとも1つの経路と、受信されたトランザクション要求を、少なくとも1つの入力から少なくとも1つの出力へルーティングするための制御回路機構とを含み、この制御回路機構が、バリアトランザクション要求に応答して、少なくとも1つの経路のうちの1つに沿って通過するトランザクション要求のストリーム内部のバリアトランザクション要求に対しての、少なくとも一部のトランザクション要求の順序付けを、トランザクション要求のストリーム内のバリアトランザクション要求の後に発生する少なくとも一部のトランザクション要求に対しての、トランザクション要求のストリーム内のバリアトランザクション要求の前に発生する少なくとも一部のトランザクション要求の順序変更を許可しないことによって、維持するように構成され、この制御回路機構が、応答信号生成器を含み、この応答信号生成器は、バリアトランザクション要求の受信に応答して、応答信号を発行し、この応答信号は、バリアトランザクション要求に応答して遅延されたいずれかのトランザクション要求が更に先へ送信され得ることを、上流のブロッキング回路機構に指示する。  (もっと読む)

(もっと読む)

半導体集積回路装置および半導体集積回路装置の動作方法

【課題】バスシステムを効率的に使用できる半導体集積回路装置および半導体集積回路装置の動作方法を提供すること。

【解決手段】ステータス情報が書き込まれるステータスレジスタおよび更新要求が書き込まれる更新制御レジスタを含むレジスタ部を有し、更新制御レジスタに更新要求が書き込まれた場合にステータスレジスタの更新を行うCPU100、200、およびI/O300に対し、ステータスレジスタに記憶されるステータス情報を読み出しかつ更新制御レジスタに更新要求を書き込むための拡張ロード命令を実行できるように、CPU100、200、バスシステムおよびI/O300を構成した。

(もっと読む)

マルチプロセッサシステム

【課題】マルチプロセッサシステムが同時に実行できるサービスの上限数の制限を緩和し、且つ、マルチプロセッサシステムの処理効率を向上させる。

【解決手段】ホストプロセッサ12と、ホストプロセッサ12のアクセラレータとして動作して、サービスを実行するコプロセッサ14と、ホストプロセッサ12とコプロセッサ14とを接続するバス16と、を備える。ホストプロセッサ12は、第1通信方式に基づいて、ユーザアプリケーション18aによって発行されたアプリケーションデータをコプロセッサ14にバス16を介して転送する第1通信管理部123と、第1通信方式よりもバストラフィックが少ない第2通信方式に基づいて、ユーザアプリケーション18aによって発行されたアプリケーションデータをコプロセッサ14にバス16を介して転送する第2通信管理部124と、第1及び第2通信管理部123,124を選択的に制御する制御部121と、を備える。

(もっと読む)

画像出力装置および3次元画像表示システム

【課題】マルチコアプロセッサを用いて複数の画像データを効率的に並列処理して出力可能にする。

【解決手段】複数の画像メモリ51〜54と、マルチコアプロセッサ21内の複数のコア31〜34とを、バス25を介して1対1に対応させる。そして、複数のコア31〜34によって画像処理された複数の画像データを、バス25を介して複数の画像メモリ51〜54に並列的に格納する。複数の画像メモリ51〜54に格納された複数の画像データは、複数の出力I/F55〜58によって並列的に出力される。すなわち、ビデオカードのGPUを用いることなく、マルチコアプロセッサ21によって直接的に画像処理された複数の画像データを、複数の画像メモリ51〜54および複数の出力I/F55〜58を介して並列的に出力する。これにより、マルチコアプロセッサ21が有するコアの数だけ並列的に画像処理を行って並列的な画像出力が可能となる。

(もっと読む)

バス調停方式およびマルチCPU構成のプログラマブルコントローラ

【課題】マルチCPUシステムにおいて、各CPUが、共有メモリにアクセス中でも、それぞれの内部バスに接続されている各種メモリの使用を可能として、また、各CPU自体はバス調停を行う必要性をなくす。

【解決手段】本方式は、CPU21に内部バスB21を介してFPGA26を接続し、FPGA16,26それぞれを外部バスB13,B23を介してモジュールバス30に共通接続すると共に、FPGA26にメモリバスB22を介して共有メモリ27を接続し、FPGA26は、CPU21が共有メモリ27にアクセス中でメモリバスB22を占有中のときに、CPU11からアクセス要求があると、CPU21のアクセス優先、アクセス先着順、CPU11アクセス優先かの判断により、共有メモリ27にCPU11がアクセスするためのバス調停を行う。

(もっと読む)

制御装置

【課題】制御装置内に設けられた複数のマイコン間の通信において、データの授受時間の制限を軽減することが出来る制御装置を提供する。

【解決手段】信号出力部17から出力される切替信号の出力値が第1の値の場合は、マイコン11とEEPROM31との間でデータの授受を行い、信号出力部17から出力される切替信号の出力値が第2の値の場合は、マイコン21とEEPROM31との間でデータの授受を行う。マイコン11とマイコン21との間におけるデータの授受に際して、クロックの出入力作業は、EEPROM31との間においてデータを授受する一方のマイコンのみが行えば良く、また、これにより、ACK,NACKの確認作業が不要となるため、制御装置100内に設けられたマイコン11とマイコン12との間の通信において、データの授受時間の制限を軽減することが出来る。

(もっと読む)

マルチプロセッサシステムおよび起動方法

【課題】より短時間でマルチプロセッサシステムの起動を完了させることができるようにする。

【解決手段】マルチプロセッサシステムが起動される場合、期間151において、主プロセッサの起動処理が行われ、次に、副プロセッサのそれぞれは、自分が実行すべきプログラムの転送処理を開始する。このとき、バス調停装置によるアービトレーションが行われるので、副CPU起動用プログラム121の転送、副CPU起動用プログラム122の転送、および副CPU起動用プログラム123の転送が、期間152、期間154、および期間156において、並行して行われることになる。副CPU起動用プログラム121乃至副CPU起動用プログラム123の転送が完了すると、期間153、期間155、期間157において、それぞれ副プロセッサ106の起動処理が行われる。

(もっと読む)

並列演算装置および並列演算方法

【課題】複数の演算ユニット間の配線を簡易にすることを可能とする並列演算装置および並列演算方法を提供する。

【解決手段】並列演算装置が、予め定められた順序でデイジーチェーン制御バスを介してデイジーチェーンされている複数のユニットと、複数のユニットの内のいずれか1つが出力する出力値がユニット出力バスを介して入力され、該入力された出力値を複数のユニットのそれぞれにユニット入力バスを介して入力値として出力する増幅器と、を有する。このユニットは、ユニット出力バスを介して入力される増幅器からの入力値に基づいて、ユニット毎に予め定められた演算方法により演算し、また、トークンが前のユニットからデイジーチェーン制御バスを介して入力されたことに応じて、トークンを次のユニットにデイジーチェーン制御バスを介して出力すると共に、演算した結果を出力値として増幅器にユニット出力バスを介して出力する。

(もっと読む)

半導体装置

【課題】マルチコア方式の半導体装置では、CPU単体の消費電力は低減されるが、CPU−CPU間などのデータ・バスにおける消費電力が増大する。

【解決手段】データ送信に無線信号のバックスキャッタ方式を用いる複数のCPUと、CPU−CPU間などのデータ送受信を仲介するルータ回路と、スレッドのスケジューリング機能を有するスレッド回路と、を有することで、低消費電力で高演算能力の半導体装置を安価に提供することができる。

(もっと読む)

調停回路、クロスバ、リクエスト選択方法、及び情報処理装置

【課題】ユニットの何れかから発行されたリクエストが長時間、未処理となるのを回避するための技術を提供する。

【解決手段】セレクタ732には、SMモジュール710、及びIOモジュール720からそれぞれ、キューバッファ部711毎にリクエストが出力される。プライオリティ・ロジック731は、各キューバッファ部711のキュー制御部712から出力されるQueue exist信号により、未処理のリクエストが存在するユニットを特定し、そのユニットのなかでリクエストを選択すべきユニットを、そのときに有効としている規則に従って選択する。その規則は、カウンタ733が出力するキャリー信号により複数回、動的に変更する。セレク732にはその選択結果に応じた選択信号を出力し、選択したユニットのリクエストを選択・出力させる。

(もっと読む)

データ処理装置

【課題】マルチプロセッサにおいて、一方のローカルメモリを一方のプロセッサが高速アクセスでき、他方のプロセッサからもアクセス可能とすること。

【解決手段】プロセッサ1にローカルバス102を介しローカルメモリ101が接続され、プロセッサ2にローカルバス202を介しローカルメモリ201が接続され、102とシステムバスSBにバスブリッジ(BB)103が接続され、202とSBとBB203が接続され、SBと101にバスインターフェースユニット(BIU)3が接続され、SBと201にBIU5が接続される。1から101へ102を介し高速アクセスする一方、1から102、103、SB、5のP1・P3を介し2からは202、203、SB、3のP2・P3を介し101をアクセスする。2から201へ202を介し高速アクセスする一方、2から202…3のP2・P3を介し1からは102…5のP1・P3を介し201をアクセスする。

(もっと読む)

クロスバーのストールした出力キューの情報をクリアするためのシステム及び方法

【課題】クロスバーのストールした出力キューの情報をクリアするためのシステム及び方法を提供する。

【解決手段】各時限ポート204は、入力キュー302、出力キュー304、及びキュータイマ306を備える。入力キュー302及び出力キュー304は、1つ又は複数の情報キュー308、312をそれぞれ備える。各情報キュー308、312は、単一の情報を記憶するように構成されている。 情報キュー308、312は直列に接続されて、1つの情報が情報キュー308、312の最初のものに到着するようにされている。その後、この1つの情報は、直列に又は順次、情報キュー308、312の最後のものへ伝播される。この1つの情報が出口キューに存在している時、次に、その情報をそのキューに結合された出力接続部上へ通信することができる。

(もっと読む)

マルチ・ノードコンピュータシステム

【課題】削減されたハードウェア資源を用いてマルチ・ノードコンピュータシステム内のノード内ファームウェアとノード間ファームウェアとの間でデータを転送する方法およびシステム。

【解決手段】1バイト制御モジュールおよび1バイトデータモジュールを通したコンピュータノードとノード間コントローラとの間でのデータ通信を可能にするため、1組の制御コードおよびデータ転送機能が提供される。

(もっと読む)

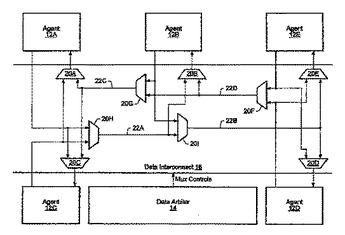

部分的にポピュレートされる階層型クロスバ

様々な実施形態で、装置は、複数のエージェントと相互接続を備える。一実施形態では、複数のエージェントは第1から第4までのエージェントを含む。相互接続は、エージェント間で通信パスを形成するように切換え可能な(例えば複数の選択回路を使用して)複数のセグメントを備え、第1セグメントは、第1エージェントから第2エージェントへの第1通信パスに含まれ、また第3エージェントから第4エージェントへの第2通信パスにも含まれる。別の実施形態では、各セグメントは選択回路によって駆動される。少なくとも1つの選択回路は、少なくとも1つのセグメントと、少なくとも1つのエージェントからの出力とを、入力として有する。さらに別の実施形態では、アービタが、セグメントを介した宛先エージェントへの通信パスを、各要求に対して相互接続上で決定するように構成される。アービタは、対応する通信パス中の各セグメントが利用可能であるような要求のサブセット間で、調停するように構成される。  (もっと読む)

(もっと読む)

1 - 20 / 23

[ Back to top ]