Fターム[5B046BA09]の内容

CAD (21,103) | 設計対象(段階、工程) (4,232) | テストデータ作成 (81)

Fターム[5B046BA09]に分類される特許

1 - 20 / 81

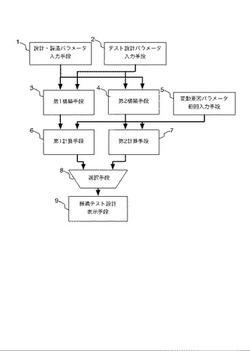

テスト設計手段選択装置及びテスト設計手段選択方法

【課題】LSIの設計製造を通じて得られる利益を最大化するためのテスト設計を、適切に選択するためのテスト設計手段選択装置及びテスト設計手段選択方法を提供する。

【解決手段】テスト設計は、LSIのチップ面積、テスト実行時間、テストパターン生成時間、故障検出率の4つの項目に影響を与えるため、フルスキャン(FS)設計、組込み自己テスト(BIST)設計、テストデータ圧縮・展開(EDT)設計の3つのテスト設計についてこの 4つの関係をモデル化する。このモデルにより各テスト設計のトレードオフを捉え、設計製造環境に応じた設計製造コストを示し、その結果LSI 設計フローの早い段階で適切なテスト設計(DFT手法とそのパラメータ)を容易に選択できる。このテストモデルを用いることで、いくつかの設計製造環境に応じて適切にテスト設計を選択することができる。

(もっと読む)

活動センサでデジタル回路を設計するシステム及び方法

【課題】SoC回路の場合であっても、機能記述ファイルに基づいてデジタル回路がそれ自体の出力変数(温度など)を計算できるようにする。

【解決手段】デジタル回路の機能記述を含むファイル14に基づいたデジタル回路シミュレータ12とシミュレータ12に供給されるテストベンチ26を実行する時にデジタル回路から出力変数30’を予想する手段28とイベントカウンタ34’とを含み、イベントは、テストベンチ26を実行する時にシミュレータ12によって提供された制御信号を用いて検出される。システムは、イベントカウンタからの出力データを用いてデジタル回路の出力変数30’を計算するモデルを反復して最適化することによって、イベントカウンタ34’の一部を選択する手段40、44とイベントカウンタの選択された部分及び最適化された計算モデルを登録する手段40、44とを更に含む。

(もっと読む)

HDL環境のためのグローバルクロックハンドラーオブジェクト

【課題】HDL環境において模擬クロック信号を発生しコントロールすること。

【解決手段】ハードウェア記述言語(HDL)環境に使用するためのグローバルなクロックハンドラーオブジェクトが開示される。HDLモジュールは、1つ以上のクロックステートメントを含む。コンピュータシステムがクロックステートメントを実行するとき、クロックハンドラーオブジェクトがコールされる。クロックハンドラーオブジェクトは、集積回路設計の1つ以上の模擬ファンクションブロックに対する模擬クロック信号を発生する。各模擬クロックは、個別の且つ独特のスレッドに指定される。クロックハンドラーオブジェクトは、集積回路設計に対する各模擬クロック信号を管理するように構成されたシングルトンオブジェクトである。各模擬クロック信号の発生及びコントロールは、ダイナミックアレイにおけるクロックハンドラーオブジェクトにより遂行される。ダイナミックアレイは、模擬クロック信号ごとにパラメータを指定するエレメントを含む。

(もっと読む)

スキャンパタン作成手法、プログラム、スキャンパタン作成装置、テスタ、及びテスト方法

【課題】スキャンテストに要する時間を削減するテストパタン作成方法を提供する。

【解決手段】テストパタン作成方法は、組み合わせ論理回路と少なくとも一つのスキャンチェーンとに関する情報を、記録媒体から読み出し、少なくとも一つのスキャンチェーンの入力側に近いフリップフロップから順番に抽出し(ステップS21)、抽出したフリップフロップがスキャンキャプチャ動作によって組み合わせ論理回路から取り込むキャプチャデータと照合する期待値の必要性を判定し(ステップS22〜S25)、期待値が不要と判定されたフリップフロップが入力側から連続して存在するフリップフロップの数を取得し(ステップS27)、スキャンチェーンに含まれるフリップフロップの総数と、取得したフリップフロップの数との差分を、スキャンキャプチャ動作後のスキャンシフト回数として決定する(ステップS28)。

(もっと読む)

テストパターン生成装置,テストパターン生成方法およびテストパターン生成プログラム

【課題】並列処理に起因するテストパターンの増加を抑止する。

【解決手段】第2の演算処理装置20は、複数の第1の演算処理装置10が要求値の設定対象となる同じ回路素子に対してそれぞれ異なる要求値を設定するコンフリクトが発生するか否かを要求値バッファ22aに格納された要求値に基づいて判定する。そして、第1の演算処理装置10が要求値の設定対象となる入力点に設定しようとする要求値が、他の第1の演算処理装置10が当該入力点に設定する要求値と異なるコンフリクトが発生すると、第2の演算処理装置20が判定した場合、当該第1の演算処理装置10は当該要求値の設定を抑止する。

(もっと読む)

開発支援方法及びプログラム

【課題】制御プログラムの開発を効率的に行なうことができる開発支援方法を提供する。

【解決手段】開発支援方法は、実装基板製造装置に組み込まれた制御プログラムによって出力されるログをログファイルから読み出すログ取得ステップ(S11)と、駆動部の状態を、ログ取得ステップで取得されたログに記述されている順に遷移させるようなテストシナリオを作成するテストシナリオ作成ステップ(S12)と、テストシナリオ作成ステップで作成されたテストシナリオに沿って、制御プログラムをテスト実行するテスト実行ステップ(S13)とを含む。

(もっと読む)

検証方法及び検証プログラム

【課題】回路検証に用いるシナリオ等のプログラムを効率的に開発する。

【解決手段】コンピュータが、検証対象に対する命令を記述したシナリオ(S65)の所定記述部分の命令実行を制限する制限情報を含んだ設定制限リスト(S67)を用い、その内容を示すシナリオチェッカ(S69)を生成する。コンピュータは、検証対象のシミュレーション(S74)において、シナリオ(S65)の上記所定記述部分の命令実行時に、シナリオチェッカ(S69)を用いて当該命令が制限情報を含むか否かチェックし、その結果(S75)を出力する。

(もっと読む)

レイアウト修正・ライブラリセル置換モジュール及び半導体装置設計用EDAツール

【課題】効率的に検出率を向上する方法及び未検出箇所が不良になる確率を低減させる手法により、多層配線層の検査工程を含む半導体製品の製造技術において、検査の迅速性を損なうことなく、半導体製品の製造歩留まりを向上させる技術を提供する。

【解決手段】不良の検出が困難な未検出領域について、パターン等の変更を行い検出率、致命率の改善を行う。例えば、検出が困難な未検出領域についてパターンを追加することで検出可能とする、パターンの間隔を広げることで不良率を低下させることなどが考えられる。

(もっと読む)

半導体集積回路のテスト設計支援装置、テスト設計支援方法及びプログラム

【課題】チップ上の機能ブロックを実動作よりも、広範囲かつ同時に動作させても、チップを誤動作させないテストパターンを作成できる半導体集積回路テスト設計支援装置を提供する。

【解決手段】本発明の半導体集積回路テスト設計支援装置は、機能ブロックを単独で動作させて、IRドロップ解析を行うIRドロップ解析部と、チップ上の小領域を示す番地(X,Y)単位に量子化したIRドロップ量Zを算出して、マッピング値(X,Y,Z)を作成するマッピング値作成部と、前記機能ブロックを、複数動作させた場合の前記マッピング値(X,Y,Z)を、同一の前記番地(X,Y)の前記量子化したIRドロップ量Zを加算することによって算出し、同時動作させた場合の各前記番地(X,Y)の前記量子化したIRドロップ量Zが、許容値以内であれば、同時動作可能な機能ブロックとしてグルーピングするグルーピング部とを備える。

(もっと読む)

半導体集積回路の設計支援装置、設計支援方法及びプログラム

【課題】不具合の再現が可能であって、秘匿性の高い再現データの生成が可能な半導体集積回路の設計支援装置を提供する。

【解決手段】図1に示す設計支援装置は、設計データを複数のFSMに変換するFSM変換部と、複数のFSMから装置が動作するために必要な論理構造を生成するFSMデータ探索部と、論理構造から装置の不具合が再現可能な縮小データを出力する縮小データ生成部と、を備えている。FSMデータ探索部においては、任意に選択したFSMから設計支援装置が動作可能であって、必要最低限の情報しか含まない情報を探索し、生成する。

(もっと読む)

論理計算システム、生成装置、生成方法及びプログラム

【課題】 多くの論理変数や論理演算を含む複雑な論理計算を高速かつ大量に処理可能な論理計算システム等を提案する。

【解決手段】 ネットリスト記憶部111が記憶するネットリストについて、タスクグラフ生成手段113は、一つ又は複数の素子をタスクに置き換えて、各素子のデータの依存関係からタスクグラフを生成する。プログラム生成部115は、複数のデータのそれぞれの移動後の位置を定義するデータ転送命令を追加して、実行プログラム105を生成する。情報処理部107は、実行プログラム105を並列分散処理する。事前に静的にネットリストを処理するため、純計算時では信号線を追跡する必要がなくなる。さらに、SIMD並列化の効率を高めることができる。また、データ転送命令により、タスク間のデータ転送を予め決まったとおりに効率的に行うことができる。

(もっと読む)

半導体集積回路の検証装置

【課題】半導体集積回路のデータ転送の検証時間を短縮することができる半導体集積回路の検証装置を提供する。

【解決手段】半導体集積回路の検証に用いるシナリオとパラメータとが記述されたリスト21、22が格納された設定ファイル記憶部14と、前記リスト21、22に基づき検証に用いる転送データ43を生成する転送データ生成部35とを具備している。前記転送データ生成部35は、前記シナリオの情報を記述したタグ42を生成することを特徴とする。

(もっと読む)

論理検証シナリオ生成装置、及び、論理検証シナリオ生成プログラム

【課題】CPUの論理検証に用いる検証シナリオ、及び期待値の生成負荷を抑える。

【解決手段】RTL記述されたCPUの論理検証のためのテストプログラムを生成する論理検証シナリオ生成装置であって、テストライブラリと、期待値フォーマット記憶部と、検証命令アドレス、前命令空間、後命令空間、データ空間、分岐命令空間、スタック空間とを有するメモリモジュールであって、テストライブラリから順次選択した検証命令と前後命令組合せとに基づいて、検証命令アドレスに検証命令を、前命令空間に前命令を、後命令空間に後命令を記憶し、前命令が分岐命令である場合に前命令の分岐先アドレスに検証命令アドレスを記憶したメモリモジュールをテストプログラムとして生成するテストプログラム生成部と、テストプログラムの各命令について期待値フォーマットを取得し、当該命令をデコードしたデコード情報に基づいて期待値を生成する期待値生成部と、を有する。

(もっと読む)

テストベンチ生成機能を有する動作合成装置と方法及びプログラム

【課題】動作シミュレーションとRTLシミュレーションで同じテストベクタを使用できるためのテストベンチを生成する動作合成装置及び方法及びプログラムを提供する。

【解決手段】入力印加のタイミング及び出力観測のタイミングを表す信号、及び前記入力印加タイミング信号と前記出力観測タイミング信号のための論理回路を生成する入力印加・出力信号観測タイミング信号生成手段104と、当該信号を観測して入力印加、及び、出力観測をおこなうテストベンチを作成するテストベンチ生成手段106と、を有する。

(もっと読む)

半導体集積回路の論理設計検証方法、その論理設計検証装置、及び、コード・カバレッジ・ツール

【課題】不要変数や未変化変数を確認するときの時間を短縮すること。

【解決手段】本発明では、RTLソース・コード2に対する論理シミュレーションを実行し、その実行結果により、RTLソース・コード2に含まれる変数のうちの、信号の変化がない未変化変数を選択し、未変化変数の中から、インスタンス間信号リスト3が表す変数に一致する候補未変化変数と、インスタンス間信号リスト3が表す変数に一致しない不要変数とを選択する。これにより、設計者が不要変数を確認する時間を短縮できる。更に、インスタンス間信号リスト3から、候補未変化変数に対応する候補出力ノードを選択し、重複する候補出力ノードのうちの1つの候補出力ノードと、重複しない候補出力ノードとを選択出力ノードとして選択する。未変化変数に対して選択出力ノードに集約することにより、設計者が未変化変数を確認する時間を短縮できる。

(もっと読む)

半導体集積回路の診断テストパターン数最適化プログラム

【課題】

組込み自己試験法によるテスト機構を備えた半導体集積回路において、診断テストパターン数を増加させずに故障検出率を向上させることができるプログラムを提供する。

【解決手段】

診断テストパターンとして発生した擬似乱数の各々で新たに検出される故障数が0又は、所定の基準値以下であるかを判定するステップと、テストグループに割り当てられた診断テストパターン発生回数の最後で発生した擬似乱数で新たに検出される故障数が任意の基準値以上であるかを判定するステップとから、パス数比でテストグループに割り当てられた診断テストパターン数を、故障の検出のし易さ(難易度)に応じて再配分することで診断テストパターン数を最適化し、故障検出率を向上させる。

(もっと読む)

故障マスキング係数を定めるための逆方向解析の改善

電子回路内の故障可観測性を定めるための方法及び構成が提示される。本方法では、各素子について、発生した故障が解析出力信号における異常を引き起こしうる期間が定められる。 (もっと読む)

テスタ用テストパタン生成方法、テスタ用テストパタン生成プログラム、及びテスタ用テストパタン生成装置

【課題】テスタによる機能テストのテスト精度を低下させずに、テスタ用テストパタンにおけるタイミングセット数を削減する。

【解決手段】本発明によるテスタ用テストパタンの生成方法は、論理設計時に生成された第1テストパタン201を、半導体集積回路で用いられる最高周波数のクロック信号20に応じたサイクルでサイクライズするステップと、第1テストパタン201におけるタイミングエッジを、タイミングエッジ直前のピリオド境界に変更して第2テストパタン301を生成するステップとを具備する。

(もっと読む)

論理検証実行システム

【課題】

乱数要素を持たせた論理検証において、検証論理にあるフリップフロップのうち全く動作しないものや、動作回数が著しく低いものがある。そして、検証論理に含まれるフリップフロップ全てがあらゆる条件下で動作するまで検証を行うと検証期間の増大する。

【解決手段】

検証論理に入力する命令およびデータのパターンを乱数を用いて生成するための制約条件を定義したシナリオファイルを複数用意し、複数のファイルから実行対象とするファイルをランダムに選び、検証実行時にカバレッジ情報を出力し、蓄積したカバレッジ情報を用いて低動作回数フリップフロップを抽出し、抽出したフリップフロップを動作させたファイルが多く実行されるように動作回数に応じて実行確率を算出する処理を行うことで、抽出したフリップフロップを動作させたファイルの実行回数を上げ、検証論理にある全フリップフロップの動作回数を平均的に上げ、効率がよい論理検証を可能にする。

(もっと読む)

論理検証装置、論理検証方法

【課題】種々のメモリ規格のメモリに対応して論理検証を可能とし、コーナーケースを抜けなく論理検証できる論理検証装置を提供すること。

【解決手段】CPUが発行する第1のコマンドを、第2のコマンドに変換してメモリ107に供給するメモリコントローラ106の論理を検証する論理検証装置100であって、メモリ107の規格情報を記憶したメモリ規格情報記憶手段103と、規格情報が有するアドレス対応情報に従い、第1のコマンドから変換される第2のコマンドの期待値を生成する期待値生成手段108と、第1のコマンドをメモリコントローラ106に発行するコマンド発行手段101と、メモリコントローラ106が第1のコマンドから変換した第2のコマンドを監視し、期待値と比較する監視手段104と、を有することを特徴とする。

(もっと読む)

1 - 20 / 81

[ Back to top ]