Fターム[5B047EB06]の内容

Fターム[5B047EB06]の下位に属するFターム

交代バッファリング (21)

Fターム[5B047EB06]に分類される特許

1 - 20 / 118

演算方法、演算装置、画像処理装置およびプログラム

【課題】 遅延メモリの省容量化を実現しつつも、ある一定のメモリ帯域の中でさまざまな形態の画像処理を実現するため、データの解像度と参照枚数が変化しても柔軟に対処できる画像処理方法及びその装置を提供する。

【解決手段】 画像データの転送単位を設定し、該転送単位の画像データを処理するために必要な参照用データの転送単位を取得する。バッファの容量に収まるように、画像データの転送単位と参照用データの転送単位とから、画像データの転送量を取得する。画像データの転送量と画像データの転送単位とに基づいて、バンド領域の高さを取得する。

(もっと読む)

画像処理装置、画像処理システム、及びバンク管理方法

【課題】様々な動作周期及び動作開始タイミングに適切に対応できるようにバンク管理を行なう画像処理装置、画像処理システム、及びバンク管理方法を提供する。

【解決手段】画像処理装置は、3つのバンク領域を示す3つのアドレスを格納する第1乃至第3のアドレスレジスタと、フラグと、入力画像切り替わりのタイミングで第1のアドレスレジスタと第2のアドレスレジスタとの間で格納アドレスを入れ替えるとともにフラグをセットし、第1のアドレスレジスタの格納アドレスを入力画像書き込みアドレスとして供給する画像入力バンク管理部と、フラグがセット状態の場合、処理画像切り替わりのタイミングで第2のアドレスレジスタと第3のアドレスレジスタとの間で格納アドレスを入れ替えるとともにフラグをリセットし、第3のアドレスレジスタの格納アドレスを処理画像読み出しアドレスとして供給する画像処理バンク管理部とを含むことを特徴とする。

(もっと読む)

画像形成装置、画像形成方法、プログラムおよび記録媒体

【課題】コピー時に原稿の表面と裏面を同時に読み取るときに要するメモリ容量を削減する。

【解決手段】スキャナ画像処理部203は、メモリ704からブロック(一定サイズの画像データ)毎に、表面と裏面が交互に読み出された各ブロックに対して画像処理を実行する。前ブロックの最後の数ライン分のデータを破棄せずにメモリ704に残し、次ブロックの処理時にスキャナ画像処理部203へ転送する。

(もっと読む)

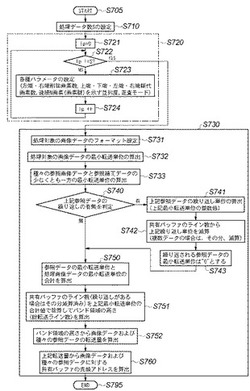

データ処理装置

【課題】複数のバッファを交互に切り替えて分割したブロック毎に処理を行うデータ処理装置において、処理に必要なデータが、データを転送する際の転送の切れ目をまたいでいるような場合でも、各ブロックの処理の間のロス時間を低減することができるデータ処理装置を提供する。

【解決手段】予め定められたデータ取得単位毎にデータを取得するデータ取得部と、1つのデータ取得単位で取得する量のデータを記憶する記憶容量に加え、データ取得単位に満たない量のデータを記憶する追加記憶容量を具備する複数のバッファ部と、データ取得部が取得するデータの内、有効なデータの量を算出すると共に、取得したデータが有効なデータであるか否かを表す有効データ情報を出力する有効データ量算出部と、複数のバッファ部を排他的に制御して、取得したデータの複数のバッファ部のいずれか1つのバッファ部への書き込みを制御するデータ書き込み制御部と、を備える。

(もっと読む)

画像処理装置及び画像形成装置

【課題】低消費電力化を図れる画像処理装置を提供する。

【解決手段】書込読出制御部53は第1及び第2のラインメモリ51a,51bの中から読み出し可能なラインメモリと書き込み可能なラインメモリとを交互に切り換える制御する。1ラインの画像データが上記ラインメモリに書き込まれる際に、白ライン判定部31はそのラインの画像データに対応する画像が白ラインか否か判定する。白ラインであれば、画像処理制御部23はそのラインの画像データをラインメモリから読み出す読出クロックCLK3及び画像処理部27で使用される動作クロックCLK4の生成を停止する。

(もっと読む)

メモリ制御方法、メモリ制御装置、および画像形成装置

【課題】シリアル−パラレル変換とパラレル−シリアル変換を効率的に実行する。

【解決手段】画像処理前のラインデータを記憶するラインメモリと画像処理後のラインデータを記憶するラインメモリとを同一素子で構成し、シリアルデータ形式で入力されるラインデータをラインメモリで記憶する処理前・メモリ入力タイミング,記憶された処理前のラインデータをパラレルデータ形式で読み出す処理前・メモリ出力タイミング,処理後のパラレルデータ形式のラインデータをラインメモリで記憶する処理後・メモリ入力タイミング,記憶された処理後のラインデータをシリアルデータ形式で読み出す処理後・メモリ出力タイミング,の4タイミングで制御し、同一ライン周期内に処理前・メモリ出力タイミングの直後に処理後・メモリ入力タイミングを実行すると共に、同一ライン周期内に処理後・メモリ出力タイミングの直後に処理前・メモリ入力タイミングを実行する。

(もっと読む)

画像処理装置、画像形成装置、画像処理方法、画像処理プログラム及び記録媒体

【課題】本発明は、原稿の両面の画像を同時に読み取るとともに、長尺原稿を自動判別してメモリ容量を削減しつつ原稿両面画像データと長尺原稿の片面画像データを切り替えてメモリに保存する。

【解決手段】画像形成装置1は、原稿の表面と裏面をスキャナ部2aとスキャナ部2bで約同時に読み取って、所定のサイズの原稿の表面画像データ1ページ分を記憶する表面メモリ領域と該原稿の裏面画像データ1ページ分を記憶する裏面メモリ領域を備えているメモリ4の該表面メモリ領域と該裏面メモリ領域に、メモリ制御部3によって順次書き込み、表面画像データの画像データが、該表面メモリ領域の上限のデータ量になると、メモリ制御部3が、原稿の裏面のメモリ4への書き込みを停止するとともに、表面画像データを、該表面メモリ領域と該裏面メモリ領域を1つに結合した結合メモリ領域に連続して書き込む。

(もっと読む)

画像処理装置

【課題】メインメモリに格納されたバンドディスクリプタへのアクセス時間を短くできる画像処理装置を提供する。

【解決手段】画像処理装置はブロックディスクリプタ処理部及びバンドディスクリプタ処理部を備える。複数のブロックディスクリプタBLDが主走査方向及び副走査方向に並ぶ複数のブロック領域のそれぞれに割り当てられている。複数のバンドディスクリプタBADが副走査方向に並ぶ複数のバンド領域にそれぞれ割り当てられている。ブロックディスクリプタ処理部はメインメモリに画像データが格納される際に、ブロック領域の先頭の画素を含むバンド領域に割り当てられたバンドディスクリプタBADのメインメモリ上のアドレスをバンドディスクリプタ関係付けアドレスとした場合、バンドディスクリプタ関係付けアドレスの情報を含むブロックディスクリプタBLDをメインメモリに格納する処理を、複数のブロックディスクリプタBLDのそれぞれにおいて実行する。

(もっと読む)

画像処理装置,画像形成装置

【課題】原稿から読み取った画像データからその画像データがカラー原稿と白黒原稿とのいずれであるかを自動判定(ACS判定)するACSモード時において,ACS判定がなされた後にメモリを有効利用することのできる画像処理装置を提供する。

【解決手段】ACS判定がなされたことを条件に,読取データ格納領域M1のうち予め定められた一部の特定格納領域M11を除く残余格納領域M12を開放し,その後は,特定格納領域M11に記憶された画像データを順次繰り返して出力し,その画像データの出力に追随して,画像読取部により読み取られる画像データを特定格納領域M11に順次繰り返して記憶する。

(もっと読む)

光学読取装置、光学読取装置の制御方法、及び、プログラム

【課題】光学読取装置が受光素子を線型に並べたリニアイメージセンサーを用いて読み取った画像を処理する場合に、意図しない画像の反転を防止できるようにする。

【解決手段】読取対象の記録媒体Sの搬送方向に直交する方向に受光素子を線状に配置したリニアイメージセンサー111A、112Aを有し、搬送される記録媒体Sをリニアイメージセンサー111A、112Aにより光学的に読み取って、リニアイメージセンサー111A、112Aの各受光素子の検出値を端から順に読み出して出力する光学読取部と、光学読取部が出力した検出値に基づいて読取画像データを生成し、生成した読取画像データに、リニアイメージセンサー111A、112Aが有する受光素子の読出し順と読取画像データの画素の並び順との関係を示す情報を付加して、他の装置へ送信するゲートアレイ45及びCPU40とを備える。

(もっと読む)

光学読取装置、光学読取装置の制御方法、及び、プログラム

【課題】光学読取装置が読み取った読取画像を他の装置へ転送するための待ち時間を短縮し、読取処理を高速化して利便性の向上を図る。

【解決手段】ドットインパクトプリンター10は、読取対象の媒体を搬送する媒体搬送機構100と、媒体の搬送路Pに設けられ、搬送される媒体を光学的に読み取る光学読取装置110と、を備え、読取範囲内に設定された一または複数の領域を光学読取装置110によって読み取り、読取画像を記憶部に記憶し、少なくともいずれか一つの領域の読み取りが終了すると、他の領域の読み取りが終了する前であっても記憶部に記憶された読取画像を他の装置に送信する。

(もっと読む)

複写機

【課題】複写機において、原稿スキャン処理の速やかな開始を損なわず、また、原稿スキャン処理とプリント処理とが並行して行われる高速コピー処理において、画像データの記録よりもプリント処理が先行せず、光源の明るさチェックを可能とすること。

【解決手段】光源241を備えたキャリッジ240が、ADF230の参照板236に対向する第1の位置で第1ランプチェック処理を行い、その結果が良好でなければ、キャリッジを移動させて第2の位置で第2ランプチェック処理を行う。前記第1ランプチェック処理の結果が良好であれば高速コピー処理が実行され、第2ランプチェック処理の結果が良好であれば、キャリッジを第2の位置から原稿台に対向する位置へ直行させて、高速コピー処理又は通常コピー処理が実行され、その他の場合はコピー処理が中断される。

(もっと読む)

画像読取装置及び画像データ転送方法

【課題】読取対象物の両面を同時に読取可能な画像読取装置において、読み取った画像デ

ータを格納するためのメモリーの容量を低減することを第1に目的とする。また、画像読

取装置において、データ転送時間を短縮することを第2の目的とする。

【解決手段】画像読取装置であって、第1の画像読取センサーと、第2の画像読取センサ

ーと、読み取った表面画像データ及び裏面画像データとを格納可能なメモリーと、表面画

像データの一部と裏面画像データの一部とをメモリーに書き込む部分書込処理と、部分書

込処理でメモリーに書き込んだ表面画像データと裏面画像データとを読み出して読取装置

の外部へ転送する部分読出処理とを実行するメモリー制御部と、を備え、メモリー制御部

は、部分書込処理と部分読出処理とを交互に複数回実行することで、表面画像データ及び

裏面画像データを当画像読取装置の外部へ転送する。

(もっと読む)

情報処理システム

【課題】メモリ装置をアクセスする複数のマスタに対して、必要なデータを円滑に転送する。

【解決手段】情報処理システムは、メモリ装置(MEM0)と、上記メモリの動作を制御可能なメモリ制御装置(SL0)と、それぞれ上記メモリ制御装置を介して上記メモリ装置へアクセス可能な複数のバスマスタ(MS0〜MS3)とを含む。上記メモリ制御装置は、上記バスマスタからのアクセス要求を保持可能なバッファを含み、上記バッファの利用権を上記バスマスタ毎に設定可能である。

(もっと読む)

画像処理装置、画像処理方法、コンピュータプログラム

【課題】 入力画像に対して複数種類の画像処理を行う場合、それぞれの画像処理に適した画像を生成するのが望ましい。しかしながら、それらの画像を同時に保持しようとすると、多くのメモリが必要になってしまう。

【解決手段】 本発明では、入力画像に対して複数種類の画像処理(領域解析処理、文字部ベクトル化処理、図画部ベクトル化処理など)を行う場合、各画像処理を実行する前にそれぞれの画像処理に適した画像を生成する。そして、画像処理の処理結果は領域情報に格納するとともに、各画像処理で使用したワークメモリを開放してから、次の画像処理を行う。

(もっと読む)

画像処理装置

【課題】 画像処理装置において、符号化後のバンドデータを構成するすべてのデータの格納場所のアドレスが連続となるようにして、符号化後のバンドデータの書き込みおよび読み出しにおける遅延の発生を抑制する。

【解決手段】 画像データを構成する複数のバンドデータに対して順番に画像処理を行う画像処理装置において、RAM14は、固定長のバッファ領域を有し、JPEG符号化回路12は、複数のバンドデータを順番に可変長符号化していき、符号化後のバンドデータをバッファ領域の先頭から順番に書き込んでいき、符号化後のバンドデータの終端が、バッファ領域の終端部分における所定長の境界領域内に位置する場合には、次の符号化後のバンドデータをバッファ領域の先頭から書き込む。

(もっと読む)

画像処理装置

【課題】配線数の増大を抑え、回路規模や信号伝達遅延時間の増加を防止して、画像データを90度単位で回転する画像処理装置を提供する。

【解決手段】連続する所定数の画素データ単位で画像データを分割した各画素群の画素データのそれぞれを入力して記憶する複数のメモリ1〜4と、画像データの回転を指示する指示情報を生成する動作モード制御部7と、指示情報に応じて、複数のメモリ1〜4のそれぞれから画素データを読み出すアドレスを複数のメモリのそれぞれに出力して、前記複数のメモリの各対応するアドレスに記憶された画素データを読み出すコントローラ部5と、複数のメモリ1〜4から読み出した複数の画素データを指示情報に応じて並び替えて出力するセレクタ部6とを有する。

(もっと読む)

画像処理装置および画像処理方法、並びにプログラム

【課題】本発明は、メモリの帯域の無駄な消費を抑制すると共に、主メモリへの重複アクセスを抑制することができる画像処理装置を提供する。

【解決手段】主メモリ102上に展開された画像データから主走査方向及び副走査方向に分割された矩形の単位で画像データを読み取り画像処理を行う画像処理装置100において、分割された矩形を囲む矩形の領域であって、隣り合う2つの矩形間の境界を含むように互いに重複する部分を有する参照領域に対して画像処理を行う画像処理手段が、重複する部分に画像処理を行うときに、読み取った画像データをキャッシュに格納する。

(もっと読む)

並列処理プロセッサシステム

【課題】 複数のプロセッサを備え、処理するデータを所定の単位に分割し、各データに対して、各プロセッサで並列に処理を行う構成において、命令キャッシュ容量を低減しながら所望のパフォーマンスを得る構成を提供する。

【解決手段】 並列処理プロセッサシステム203は、それぞれDSP301、命令キャッシュ302、画像用ローカルメモリ303を含む複数のプロセッサエレメント(PE1〜PE3)と、共有メモリ304とを備える。共有メモリには、DSPが実行するファームウェアが格納される。並列処理プロセッサシステムは、画像用ローカルメモリに処理対象の画像データを転送し、DSPにより画像処理を施す。キャッシュミスが発生した場合の命令キャッシュの更新は例えば、DSPがアクセスしたアドレスに対応する共有メモリの内容を命令キャッシュにコピーすることによって実現される。

(もっと読む)

画像描画装置

【課題】キャッシュ効率を向上させ描画速度の速い画像描画装置を提供する。

【解決手段】画面の横方向の直線状の絵を書くために、横方向一直線状にテクセルを取得する場合を考える。このとき、16x16ブロックのテクセルに割り振るキャッシュアドレスは、横方向の組のテクセルをグループとし、グループの横側に隣接するグループは、異なるキャッシュアドレス領域が割り当てられたグループとなるようにする。

(もっと読む)

1 - 20 / 118

[ Back to top ]