Fターム[5B060MB09]の内容

Fターム[5B060MB09]に分類される特許

1 - 20 / 52

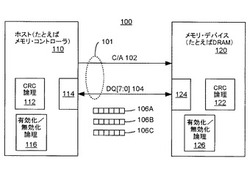

共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置

【課題】共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置を提供する。

【解決手段】メモリ・システム100は、ホスト110とメモリ・デバイス120との間でデータを転送するためにデータ・フレームを使用する。いくつかの場合には、システムは(別個のビット・レーンを介してではなく)データ・フレーム内で一つまたは複数のデータ・マスク・ビットも転送してもよい。システムは、データ・ビットおよびデータ・マスク・ビットをカバーするエラー・ビット・チェックサム(巡回冗長符号すなわちCRCのような)を生成してもよい。いくつかの実施形態では、データ・ビット、データ・マスク・ビットおよびチェックサム・ビットは共通フレームにおいて転送される。

(もっと読む)

プリント基板

【課題】各メモリ7、8に内蔵されたチップが、それぞれ2つであっても1つであっても、同一のプリント基板PCBを使用でき、かつ、アドレスデコーダメモリ間経路L1〜L4及びプロセッサアドレスデコーダ間経路L0を構成する経路切り替え用抵抗素子R2〜R6の配設箇所が少なく、アドレスデコーダメモリ間経路L1〜L4のSI解析工数が増加しない、プリント基板を提供する。

【解決手段】プロセッサアドレスデコーダ間経路L0は、第1MPU出力端子A23から第1アドレスデコーダ入力端子Aに指示信号を供給可能で経路切り替え用抵抗素子R4が実装可能な第1指示信号経路A23−Aと、端子A24から入力端子Bに指示信号を供給可能な第2指示信号経路A24−Bと、入力端子Aにアース信号Seを供給可能で経路切り替え用抵抗素子R6が実装可能な固定指示信号経路R6−Aとから成る。

(もっと読む)

スケーラブルメモリシステム

【課題】任意の個数のメモリデバイスをサポートできるメモリシステムアーキテクチャを提供する。

【解決手段】メモリシステムは直列接続された複数のメモリデバイスを有する。各メモリデバイスは、他のメモリデバイス及びメモリコントローラとの間用の直列入出力インターフェースを有し、メモリコントローラはビットストリームでコマンドを出し、ビットストリームはモジュラコマンドプロトコルに従う。コマンドはアドレス情報及びデバイスアドレスと共にオペレーションコードを含み、アドレッシングされたメモリデバイスだけがコマンドに作用する。データ出力ストローブ信号及びコマンド入力ストローブ信号がデータのタイプおよびデータの長さを識別するために、各出力データストリーム及び入力コマンドデータストリームと並列に供給される。モジュラコマンドプロトコルは性能改善のために各メモリデバイス内での同時動作のために使用される。

(もっと読む)

メモリコントローラアドレスおよびデータピンの多重化

【課題】メモリデバイスと通信するメモリコントローラを構成するためのシステムを提供する。

【解決手段】メモリコントローラは、複数のピンからなる第1のピンのセットを備え、各ピンはデータビットとアドレスビットとのうちの少なくとも一方に関連している。システムは、メモリコントローラの第1のピンのセットに接続されているプログラマブル論理ブロックを備える。プログラマブル論理ブロックは、第1のピンのセットの一部からなる第2のピンのセットを用い、メモリデバイスのサイズにしたがってメモリデバイスとメモリコントローラとの間のデータ転送をイネーブルする。第2のピンのセット以外のピンは、1つ以上の他のアプリケーションに利用可能である。

(もっと読む)

半導体集積回路及び制御方法

【課題】LSIの機能増加に伴い外部端子数が増加傾向にある。更に、回路の微細化が進み、パッケージサイズも小型化が進んでいる。このため、LSIの外部端子数の削減が求められている。

【解決手段】本発明は、複数の外部記憶デバイスから1つを選択して、実行プログラムをロードする半導体集積回路であって、複数の内蔵ヒューズ回路を備えるヒューズ部と、前記内蔵ヒューズ回路が示す値に応じて選択した外部記憶デバイスからの実行プログラムをロードする処理部と、を有する半導体集積回路である。

(もっと読む)

メモリコントローラ及び情報処理装置

【課題】端子を追加することなく確実にデータ転送を行うことが可能なメモリコントローラ、及び情報処理装置を提供すること。

【解決手段】メモリコントローラは、メモリから読み出されたリードデータを、メモリに入力される内部クロック信号を帰還した帰還クロック信号に同期して格納するレジスタ群と、レジスタ群にリードデータを取り込む際に、リードデータの格納位置を、帰還クロック信号に同期して指定するライトポインタと、レジスタ群からリードデータを取り出す際に、リードデータの取出位置を、内部クロック信号に同期して指定するリードポインタと、を含むFIFOメモリを備え、メモリに供給する内部クロック信号の一部をマスクし、リードポインタに対するライトポインタの動作タイミングを調整する。

(もっと読む)

半導体装置及びデータ処理システム

【課題】外部からのアクセスに対する高速な応答性を実現しながら外部からアクセスを受けるためのアドレス入力に割当てられる外部端子の数が少ない半導体装置を提供する。

【解決手段】自らのアドレス空間に保有するリソースを他の外部デバイスが直接アクセスできるようにするために、外部からのアクセスに必要なアドレス信号の一部を入力する外部端子303,304と、前記外部端子から入力されたアドレス情報の上位側を補完するための補完レジスタ401と、外部からアクセス可能なモードレジスタ400と、前記アドレス空間をアクセスするためのアドレス信号を前記外部端子からの入力情報、必要な補完情報及び前記モードレジスタのモード情報に基づく形態で生成するアドレス制御回路202とを、外部インタフェース回路に採用する。

(もっと読む)

異なるメモリ種類にアクセスする異なる速度での時分割多重化

【課題】 システムの性能、コスト、又は他の特徴を最適化し得ること。

【解決手段】 メモリコントローラは、時分割多重化バスの使用を通して異なる固有速度で実行中の異なる種類のメモリ装置にアクセスする。データは、1種類のメモリ装置にアクセスする場合にはある速度でバスを介して転送され、別の種類のメモリ装置にアクセスする場合には異なる速度で転送される。加えて、メモリコントローラは、制御情報(例えば、コマンド及びアドレス情報)を異なる種類のメモリ装置に異なる速度で提供し得、場合によっては、制御情報を共有バス上に時間多重化し得る。

(もっと読む)

メモリシステム及び半導体記憶装置

【課題】データ入力端子とデータ出力端子を分離し、スループットを向上させるとともに、端子数の増加を抑制できる半導体記憶装置及びメモリシステムを提供する。

【解決手段】少なくとも一つのライトデータ入力端子と、ライトデータ入力端子のN倍の数のリードデータ出力端子と、データ記憶部と、第1の周波数の信号に同期してデータ記憶部から読み出したリードデータをリードデータ出力端子から出力するデータ出力回路と、ライトデータ入力端子から入力したライトデータを第1の周波数のN倍の周波数のライトストローブ信号に同期して取り込み、前記データ記憶部へ送るデータ入力回路と、を備える。

(もっと読む)

車載カメラ装置

【課題】書き換え可能な不揮発性メモリを備える車載カメラ装置において、外部デバイスと接続された既存の信号線を有効に利用して不揮発性メモリのデータを書き換えるようにする。

【解決手段】車載カメラ装置1内のFPGA20は、操作部3に替えて既存の信号線2−1,2−2に接続されたメモリ書換装置4からの入力信号1,2にもとづき、不揮発性メモリ(SPIフラッシュメモリ)40のC信号、D信号、S信号を生成する記録信号生成部24を備える。不揮発性メモリ40は、これらC信号、D信号、S信号によって、それまで記録されているデータを書き換える。

(もっと読む)

デュアルチャネル動作中にアドレス/コントロール信号をインターリーブすることによるシングルチャネルとデュアルチャネルのハイブリッドDDRインターフェース方式

メモリ構造体が説明される。一実施形態では、メモリ構造体には、クロック信号を受け取り、単一のアドレス/コントロールバスを介して複数のメモリモジュールに結合されるように構成されたメモリコントローラが備わっている。メモリコントローラは、各メモリモジュール向けの別々のチップセレクト信号によって複数のメモリモジュールのそれぞれに結合する。メモリコントローラは、クロックによって与えられるタイミングに従ってインターリーブされるやり方で、メモリモジュールに対してアドレス/コントロールバスを介してコマンドを送出する。メモリコントローラは、1つのメモリモジュールに対するコマンド送出後の待機期間中に、別のメモリモジュールに対してコマンドを送出することができる。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】データ信号線の本数を増大させることなくデータ信号を差動信号として構成した半導体集積回路を提供する。

【解決手段】半導体集積回路は、2つのデータ入出力端子と、2つのデータ入出力端子を介してデータを入力するデータ入力回路と、2つのデータ入出力端子を介してデータを出力するデータ出力回路とを含み、データ入力回路及びデータ出力回路の一方の回路は、2つのデータ入出力端子を個々に独立した端子として用いて2つの単相信号を伝送し、データ入力回路及びデータ出力回路の他方の回路は、2つのデータ入出力端子を一対の端子として用いて一対の差動信号を伝送する。

(もっと読む)

ハイブリッドデータ、コード及びキャッシュ保存のためのNANDベースNOR及びNANDフラッシュ及びSRAM具備のワンチップ統合メモリシステム

【課題】ハイブリッドデータ、コード及びキャッシュ保存のためのNANDベースNOR 及びNANDフラッシュ及びSRAM具備のワンチップ統合メモリシステムの提供。

【解決手段】NANDフラッシュメモリ、NOR フラッシュメモリ及びSRAMを包含し、シングルチップ上に製造されるメモリである。NAND及びNOR メモリのいずれも同じNAND製造プロセスで製造される。これら三つのメモリは該シングルチップの同じアドレスバス、データバス、及びピンを共用する。該アドレスバスはコード、データ及びアドレスの双方向の受け取りと出力に供される。該データバスも双方向のデータの受け取り及び伝送に供される。一つの外部チップイネーブルピン及び一つの外部出力イネーブルピンがこれら三つのメモリに共用されることでシングルチップに必要なピン数を減らす。NAND及びNOR メモリはいずれもデュアル読み出しページバッファとデュアル書き込みページバッファを有し、ロード中読み出しとプログラム中書き込みの動作を行ない、これにより読み出しと書き込み動作を加速する。メモリマップ法が異なるメモリ、状態レジスタ、及びデュアル読み出しページバッファ又はデュアル書き込みページバッファの選択のために使用される。

(もっと読む)

半導体記憶装置およびメモリ制御システム

【課題】マイコンシステムにおいて制御しやすいロジック内蔵DRAMを提供する。

【解決手段】インタフェース部2は、アドレス信号ADD.で指定される領域が、ロジック制御領域である場合には、DRAM4とデータを授受する代わりに、レジスタ6とデータ授受を行なう。その際のデータ信号DATAは、レジスタ6に保持されるロジック回路8に対する制御コマンドや、処理のための入力データである。レジスタ6の保持内容に応じて、ロジック回路8は、たとえば、暗号処理や、画像処理等の、マイコンでは時間を要してしまう処理を実行する。処理結果はレジスタ6に保存され、DRAMに対する読出と同様のシーケンスで読出される。

(もっと読む)

メモリ制御回路

【課題】複数のSDRAMに対して、並列に個々のSDRAMに効率的にアクセスする。

【解決手段】複数個で構成されるSDRAMの個々のSDRAMに対してアクセス要求を行う複数のマスター101a、101bのSDRAMに対する書き込みまたは読み出し要求からコマンド発生回路102a、102bにより独立にSDRAMへのコマンドを生成し、コマンドアドレス多重回路104により一つのコマンドに多重する。多重後のコマンドを共通のコマンドとして各SDRAMに供給し、チップセレクト信号のみSDRAM毎に別々に制御することにより、複数のSDRAMに対して連続したアクセスを実現する。

(もっと読む)

ダブルデータレートDRAM書き込みの間に不使用のデータバイトをトライステートにするための方法、システム及び装置

【解決手段】

メモリインタフェース回路は、複数のデータバスドライバと、書き込みドライバマスク情報に動作可能に応答するにように適合させられる論理とを含む。必要に応じて、複数のバス書き込みドライバ及び論理は別個の集積回路内に実装されてよい。複数のバスドライバは書き込み動作に応答するように適合させられている。論理もまた、書き込みドライバマスク情報に基いて書き込み動作の間に複数のデータバスドライバのいずれか1つを選択的に無効にするように適合させられている。

(もっと読む)

メモリデバイスにおいてデータを反転させるための方法および装置

【課題】信号レベルの遷移数が多いことによるデータ転送を効率の低下を防止すること

【解決手段】前記現在のワードはN個のビットを有する前のワードと比較され、低レベル値から高レベル値、またはその逆の高レベル値から低レベル値へのビットの遷移の数を識別する。遷移の数がN/2よりも多ければ、現在ビットを反転する。反転の有無を表示するためにエクストラビットをデータバイトに付随させなくてもよいように、反転ビットを送るのに通常は書き込み動作中には使用されないデータマスクピンを活用する。

(もっと読む)

メモリモジュール及びその使用方法、並びにメモリシステム

【課題】データ入出力パッド13の終端抵抗と終端抵抗のオンオフを制御する信号を入力するための終端抵抗制御パッド14とを備えた同期式メモリチップを多ランク搭載した多ランクメモリモジュールにおいて、メモリモジュールに設けた終端抵抗制御(ODT)端子の数より、ランクの数のほうが大きい場合においても、内蔵終端抵抗を用いて、高速動作を可能にする。

【解決手段】モジュール基板8上のデータバス19とデータ入出力パッド13との配線の長さが長いメモリチップ12の終端抵抗制御パッド14を、終端抵抗制御配線18、21に接続し、ODT端子から終端抵抗のオンオフを制御し、モジュール基板上のデータバス19とデータ入出力パッド13との配線の長さが短いメモリチップ11の終端抵抗制御パッドについて終端抵抗をオンさせるように固定電位20に接続する。

(もっと読む)

メモリ制御装置

【課題】信号線の接続本数の最小限化と高スループット化を両立したメモリ制御装置を提供すること。

【解決手段】アドレスとデータを時分割で共有する複数のメモリを制御するメモリ制御装置は、第1のメモリのデータバス幅以上のアドレスを第2のメモリのデータバスビットで表現し、第2のメモリのデータバス幅以上のアドレスを第1のメモリのデータバスビットで表現して、複数のメモリに同時アクセスする。

(もっと読む)

メモリ制御回路

【課題】メモリに対するアクセスを高速にするとともに実装面積の増大を抑制可能なメモリ制御回路を提供。

【解決手段】シリアルアクセスが可能で、シリアルアクセスで使用される端子を用いてパラレルアクセスが可能なメモリにアクセスするための第1アクセスデータが入力され、第1アクセスデータをシリアルで出力するシリアルデータ処理回路と、第2アクセスデータが入力され、第2アクセスデータをパラレルで出力するパラレルデータ処理回路と、シリアルアクセスを指示するための第1指示信号が入力されている場合に、シリアルアクセスが可能であるメモリに、シリアルデータ処理回路からの第1アクセスデータをシリアルで出力し、パラレルアクセスを指示するための第2指示信号が入力されている場合に、パラレルアクセスが可能であるメモリに、パラレルデータ処理回路からの第2アクセスデータをパラレルで出力する選択回路とを備える。

(もっと読む)

1 - 20 / 52

[ Back to top ]