Fターム[5B061RR02]の内容

Fターム[5B061RR02]に分類される特許

1 - 20 / 82

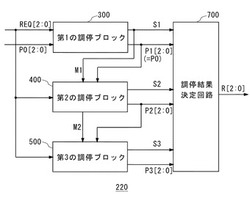

調停回路及び半導体装置

【課題】複数の要求装置の優先順位を動的に可変にでき、処理効率を高めると共に、該複数の要求装置の総数が変化した場合に柔軟に対応可能にする。

【解決手段】調停要求信号REQは各調停ブロックに入力される。各調停ブロックは、調停結果と優先信号を調停結果決定回路に出力する。第1の調停ブロック300は、さらに、優先順位パターンP0が入力され、第1の調停結果P1と第1のマスク信号M1を第2の調停ブロック400に出力する。第2の調停ブロック400は、さらに、第1の調停結果P1が入力され、第2の調停結果P2と第2のマスク信号M2を第3の調停ブロック500に出力する。第3の調停ブロック500は、さらに、第2の調停結果P2が入力される。調停結果決定回路700は、各調停ブロックからの信号に基づいて調停結果Rを選択する。

(もっと読む)

信号転送回路

【課題】プロトコルに従ってアクセスを行うアービタとバスマスタとの間の入出力信号のタイミングの制約を改善することができる信号転送回路を提供する。

【解決手段】バスマスタから入力されたメモリへのアクセス要求をアービタに中継する際に、入力されるアクセス要求入力信号およびメモリアドレス入力信号のタイミングを整えたアクセス要求出力信号およびメモリアドレス出力信号を出力すると共に、アービタから入力されるアクセス許可入力信号に先行して、アクセス許可出力信号をバスマスタに出力する制御信号転送部と、データをバスマスタまたはアービタに中継する際に、入力されるそれぞれのデータ入力信号のタイミングを整えたそれぞれのデータ出力信号を、バスマスタまたはアービタに出力すると共に、アービタから入力されるデータ有効期間入力信号のタイミングを整えたデータ有効期間出力信号をバスマスタに出力するデータ信号転送部と、を備える。

(もっと読む)

クロックゲーティング回路およびバスシステム

【課題】トランザクションを単位として扱うバスシステムにおいて消費電力を低減する。

【解決手段】クロックゲーティング回路は、クロックイネーブル信号生成部とマスククロック生成部とを備える。クロックイネーブル信号生成部は、バスシステムを複数のリージョンに分割した各々においてアウトスタンディングトランザクションの数を計数することにより複数のリージョンの各々のためのクロックイネーブル信号を生成する。マスククロック生成部は、複数のリージョンの各々のためのクロックイネーブル信号によってクロックをマスクしてマスククロックを生成する。

(もっと読む)

双方向シリアルバスの通信制御方法および双方向シリアルバススイッチ

【課題】双方向シリアル信号を単方向信号に変換し所定のタイミングで方向を切り替えることができる双方向シリアルバスの通信制御方法および双方向シリアルバススイッチを提供する。

【解決手段】双方向シリアルバススイッチ(100)は、マスタデバイス(101)とスレーブデバイス(102)との間の双方向信号を単方向信号に変換するスイッチ(103,104)と、マスタデバイスが出力する信号に従って単方向信号の方向を決定しスイッチを制御するデコード部(105)と、を有する。

(もっと読む)

バススイッチ装置及びバススイッチシステム及びバススイッチ方法及びプログラム

【課題】マスター装置からスレーブ装置に対する操作要求と操作情報とを入力して、操作が要求されたスレーブ装置に操作要求と操作情報とを出力するバススイッチがあったが、スレーブ装置が増加すると、マスター装置からスレーブ装置へ出力する操作情報のトラフィックに対応できなかった。

【解決手段】バススイッチ101は、複数の操作情報チャネルに出力された操作情報を、操作が要求されたスレーブ装置に対応したチャネル選択回路に入力させるリクエスト信号とチャネル選択信号とを生成する選択信号生成回路121と、選択信号生成回路121が生成したリクエスト信号をもとに、上記スレーブ装置に対応したチャネル選択回路を選択する選択回路部130とを備え、選択されたチャネル選択回路が、複数の操作情報チャネルのうち、チャネル選択信号が表す操作情報チャネルから操作情報を入力する。

(もっと読む)

半導体集積回路および割り込み生成方法

【課題】消費電力を低減すると共に、必要とされる対象処理の遅延を低減することができる半導体集積回路および割り込み生成方法の提供を図る。

【解決手段】レジスタ1を含む回路ブロック100と、前記レジスタの値を読み出して出力するレジスタ値読み出し回路400と、前記レジスタの値を前記レジスタ値読み出し回路から受け取り、予め設定された期待値と前記レジスタ値を比較し、前記比較の結果に基づいて割り込み要求を生成する割り込み生成回路500と、を有する。

(もっと読む)

データ転送装置及びデータ転送方法

【課題】データ転送をより柔軟に行えるデータ転送装置及びデータ転送方法を提供する。

【解決手段】転送データサイズの上限値を設定可能なレジスタと、この上限値と外部から送られた転送サイズとを比較し、この転送サイズがレジスタ設定値より大きい場合、この転送サイズを減少させる機構とを備えるデータ転送装置。また、レジスタに設定値を設定し、転送データサイズの上限値を設定し、この上限値と外部から送られた転送サイズとを比較し、この転送サイズが前記設定値より大きい場合、この転送サイズを減少させるデータ転送方法。

(もっと読む)

データ転送装置

【課題】バイト単位のデータ転送を実現しようとするとFIFO等の使用するハードウェアの規模が大きくなる。

【解決手段】ライト用バイトイネーブル保持回路10は、FIFO40の最新のライトアドレスに書き込まれているデータのバイトイネーブルを保持し、リード用バイトイネーブル保持回路20は、1タイミング前のライトデータのバイトイネーブルまたは該バイトイネーブルと1タイミング前の自保持内容との論理和または1タイミング前の自保持内容を保持する。バイト読出し判定フラグ50は、リードデータのバイトイネーブルを解読してFIFOの1ワード分の全バイト読出しであるか否かを示す。否のとき、セレクタ503は、回路20の保持内容、全バイト読出しであるときは回路10が保持しているバイトイネーブルを選択して、リードデータのバイトイネーブルとする。

(もっと読む)

集積回路装置、検証装置及び検証方法

【課題】集積回路装置が仕様通りとなっているかの検証の容易化を図る。

【解決手段】集積回路装置10は、マスターモジュール11と、マスターモジュール11に接続されたインターコネクト12と、インターコネクト12によってマスターモジュール11の接続先とされるスレーブモジュール13を含む。集積回路装置10は更に、そのスレーブモジュール13に対してインターコネクト12から送信されてくる読み出し命令信号を受信する固定値応答回路14を含む。インターコネクト12から読み出し命令信号を受信した固定値応答回路14は、インターコネクト12によってマスターモジュール11の接続先とされたスレーブモジュール13固有の固定値を、インターコネクト12に送信する。この固定値に基づき、接続先が仕様通りか否かを検証する。

(もっと読む)

デイジーチェーンカスケードデバイス

【課題】デバイスをデイジーチェーンカスケード配列でシリアルに連結する。

【解決手段】デバイスはデイジーチェーンカスケード配列で連結され、第1デバイスの出力部は、データ、アドレス及びコマンド情報等の情報並びに制御信号を第2デバイスに第1デバイスから転送するように、デイジーチェーンカスケードの後方にある第2デバイスの入力部に連結されている。デイジーチェーンで連結されたデバイスは、シリアル入力部SIとシリアル出力部SOとを備える。情報がデバイスにSIを通じて入力され、該情報がデバイスからSOを通じて出力される。デイジーチェーンカスケードの前方のデバイスのSOは、デイジーチェーンカスケードの後方のデバイスのSIに連結されている。前方のデバイスにSIを通じて入力された情報は、該デバイスのSOを通じて出力される。該情報は次いで、後方のデバイスのSIに転送される。

(もっと読む)

バスモジュール及びバスシステム

【課題】システムバスを介してデータ授受を行う場合に、異常箇所の検出を容易に行うことができるバスモジュール及びバスシステムを得る。

【解決手段】システムバス20に接続されたモジュール1、2、3、nは、バスマスタとして、システムバス20へのデータ送信時には、出力アドレスレジスタ103にアドレスを、出力データレジスタ105にデータをそれぞれラッチするとともに、システムバス20に出力したアドレスを入力アドレスレジスタ104に取り込み、出力アドレスレジスタ103の内容と比較し、システムバス20に出力したデータを入力データレジスタ106に取り込み、出力データレジスタ105の内容と比較し、これらの比較で、一致しない場合に自バスモジュールのエラーを判定する。

(もっと読む)

複数のプロトコルのバスを有するバスシステム及びそれに使用されるバススイッチングデバイス

【課題】複数のプロトコルのバスシステムが混在するバスシステムであって,バスの配線量を抑制したバスシステムと,それに使用されるバススイッチデバイスを提供する。

【解決手段】第1のバスシステムと,第2のバスシステムと,第1のバス配線の第1及び第2の部分バス配線間または,第2のバス配線の第3及び第4の部分バス配線間を,接続する共通バス配線と,第1の部分バス配線と共通バス配線との間と第3の部分バス配線と共通バス配線との間とに設けられた第1のバススイッチデバイスと,第2の部分バス配線と共通バス配線との間と第4の部分バス配線と共通バス配線との間とに設けられた第2のバススイッチデバイスとを有し,バススイッチデバイスは,部分バス配線の電圧状態をそれぞれ監視し,メッセージが送信されていない電圧状態を検出した時に,第3及び第4の部分バス配線と前記共通バス配線とを接続する第2の接続状態にそれぞれ切り替える。

(もっと読む)

データ処理システム

【課題】 データ処理システムの消費電力をきめ細かく制御する。

【解決手段】 複数のマスターの各々は、データの転送要求とともにデータの転送速度を示すスピードグレード信号を出力する。調停回路は、複数のマスターからの転送要求およびスピードグレード信号を調停する。クロックイネーブル生成回路は、調停回路により調停されたスピードグレード信号に応じて、有効期間の比率が異なるクロックイネーブル信号を生成する。スレーブは、クロックイネーブル信号が有効なときにクロック信号を受けて動作し、調停回路により調停された転送要求に応じてデータを転送する。これにより、スレーブを動作させるクロック信号の周波数を転送要求毎に変更でき、スレーブの電力のきめ細かな制御を容易に実施できる。

(もっと読む)

半導体集積回路及び半導体集積回路におけるデータ転送の制御方法

【課題】バス間を複数のバスブリッジで接続する構成の半導体集積回路において、トランザクションの順番の入れ替わりを防ぎ、データの転送性能を向上させる。

【解決手段】1以上のマスタデバイスが接続される第1のバスと、1以上のスレーブデバイスが接続される第2のバスと、第1のバスと第2のバスとを接続する複数のデータ転送経路とを備えた半導体集積回路であって、第1のバスは、第1のマスタデバイスから第1のスレーブデバイスへのデータ転送経路を、複数のデータ転送経路から選択する経路選択モジュールを含み、経路選択モジュールは、第1のマスタデバイスから第1のスレーブデバイスへのデータ転送のトランザクションが発生した場合、第1のマスタデバイスから第1のスレーブデバイスへの過去のデータ転送のトランザクションの状態に応じて、現に発生したトランザクションのデータ転送経路を選択する。

(もっと読む)

データ転送装置

【課題】PCI−eバスインタフェースを具備するチャネルハードウェアをメインフレームに搭載する際、システム装置内の大幅な変更無しにスループットの向上が実現できるデータ転送装置を提供する。

【解決手段】チャネルから主記憶を参照する場合に、実際の主記憶参照と並行してプリフェッチ動作を行い、参照の対象となるデータを先行してキャッシュに登録する。本発明によれば、PCI−eバスインタフェースを具備するチャネルハードウェアをメインフレームに搭載する際、データを先行してキャッシュに登録することでデータ転送のスループット低下を防止することができ、且つ主記憶内のデータ更新を反映することが可能なデータ転送装置を提供できる。

(もっと読む)

共通クロック方式の同期型シリアル転送回路

【課題】シリアルクロックの動作周波数が上限に達していても、新たなシリアルデータ信号線路を追加することなく、転送速度のさらなる高速化が可能な、共通クロック方式のシリアル転送回路を提供する。

【解決手段】シリアルデータ信号を伝送する線路として、従来のシリアルデータ信号線路に加えて、シリアルクロック信号を伝送する線路をも利用する。このとき、シリアルクロック信号を伝送する線路のインピーダンスを制御することによって、シリアルデータ信号の一部を表現する。

(もっと読む)

ダイレクトメモリアクセスシステム及びその制御方法

【課題】高機能かつ高性能のダイレクトメモリアクセス転送を、CPUに対する負荷を増大させることなく、かつ、回路規模を増大することなく実現する。

【解決手段】システムは、ダイレクトメモリアクセス部とプロセッサ部とを有する。ここで、プロセッサ部は、メモリと、メモリから命令を読み出して実行することで、ダイレクトメモリアクセス部が実行する命令を当該ダイレクトメモリアクセス部に書き込むプロセッサとを備える。また、ダイレクトメモリアクセス部は、複数のプログラムカウンタと、複数のプログラムカウンタを順に選択する選択手段と、プロセッサによって書き込まれた命令を保持する命令保持手段と、選択手段で選択されたプログラムカウンタにより示される命令保持手段のアドレスに格納されている命令を出力する出力手段と、出力手段によって出力される命令に応じてダイレクトメモリアクセスによるデータ転送を実行する実行手段とを備える。

(もっと読む)

計算機装置及びその制御方法

【課題】長距離及び高周波数伝送が必要な場合に、振幅が減衰した信号とノイズを区別し、ノイズによる誤動作を防ぐ。

【解決手段】計算機モジュール110及びI/Oモジュール120の中継バッファ600,601,602,603は、それぞれPCIeインターフェース161,162の信号振幅を判断して信号とノイズを区別し、出力信号のON/OFFを制御するノイズフィルタ回路を有する。I/O HUB300及びPCIeスイッチ400は、通信モードに応じて、中継バッファのノイズフィルタ回路の有効/無効を切り替え、通信速度が高速の時にはノイズフィルタ回路を無効にする。ケーブル抜去検出回路115,125は、PCIeケーブル151の抜去をI/O HUB300及びPCIeスイッチ400に通知し、PCIのグリッチによるノイズによる誤作動を抑止する。

(もっと読む)

調停装置、バスアクセス調停プログラムおよびバスアクセス調停方法

【課題】共通のバスへのデータ転送の転送効率を向上させることを課題とする。

【解決手段】調停装置は、複数のDSP間における共通のバスへのアクセス権の切替時に要する切替時間を保持し、切替時間と、DSPの温度が所定閾値以上である場合に受信する複数のDSPの温度情報とに基づいて、複数のDSPそれぞれの位相シフト値を求める。そして、調停装置は、発振器によって送出された基準クロックと、求められた位相シフト値とを用いて、複数のDSPごとに異なるクロックを生成して出力する。

(もっと読む)

データ転送装置、データ転送方法及びデータ転送プログラム

【課題】DMA転送装置において、任意のタイミングに転送情報を切り替え可能とすることを目的とする。

【解決手段】転送周期決定回路120は、所定の周期を示す周期信号40を生成する。切り替え回路130は、周期信号40に同期して、カウンタ値をインクリメントする。また、切り替え回路130は、カウンタ値をオフセット値43として、固定アドレス記憶部140が記憶した固定アドレス41とオフセット値43とからアドレス44を計算する。DMA転送チャネル110は、切り替え回路130のRAMにおけるアドレス44が示す位置から転送情報42を取得する。そして、DMA転送チャネル110は、取得した転送情報42に従いデータを転送する。

(もっと読む)

1 - 20 / 82

[ Back to top ]