Fターム[5B062AA05]の内容

マイクロコンピュータ (2,258) | 目的、効果 (507) | 消費電力の低減、節電 (153)

Fターム[5B062AA05]に分類される特許

1 - 20 / 153

電力の島を使用した集積回路での電力の管理

半導体集積回路の製造方法

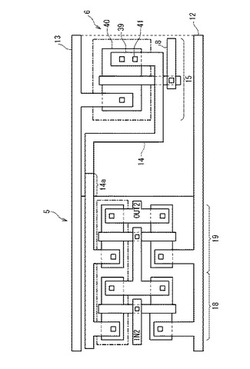

【課題】常時動作領域と電源遮断可能領域とが混在する半導体集積回路を提供する。

【解決手段】半導体基板に設けられ、複数の基本セル(10)の配置が可能なセル配置領域と、空間的に前記セル配置領域と重なって設けられた基本電源配線(11)と、前記基本電源配線(11)から前記セル配置領域への電源供給を停止するスイッチセル(6)と、前記スイッチセル(6)に隣接して前記セル配置領域に配置され、前記スイッチセル(6)が前記セル配置領域への電源供給を停止した場合においても、前記スイッチセル(6)から電源供給を受ける常時動作セル(5)とを具備する。

(もっと読む)

IC出力ポート切換制御装置

【課題】電源を省電力化することができるIC出力ポート制御装置を提供する。

【解決手段】ワイヤレスキーシステムの照合ECU4は、自身のメモリに記憶されたプログラムにて所定周期で動作するソフトウェア制御部19と、自身に元から備わるPWMリソースとを有する。照合ECU4のスリープ中、車両受信機が受信待機動作をとるパルスP4の1周期前のパルスP3で電源ポート11をソフトウェア制御からPWM制御に変更することにより、電源ポート11をPWM制御に切り換える。このため、PWM制御のパルスPxがHiレベルに立ち上がってからの時間が電源安定待ち時間Tsとして車両受信機に供給される。

(もっと読む)

情報処理装置、データ復帰方法

【課題】製造プロセスの影響を抑制してスリープ時の消費電力を低減できる情報処理装置を提供すること。

【解決手段】プログラムを実行する第1の動作モード中に作業用記憶手段に作成されたデータを第2の動作モード中に保持する退避データ記憶手段を有する情報処理装置100であって、第2の動作モードの動作クロックと、第2の動作モードの動作クロックよりも大きい第1の動作モードの動作クロックを生成するクロック生成手段19,20と、第2の動作モードから復帰する際、前記クロック生成手段が第1の動作モードの動作クロックに上昇させる前に、当該情報処理装置の状態を示す情報処理装置ステータスデータを前記退避データ記憶手段から作業用記憶手段に復帰させる第1のデータ復帰手段41と、前記クロック生成手段が第1の動作モードの動作クロックに上昇させた後、第1の動作モード中に作成されたデータを退避データ記憶手段から作業用記憶手段に復帰させる第2のデータ復帰手段46と、を有することを特徴とする。

(もっと読む)

プロセッサインストラクションの発行の絞り込み

【課題】選択された問題のあるインストラクションの発行を絞り込むことにより電力消費を減少するためのシステム及び方法を提供する。

【解決手段】プロセッサ内の電力スロットルユニットは、高電力消費推定値に基づいて選出される関連インストラクション形式に対するインストラクション発行カウントを維持する。電力スロットルユニットは、所与のインストラクション発行カウントが所与のスレッシュホールドを越えることを決定する。それに応答して、電力スロットルユニットは、各発行レートを制限するための所与のインストラクション形式を選択する。電力スロットルユニットは、その選択された所与のインストラクション形式の各々に対する発行レートを選出し、そしてその関連発行レートを、選出された発行レートに制限する。所与のインストラクション形式及び関連発行レート限界の選択は、プログラム可能である。

(もっと読む)

半導体管理システム及び半導体管理方法

【課題】処理の優先度を考慮して印加電圧を制御することにより、半導体装置の消費電力を低下させる。

【解決手段】上位・下位分割器6が、正常に動作するために必要な電圧である正常動作電圧が低い演算器ほど、優先度の高い処理を割り当てる。電源装置2は、正常動作電圧の低さの順位が所定の順位以内の演算器に対しては、印加電圧を当該演算器の正常動作電圧以上に維持し、他の演算器に対しては、所定の場合に、印加電圧を当該演算器の正常動作電圧未満にして、優先度の高い処理を正確に実行することを保証しながら、半導体装置1の消費電力の低減を図る。

(もっと読む)

半導体装置および半導体装置の制御方法並びに半導体装置の設計支援方法

【課題】本発明の課題は、組み込みシステムのアーキテクチャに左右されることなく、DVFSの実行に必要なサイクル数を容易に取得することである。

【解決手段】ファームウェア(21)は、サイクル数概算ルーチン(213)と、動作電圧・周波数算出ルーチン(213)とを有する。サイクル数概算ルーチンは、サイクル数概算関数を備える。サイクル数概算関数は、ユーザ回路(6)の処理内容を決定づける属性パラメータの入力でタスクのサイクル数を概算する。動作電圧・周波数算出ルーチンは、サイクル数概算ルーチンの実行によって得られたサイクル数に基づいて、ユーザ回路(6)の目標動作電圧・周波数を算出する。

(もっと読む)

車載用ECU

【課題】内部のマイコンの動作不要時における消費電力を最小限に抑えた車載用ECUを得る。

【解決手段】車載用ECU10は、間欠動作モード設定時において、マイコン1の動作不要時には電源入力部VCCへの動作電源V4の供給を完全に停止させている。マイコン1は、間欠動作モードを指示するセット状態の判別用データCDを書込む第1の書込み処理、及び通常モードを指示するクリア状態の判別用データCDを書込む第2の書込み処理を共に内部の不揮発性RAM15に対する個別書込み動作によって行っている。また、不揮発性RAM15における判別用データCDの格納ブロックに対する一括消去動作を、マイコン1が通常モード設定時の定周期処理として実行する。

(もっと読む)

半導体装置

【課題】スタンバイ状態時にSRAMにデータを保持できる電圧が与えられている場合に、パワーオンリセットがかからないようにすることができる半導体装置を提供する。

【解決手段】CPU5は、スタンバイ状態に遷移することを通知する。電源制御回路11は、スタンバイ状態時に、SRAM4における電力消費を低減させる。POR回路2は、外部電源電圧の値と、現在の状態がスタンバイ状態であるかに応じて、パワーオンリセット信号の活性化を制御する。

(もっと読む)

演算処置装置およびマイクロコンピュータ

【課題】システム処理とフィルタ処理の双方の負荷を軽くすることができ、消費電力の向上や性能の向上を図ることが可能な技術を提供する。

【解決手段】デジタル・シグナル・プロセッサDSPにおいて、プログラム・メモリPM、プログラム・カウンタPC、制御論理回路CLを有し、各命令のビット・フィールド内には、命令停止フラグ情報(TRIG_WAIT)とビット・フィールド情報(TRIG_WHAT)とを持つ。そして、制御論理回路CLは、TRIG_WAITがクリアされている命令はそのまま実行し、次の命令処理に進み、TRIG_WAITがセットされている命令は、TRIG_WHATに対応する実行再開トリガ条件が成立していなければその実行を行わずに停止し、TRIG_WHATに対応する実行再開トリガ条件が成立していればその実行を行い、次の命令処理に進む、ように制御する。

(もっと読む)

マイクロコンピュータ

【課題】リソースでの無駄な消費電力を削減することができるマイクロコンピュータを提供することを目的とする。

【解決手段】外部から電源を供給されるマイクロコンピュータにおいて,それぞれの所定の機能を有し,外部から供給される前記電源の起動時に電源が供給されない複数のリソースと,前記複数のリソースにバスを介して接続され,前記リソースに前記バスを介してアクセス信号を供給する制御ユニットと,前記複数のリソースにそれぞれ設けられ,電源起動信号に応答して外部から供給される前記電源から対応するリソースにリソース内電源を供給する複数のリソース内電源供給部と,前記複数のリソースにそれぞれ設けられ,前記バスを介して供給されるアクセス信号が対応するリソース宛か否かを検知し,前記アクセス信号が対応するリソース宛の場合に前記電源起動信号を対応するリソース内電源供給部に出力できる電源制御部とを有する。

(もっと読む)

マイクロコンピュータおよびフィールド機器

【課題】マイクロコンピュータの回路規模の単純化を図りつつ、消費電力を低減させることを目的とする。

【解決手段】本発明のマイクロコンピュータは、信号処理を行う複数の機能ブロック4を有するマイクロコンピュータ1であって、クロックCLKを生成するクロック生成部3と、機能ブロック4のうち1つの機能ブロック4−1に備えられ、他の機能ブロック4が使用可能な共通レジスタ13に入力または出力されるデータをクロックCLKの供給が停止されたときにも保持する出力データ保持部14および入力データ保持部15と、各機能ブロック4のうち動作を行う機能ブロック4のみにクロックCLKを供給するようにスイッチ制御を行うコントロールブロック2と、を備えている。

(もっと読む)

半導体集積回路及び半導体集積回路の動作制御方法

【課題】温度が高くなりすぎたりあるいは低くなりすぎたりする発振状態となって、半導体集積回路が誤動作、動作停止等することを防止する。

【解決手段】実施形態によれば、半導体集積回路1は、回路部の温度又は動作速度に基づいて、温度が安定するように、回路部の制御パラメータを調整して、フィードバック制御を実行する制御部と、温度の時系列データである第1の履歴データと、制御パラメータの時系列データである第2の履歴データとを含む履歴データを格納する履歴レジスタ17と、履歴データからフィードバック制御の有効性を判定する有効性判定部24とを有する。

(もっと読む)

異種計算機システム動作方法

【課題】異種計算機システムを動作させる方法を提供する。

【解決手段】1つ以上の高性能プロセッサ620と、高性能プロセッサ620のソフトウェアのタスク実行を支援するプロセッサ支援論理回路6410と、高性能プロセッサ620より少電力なハイパーバイザプロセッサ610を有し、ハイパーバイザプロセッサ610は、自身が処理するのに十分な処理能力を有するソフトウェアのタスクを実行し、高性能プロセッサ620を電力節約状態にするか、又は高性能プロセッサ620を電力節約状態から抜け出させて、自身が処理するのに不十分な処理能力を有するソフトウェアのタスクを実行させるか、又は高性能プロセッサ620とハイパーバイザプロセッサ610とが全てのプロセッサの結合された処理能力を必要とするソフトウェアのタスクを同時に実行する。

(もっと読む)

パルス計測方法およびその装置

【課題】パルス信号の長さに依存することなく、MCUコアの消費電力を大幅に削減することを可能とする低消費電力パルス計測方法及びその装置の提供。

【解決手段】信号状態検出回路と、タイマ回路と、パルスカウントプログラムが記憶された記憶装置と、休止モード及び動作モードを有する中央処理装置と、を備えるマイクロコントローラ装置を用い、信号状態検出回路がパルスの立上りを検出すると起動モードに移行させる第1ステップと、立上り時チャタリングガードタイムの経過後、信号状態検出回路に対し設定をした後、休止モードに移行する第2ステップと、信号状態検出回路がパルスの立下りを検出すると起動モードに移行させる第3ステップと、立下り時チャタリングガードタイムの経過後、信号状態検出回路に対し設定をした後、休止モードに移行する第4ステップと、第1〜第4ステップを繰り返し実行する第5ステップと、を有するパルス計測方法及びその装置。

(もっと読む)

マイクロコンピュータ

【課題】アプリケーションプログラムの完成前に、システム全体の電源回路の最適化が可能なマイクロコンピュータを提供すること。

【解決手段】本発明に係るマイクロコンピュータ100は、CPU101と、CPU101に接続されたバス107と、バス107に接続される通常動作モードと、バス107と遮断される擬似動作モードと、を備える機能ブロック103A〜103Cと、通常動作モードと前記擬似動作モードとのいずれかを選択するための制御信号を出力する選択回路102と、を備え、機能ブロック103A〜103Cが、擬似動作モードにおいて消費電流を生成する擬似動作回路105A〜105Cと、を備えるものである。

(もっと読む)

半導体集積回路装置およびその制御方法

【課題】確実にスリープモードに設定することが可能な半導体集積回路装置およびその制御方法を提供する。

【解決手段】まず、第1の値に設定された第1のイネーブル信号を演算部に供給し、演算部を通常動作モードより消費電力が小さいスリープモードに設定する。次に、第1の期間経過後に第1のイネーブル信号が第1の値であるか否かを判定し、第1の値である場合、第2の値に設定された第2のイネーブル信号をメモリに供給し、メモリをスリープモードに設定する。次に、第2の期間経過後に第2のイネーブル信号が第2の値であるか否かを判定し、第2の値である場合、第3の値に設定された第3のイネーブル信号をアナログ回路に供給し、アナログ回路をスリープモードに設定する。次に、第3の期間経過後に第3のイネーブル信号が第3の値であるか否かを判定し、第3の値である場合、第4の値に設定された第4のイネーブル信号をレギュレータに供給し、レギュレータをスリープモードに設定する。

(もっと読む)

ディジタル・パワー・スロットルを備えたマイクロプロセッサ

【課題】 プロセッサ内の電力消費を調整するためのディジタルベースのメカニズムを提供する。

【解決手段】 本発明は、プロセッサ内の電力消費を調整するためのディジタルベースのメカニズムを提供する。このプロセッサは、1つまたは複数の機能ユニットと、プロセッサの機能ユニットの活動状態を監視して、プロセッサの電力消費を推定するディジタル・スロットルとを含む。このディジタル・スロットルの一実施形態は、1つまたは複数のゲート・ユニットと、1つの監視回路(320)と、1つのスロットル回路(330)とを含む。各ゲート・ユニットは、プロセッサの機能ユニットへの電力送付を制御し、その関連機能ユニットの活動状態を示す信号を出力する。監視回路は、信号から推定電力消費レベルを決定し、その推定電力消費としきい電力レベルを比較する。推定電力消費レベルがしきい電力レベルを超える場合、スロットル回路はプロセッサ内の命令フローを調整する。

(もっと読む)

非同期式回路

【課題】2相式の非同期式回路の処理速度を向上させると共に、回路規模の増大を抑制する。

【解決手段】非同期式回路200は、段階的に接続された複数の回路ブロックを備え、夫々の回路ブロックが、演算回路と、該演算回路に対して2相式制御を行う制御回路を有する。モード制御回路230は、1段目の回路ブロックに対して、該回路ブロックが休止相を開始したときに初期化を開始し、最下段の回路ブロックが休止相を開始したときに稼働相を開始し、2段目の回路ブロックに対して、1段目の回路ブロックが初期化を開始したときに稼働相を開始し、1段目の回路ブロックが稼働相を開始したときに初期化を開始するように制御を行う。

(もっと読む)

クリティカルパスに基づく解析のための性能モニタリングアーキテクチャ強化

【課題】マイクロアーキテクチャの性能をモニタリングし、そのモニタリングされた性能に基づいてマイクロアーキテクチャをチューニングする方法及び装置を提供する。

【解決手段】シミュレーション、解析上の推論、リタイアメントプッシュアウト測定、全体実行時間、およびインスタンス当たりのイベントコストを決定する他の方法によって性能がモニタリングされる。インスタンス当たりのイベントコストに基づき、マイクロアーキテクチャおよび/または実行ソフトウェアは、性能を強化すべくチューニングされる。

(もっと読む)

1 - 20 / 153

[ Back to top ]