Fターム[5B062EE05]の内容

マイクロコンピュータ (2,258) | チップ外部との入出力 (243) | 直列入出力 (14)

Fターム[5B062EE05]に分類される特許

1 - 14 / 14

マイクロコンピュータ及びマルチマイクロコンピュータシステム

【課題】、一のマイクロコンピュータを介する他のマイクロコンピュータのオンボード書込みを行うためのソフトウェア開発の負担軽減とシステムコストの低減とに寄与する。

【解決手段】外部インタフェースユニットに接続する外部端子を、別の外部インタフェースユニットに接続する外部端子に選択的にスルーさせるとともに、当該外部インタフェースユニットのインタフェース機能を抑止する、バイパス生成部(23)をマイクロコンピュータ(1)に採用する。マルチマイクロコンピュータシステムにそのマイクロコンピュータを第1のマイクロコンピュータとして採用し、第1のマイクロコンピュータにおける一の外部インタフェースユニットに書き込みホスト装置に接続するインタフェースコネクタを結合し、当該第1のマイクロコンピュータにおける他の外部インタフェースユニットを別の第2のマイクロコンピュータに接続する。

(もっと読む)

電子システム

【課題】マイコンが生成するPWMパルスの周波数精度を向上する「電子システム」を提供する。

【解決手段】サブマイコン21は、低精度発振子22が生成する動作クロックを、設定された分周比nで分周した周期を持つPWMパルスを出力する。高精度発振子12が生成する動作クロックで動作するメインマイコン11は、サブマイコン21が出力するPWMパルスの周期Tprを計測し、計測した周期Tprと現在サブマイコン21に設定されている分周比nとより、サブマイコン21の動作クロックの真の周期Tsrを算出する。そして、算出したサブマイコン21の動作クロックの真の周期Tsrより、PWMパルスの周期がPWMパルスの所望周期Tptに最も近くなる分周比nを求め、マイコン間通信を用いてサブマイコン21に設定する。

(もっと読む)

マイクロコンピュータ及びデータ処理システム

【課題】マイクロコンピュータにおいてメモリアクセスコマンドの生成などの点でシリアルアクセスメモリに対するアクセスのオーバーヘッドを減らす。

【解決手段】 CPUが出力するアクセス要求に含まれるアドレス及びコマンドに基づいて、シリアルフラッシュメモリに、チップ選択信号及びクロック信号を供給し、前記クロック信号に同期してメモリアドレス及びメモリコマンドを出力してシリアルアクセスメモリのアクセス制御を行うシリアルメモリインタフェースコントローラ(60)をマイクロコンピュータに搭載し、このシリアルメモリインタフェースコントローラには、前記アクセス要求に応答するメモリアドレス及びメモリコマンドに基づくデータリードを完了したとき、そのリードデータの最後のメモリアドレスに続くアドレスへのリードアクセス要求以外のアクセス要求を検出するまで前記チップ選択信号の活性状態を維持する動作モードを採用する。

(もっと読む)

少端子マイクロコンピュータおよびその検査方法

【課題】短時間で検査できる少端子マイクロコンピュータおよびその検査方法を提供する。

【解決手段】入力端子P1i,P2iと出力端子P1o,P2oがCPU71の動作ビット数より少ない数で配置され、テストモードとユーザモードで、入力端子P1i,P2iからそれぞれのシリアルデータを独立して入力し、出力端子P1o,P2oからそれぞれのシリアルデータを独立して出力可能に構成されてなる少端子マイクロコンピュータであって、入力モード切り替え回路74iと入力回路73iの間におけるテストモードの入力経路に挿入され、入力される3以上の多値符号のシリアルデータを入力回路73iで処理可能な2値符号のシリアルデータに変換して出力する入力変換回路10iを有してなる少端子マイクロコンピュータ100とする。

(もっと読む)

電子装置およびマイクロコントローラ

【課題】シリアル通信を用いて複数の不揮発性メモリに同じデータの書き込みを行うマイクロコントローラにおいて、書き込みの確認処理を簡素化することを目的とする。

【解決手段】マイクロコントローラ1のチップセレクト出力端子CS1〜CS3は、その各々が、複数の不揮発性メモリ2a〜2cのうち1つおよび調停回路3の入力端子の1つ3b、3d、3fに接続され、不揮発性メモリ2a〜2cのデータ出力端子OUTは、それぞれ調停回路3の入力端子の1つ3a、3c、3eに接続され、調停回路3の出力端子3gは、マイクロコントローラ1のシリアルデータの入力端子M−INに接続され、調停回路3は更に、入力端子3b、3d、3fへ入力される信号がすべてオンとなっているときは、入力端子3a、3c、3eに入力される信号がすべてオンである場合にのみ、出力端子3gから出力される信号がオンとなるように構成されている。

(もっと読む)

集積回路装置

【課題】フラッシュメモリーへの高速書き込み動作及びチップ面積の縮小化を可能とする集積回路装置を提供する。

【解決手段】集積回路装置は、電気的に書換え可能な不揮発性メモリー14と、外部装置からの指示に基づいて不揮発性メモリー14を書換え可能にする制御回路10と、を含み、制御回路10は、外部装置からのシリアルデータを受信するシリアル通信回路18と、受信したシリアルデータを解析するコマンド解析回路20と、解析された内容に応じて不揮発性メモリー14の書換えのための手順制御を行う不揮発性メモリー制御回路22と、を含む。

(もっと読む)

集積回路装置及び集積回路装置の制御方法

【課題】フラッシュメモリーに書き込まれたデータに対して不正リード/ライト動作防止機能を要した集積回路装置及び集積回路装置の制御方法を提供する。

【解決手段】集積回路装置は、電気的に書換え可能な不揮発性メモリー14と、外部装置からの指示に基づいて不揮発性メモリー14を書換え可能にする制御回路10と、を含み、制御回路10は、外部装置からのシリアルデータを受信するシリアル通信回路18と、受信したシリアルデータを解析するコマンド解析回路20と、解析された内容に応じて不揮発性メモリー14の書換えのための手順制御を行う不揮発性メモリー制御回路22と、を含み、不揮発性メモリー制御回路22は、不揮発性メモリー14の所定のビットを読み出し、不揮発性メモリー14の所定のビットにプロテクトデータが書かれている場合は、不揮発性メモリー14の書き込み又は読み出しをプロテクトする。

(もっと読む)

I/O拡張回路

【課題】 汎用ロジックICのシフトレジスタを使ってI/Oポートを拡張すると共に、動作速度を向上させることができるI/O拡張回路を提供する。

【解決手段】 ワンチップマイコン1と汎用シフトレジスタIC2との間で連続出力モードを持つクロック同期方式を用いて、ワンチップマイコン1から汎用シフトレジスタIC2にシリアルデータ、同期クロック、ラッチタイミングの信号を送信し、汎用シフトレジスタIC2では、汎用ロジックICをカスケード接続した構成であり、受信した同期クロック、ラッチタイミングの信号に従って、シリアルデータを複数ビットのパラレルデータに変換するI/O拡張回路である。

(もっと読む)

縮小命令セット・コンピュータ・マイクロプロセッサーの構造

【課題】本発明は、改良された形態の、単純化された縮小命令セット・コンピューター(RISC)マイクロプロセッサーに関する。特に、スタック構造をとるマイクロプロセッサーに関する。

【解決手段】本発明のある態様では、マイクロプロセッサーシステムはマイクロプロセッシングユニットと入出力プロセッサー(IOP)とを含んでいる。大域メモリーユニットは中央処理装置及びIOPと連結されている。ある手段が、中央処理装置及びIOPの大域メモリーユニットへのアクセスを裁定する。ある形態では大域メモリーユニットは複数の大域レジスタを含んでいる。

(もっと読む)

マイクロコンピュータ

【課題】スリープモードの場合でもシリアル通信を行うことが可能なマイクロコンピュータを提供する。

【解決手段】CPUの通常動作モードで生成するメインクロックとは別に、該通常動作モードよりも消費電力量が少ないスリープモードでサブクロックを生成し、スリープモードにおいてサブクロックにより動作し、周辺回路とのシリアル通信を行うシリアル通信手段と、受信データに基づいて、動作モードをスリープモードから通常動作モードに切り替えるウェイクアップが要求されるウェイクアップ要因が発生したか否かを判定するウェイクアップ要因判定手段と、ウェイクアップ要因が発生したと判定されたときに、動作モード切換手段に対し、動作モードをスリープモードから通常動作モードに切り替えるためのウェイクアップ信号を出力するウェイクアップ信号出力手段を備えることを特徴とする。

(もっと読む)

マイクロコンピュータ

【課題】CPUの動作状態をより簡単に確認できるマイクロコンピュータを提供する。

【解決手段】マイクロコンピュータ1のCPU10は、制御プログラムを実行すると、自身に内蔵されているプログラムカウンタ10aのデータを、命令を1ステップ実行するごとにスタックメモリ15に記憶させ、外部機器18よりスタックメモリ15に対するデータ転送要求があると、DMAコントローラ16を起動して入出力回路13へのデータ転送を実行させる。

(もっと読む)

マイクロコンピュータ

【課題】簡略なインターフェイスにより、マイクロコンピュータに内蔵されるフラッシュメモリの書換え処理時間を短縮する。

【解決手段】マイクロコンピュータ101に接続された書換え装置113からデータを受け取るシリアル通信部103と、シリアル通信部103が受け取ったデータを格納するRAM104と、RAM104から転送されるデータにより内容が更新されるバッファメモリ105とを備え、バッファメモリ105に格納されたデータを用いてフラッシュメモリ102の書換えを実行し、フラッシュメモリ102の書換え実行中でないときにのみバッファメモリ105の内容を更新するように制御することで、シリアル通信とフラッシュメモリ書換えを並列に処理する。

(もっと読む)

マイクロプロセッサ

【課題】使い勝手を良くしたマイクロプロセッサを提供する。

【解決手段】パーソナルコンピュータ等に内蔵されるマイクロプロセッサに、ウェイトコントロールレジスタWCR1及びWCR2等のコントロールレジスタを含みかつROM,バーストROM,SRAM,PSRAM,DRAM及びシンクロナスDRAM等の各種半導体メモリやメモリカード及びI/Oカード等のPCカードのインターフェイスを並行制御しうるバスステートコントローラBSCを設ける。バスステートコントローラBSCには、シンクロナスDRAM接続時におけるPCカードの起動信号(−OE、−WE)のセットアップ時間を制御するための制御レジスタ(PCR)が設けられる。

(もっと読む)

マイクロコンピュータ

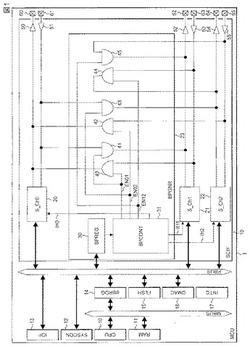

【課題】 従来のマイクロコンピュータでは、動作モードを設定する場合にノイズ等の外乱による誤動作の問題や、また特定の特殊動作モードを指定することによりマイクロコンピュータ内部のROM の内容を読み出すことが可能となり、セキュリティ上の問題があった【解決手段】 動作モード入力端子から入力される動作モード選択信号およびデバイスID信号を含むシリアルデータをパラレルデータに変換する変換回路と、デバイスIDを記憶した不揮発性メモリ回路と、変換回路からのデバイスIDデータと不揮発性メモリ回路の内容とを照合するデバイスID照合回路と、変換回路からの動作モード選択データおよびデバイスID照合回路の照合結果に基づいてマイクロコンピュータの動作モードを設定する動作モード設定回路とを有する。 (もっと読む)

1 - 14 / 14

[ Back to top ]