Fターム[5B062HH04]の内容

マイクロコンピュータ (2,258) | クロック、電源、リセット (407) | 電源 (111) | 電源供給の制御 (87)

Fターム[5B062HH04]に分類される特許

1 - 20 / 87

電力の島を使用した集積回路での電力の管理

半導体集積回路の製造方法

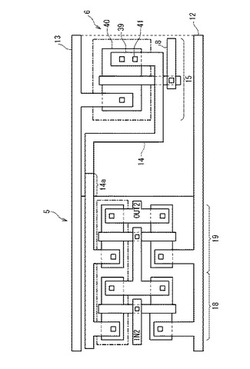

【課題】常時動作領域と電源遮断可能領域とが混在する半導体集積回路を提供する。

【解決手段】半導体基板に設けられ、複数の基本セル(10)の配置が可能なセル配置領域と、空間的に前記セル配置領域と重なって設けられた基本電源配線(11)と、前記基本電源配線(11)から前記セル配置領域への電源供給を停止するスイッチセル(6)と、前記スイッチセル(6)に隣接して前記セル配置領域に配置され、前記スイッチセル(6)が前記セル配置領域への電源供給を停止した場合においても、前記スイッチセル(6)から電源供給を受ける常時動作セル(5)とを具備する。

(もっと読む)

IC出力ポート切換制御装置

【課題】電源を省電力化することができるIC出力ポート制御装置を提供する。

【解決手段】ワイヤレスキーシステムの照合ECU4は、自身のメモリに記憶されたプログラムにて所定周期で動作するソフトウェア制御部19と、自身に元から備わるPWMリソースとを有する。照合ECU4のスリープ中、車両受信機が受信待機動作をとるパルスP4の1周期前のパルスP3で電源ポート11をソフトウェア制御からPWM制御に変更することにより、電源ポート11をPWM制御に切り換える。このため、PWM制御のパルスPxがHiレベルに立ち上がってからの時間が電源安定待ち時間Tsとして車両受信機に供給される。

(もっと読む)

半導体管理システム及び半導体管理方法

【課題】処理の優先度を考慮して印加電圧を制御することにより、半導体装置の消費電力を低下させる。

【解決手段】上位・下位分割器6が、正常に動作するために必要な電圧である正常動作電圧が低い演算器ほど、優先度の高い処理を割り当てる。電源装置2は、正常動作電圧の低さの順位が所定の順位以内の演算器に対しては、印加電圧を当該演算器の正常動作電圧以上に維持し、他の演算器に対しては、所定の場合に、印加電圧を当該演算器の正常動作電圧未満にして、優先度の高い処理を正確に実行することを保証しながら、半導体装置1の消費電力の低減を図る。

(もっと読む)

半導体装置および半導体装置の制御方法並びに半導体装置の設計支援方法

【課題】本発明の課題は、組み込みシステムのアーキテクチャに左右されることなく、DVFSの実行に必要なサイクル数を容易に取得することである。

【解決手段】ファームウェア(21)は、サイクル数概算ルーチン(213)と、動作電圧・周波数算出ルーチン(213)とを有する。サイクル数概算ルーチンは、サイクル数概算関数を備える。サイクル数概算関数は、ユーザ回路(6)の処理内容を決定づける属性パラメータの入力でタスクのサイクル数を概算する。動作電圧・周波数算出ルーチンは、サイクル数概算ルーチンの実行によって得られたサイクル数に基づいて、ユーザ回路(6)の目標動作電圧・周波数を算出する。

(もっと読む)

半導体装置

【課題】スタンバイ状態時にSRAMにデータを保持できる電圧が与えられている場合に、パワーオンリセットがかからないようにすることができる半導体装置を提供する。

【解決手段】CPU5は、スタンバイ状態に遷移することを通知する。電源制御回路11は、スタンバイ状態時に、SRAM4における電力消費を低減させる。POR回路2は、外部電源電圧の値と、現在の状態がスタンバイ状態であるかに応じて、パワーオンリセット信号の活性化を制御する。

(もっと読む)

半導体装置

【課題】安定に動作する半導体装置を提供する。

【解決手段】このマイクロコンピュータは、主電源端子T1と電源ノードN1の間に接続されたスイッチS1と、補助電源端子T2と電源ノードN1の間に接続されたスイッチS2とを備え、主電源端子T1の電圧V1と参照電圧VR1とを比較し、V1>VR1の場合はスイッチS1をオンさせるとともにスイッチS2をオフさせ、V1<VR1になった場合は、スイッチS1をオフさせるとともに、電源ノードN1の電圧V3が徐々に上昇するようにスイッチS2をオン/オフさせる。したがって、V3をV1からV2に切換える場合でも、V3によって駆動されるクロック発生回路9は安定に動作する。

(もっと読む)

プロセッサシステム及び半導体集積装置

【課題】処理速度の低下を最低限に抑えかつ従来技術に比較して消費電流の変動を抑える。

【解決手段】プロセッサシステム1は、プログラムメモリ2に格納された複数の命令コードを任意の順序で連続して実行する。テーブルメモリ53は、各命令コードと各命令コードの実行時の消費電流量との関係を示す消費電流量テーブルを格納する。電流変動抑制回路51は、消費電流量テーブルを参照して、連続する2つの命令コードの実行時の消費電流量の差の大きさが所定のしきい値以下になるように、上記連続する2つの命令コードのうちの一方の命令コードの実行時にプロセッサシステム1に流す補正消費電流を算出し、上記算出された補正消費電流量の補正消費電流をプロセッサシステム1に流すように、補正消費電流発生回路54を制御する。

(もっと読む)

マイクロコンピュータ

【課題】リソースでの無駄な消費電力を削減することができるマイクロコンピュータを提供することを目的とする。

【解決手段】外部から電源を供給されるマイクロコンピュータにおいて,それぞれの所定の機能を有し,外部から供給される前記電源の起動時に電源が供給されない複数のリソースと,前記複数のリソースにバスを介して接続され,前記リソースに前記バスを介してアクセス信号を供給する制御ユニットと,前記複数のリソースにそれぞれ設けられ,電源起動信号に応答して外部から供給される前記電源から対応するリソースにリソース内電源を供給する複数のリソース内電源供給部と,前記複数のリソースにそれぞれ設けられ,前記バスを介して供給されるアクセス信号が対応するリソース宛か否かを検知し,前記アクセス信号が対応するリソース宛の場合に前記電源起動信号を対応するリソース内電源供給部に出力できる電源制御部とを有する。

(もっと読む)

半導体集積回路及び半導体集積回路の動作制御方法

【課題】温度が高くなりすぎたりあるいは低くなりすぎたりする発振状態となって、半導体集積回路が誤動作、動作停止等することを防止する。

【解決手段】実施形態によれば、半導体集積回路1は、回路部の温度又は動作速度に基づいて、温度が安定するように、回路部の制御パラメータを調整して、フィードバック制御を実行する制御部と、温度の時系列データである第1の履歴データと、制御パラメータの時系列データである第2の履歴データとを含む履歴データを格納する履歴レジスタ17と、履歴データからフィードバック制御の有効性を判定する有効性判定部24とを有する。

(もっと読む)

異種計算機システム動作方法

【課題】異種計算機システムを動作させる方法を提供する。

【解決手段】1つ以上の高性能プロセッサ620と、高性能プロセッサ620のソフトウェアのタスク実行を支援するプロセッサ支援論理回路6410と、高性能プロセッサ620より少電力なハイパーバイザプロセッサ610を有し、ハイパーバイザプロセッサ610は、自身が処理するのに十分な処理能力を有するソフトウェアのタスクを実行し、高性能プロセッサ620を電力節約状態にするか、又は高性能プロセッサ620を電力節約状態から抜け出させて、自身が処理するのに不十分な処理能力を有するソフトウェアのタスクを実行させるか、又は高性能プロセッサ620とハイパーバイザプロセッサ610とが全てのプロセッサの結合された処理能力を必要とするソフトウェアのタスクを同時に実行する。

(もっと読む)

状態保持回路における状態保全性の検証

【課題】 本発明は、データ処理動作を行うよう構成されたデータ処理回路を備えたデータ処理装置を提供する。

【解決手段】 複数の状態保持回路がデータ処理回路の一部を形成し、これらの回路は、低電力モードに入ったデータ処理回路のそれぞれのノードにてそれぞれの状態値を保持するよう構成される。1以上のスキャンパスは、状態値がそれぞれのノードにスキャンインまたはアウトされてもよいよう、複数の状態保持回路を直列に接続する。複数のパリティ情報生成要素はスキャンパスに結合され、状態保持回路によってそれらそれぞれのノードにて保持されたそれぞれの状態値を示すパリティ情報を生成するよう構成される。複数のパリティ情報生成要素は、それぞれの状態値の一つが変化した場合にパリティパスの出力にて生成された出力パリティ値を反転するよう、1以上のパリティパスを提供し、状態保持回路によって保持された状態値の保全性の外部指示を提供するよう配置される。

(もっと読む)

マイクロコンピュータ

【課題】アプリケーションプログラムの完成前に、システム全体の電源回路の最適化が可能なマイクロコンピュータを提供すること。

【解決手段】本発明に係るマイクロコンピュータ100は、CPU101と、CPU101に接続されたバス107と、バス107に接続される通常動作モードと、バス107と遮断される擬似動作モードと、を備える機能ブロック103A〜103Cと、通常動作モードと前記擬似動作モードとのいずれかを選択するための制御信号を出力する選択回路102と、を備え、機能ブロック103A〜103Cが、擬似動作モードにおいて消費電流を生成する擬似動作回路105A〜105Cと、を備えるものである。

(もっと読む)

半導体集積回路装置およびその制御方法

【課題】確実にスリープモードに設定することが可能な半導体集積回路装置およびその制御方法を提供する。

【解決手段】まず、第1の値に設定された第1のイネーブル信号を演算部に供給し、演算部を通常動作モードより消費電力が小さいスリープモードに設定する。次に、第1の期間経過後に第1のイネーブル信号が第1の値であるか否かを判定し、第1の値である場合、第2の値に設定された第2のイネーブル信号をメモリに供給し、メモリをスリープモードに設定する。次に、第2の期間経過後に第2のイネーブル信号が第2の値であるか否かを判定し、第2の値である場合、第3の値に設定された第3のイネーブル信号をアナログ回路に供給し、アナログ回路をスリープモードに設定する。次に、第3の期間経過後に第3のイネーブル信号が第3の値であるか否かを判定し、第3の値である場合、第4の値に設定された第4のイネーブル信号をレギュレータに供給し、レギュレータをスリープモードに設定する。

(もっと読む)

半導体装置及び自動車用コントロールシステム

【課題】電源遮断後も、PLL発振状態からの遷移か、PLL自走からの遷移かの識別を可能にする。

【解決手段】電源供給状態から電源遮断状態に遷移された後に再び電源供給状態に復帰される第1領域(12)と、上記第1領域の電源遮断にかかわらず、電源電圧が保持される第2領域(13)と、上記第1領域に供給される第1クロック信号を形成する発振器(11)とを含んで半導体装置(1)を構成する。上記第1領域はPLL回路を含む。上記第2領域には、上記PLL回路の動作モードがPLL発振モードであるかPLL自走モードであるかを識別可能な情報を保持可能な情報保持部を設け、上記第1領域が電源遮断状態から電源供給状態に復帰した際の上記PLL回路の動作モードを、上記情報保持部の保持情報に従って決定する。

(もっと読む)

電源制御システム及び電源制御方法

【課題】複数の機能回路ブロックを備えた半導体装置の回路規模を抑制しつつ、複数の機能回路ブロックに供給される電源電圧を個別に制御可能な電源制御システムを提供すること。

【解決手段】テスト制御部103は、アイドル状態の機能回路ブロックD109を検出した後、アドレス/データバス101を介して電源制御部104に電圧降圧指示を出す。電源ドメインD113の電源電圧降圧完了後、テスト制御部103は、アドレス/データバス101を介して機能回路ブロックD109にテストパターンを送信し、その結果を期待値と比較する。当該比較結果に基づいて、電圧差による遅延エラー等の異常が発生したと判別した場合、テスト制御部103は、機能回路ブロックD109を正常な状態に戻すために、電源制御部104に電源ドメインD113の電圧昇圧指示を出す。

(もっと読む)

メモリを内蔵したマイクロプロセッサ

【課題】プログラムをメモリに転送して動作させるマイクロプロセッサでは、通常動作と特殊動作で使用するメモリの容量が異なるが、メモリ全体に電力を供給していたので、消費電力が増大するという課題があった。本発明ではメモリの消費電力を低減することができるマイクロプロセッサを提供することを目的にする。

【解決手段】メモリを独立して電源が供給できる複数のメモリ領域に分割し、使用するメモリ領域にのみ電源を供給するようにした。マイクロプロセッサの消費電力を低減できる。

(もっと読む)

マイクロプロセッサ、電子制御ユニット、電源制御方法

【課題】低消費電力と低コストの両立を図りながら、マルチプロセッサの消費電力を低減できるマイクロプロセッサ、電子制御ユニット及び電源制御方法を提供すること。

【解決手段】 N個のプロセッサ19と、複数のグループに分けられたN個のプロセッサに、グループ毎に共通の電源電圧を供給する電源回路17と、グループ毎に共通のクロック周波数のクロックを供給する、電源回路と対のクロック生成回路18と、プロセッサの負荷に基づき、グループ毎に電源電圧とクロック周波数を制御する制御回路14と、を有し、電源回路17の数の合計がN個より小さいM個であり、電源回路17の数の合計又はクロック生成回路18の数の合計が、N個より小さいM個である、ことを特徴とするマイクロプロセッサ100又はチップセット100を提供する。

(もっと読む)

多コア・プロセッサの電力供給及び電力管理

【課題】本願における開示された主題の実施例によれば、複数の電圧調節器(「VR」)を備えた電力管理システムを用いて、多コア・プロセッサ内のコアに電力を供給することができる。

【解決手段】各VRは電力をコア、又はコアの一部に供給することができる。別々のVRが、複数の電圧を多コア・プロセッサ内のコア/一部に供給することができる。VRの出力電圧の値は、電圧調節器が電力を供給する先のコア/一部の方向下で調節することができる。一実施例では、複数のVRをコアと単一のダイに一体化することができる。別の実施例では、複数のVRを備えた電力管理システムは、多コア・プロセッサのダイとは別個のダイ(「VRダイ」)上にあり得る。VRダイは、多コア・プロセッサ・ダイと同じパッケージに含めることができる。

(もっと読む)

半導体装置

【課題】外部装置を駆動する駆動回路が形成されたチップの面積の増加を抑制することができる半導体装置を提供する。

【解決手段】フラッシュメモリ22がリード動作を実行する場合は、セレクタ26は、ロジック回路30から入力された選択信号SELに応じて基準電圧VREF1を選択する。VLCD昇圧回路28は、基準電圧VREF1を昇圧した駆動電圧VLCDをLCDパネルドライバ12に出力する。また、フラッシュメモリ22は、電源電圧VDDの供給のみでリード動作を実行する。プログラム動作またはイレース動作を実行する場合は、セレクタ26は、選択信号SELに応じて基準電圧VREF2を選択する。VLCD昇圧回路28は、基準電圧VREF2を昇圧した電圧VPPをフラッシュメモリ22に出力する。フラッシュメモリ22は、電圧VPPの供給を受け、プログラム動作またはイレース動作を実行する。

(もっと読む)

1 - 20 / 87

[ Back to top ]