Fターム[5B079BB04]の内容

Fターム[5B079BB04]の下位に属するFターム

Fターム[5B079BB04]に分類される特許

1 - 20 / 97

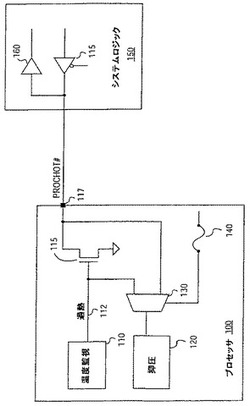

プロセッサの温度制御インタフェース

【課題】アプリケーションに適当な制御及び/又は同期化性能を提供することを目的とする。

【解決手段】プロセッサの温度制御インタフェース技術である。一実施例において、プロセッサは双方向インタフェースと、前記双方向インタフェースで内部の高温を示す第1の信号をアサートする出力ロジックとを含む。内部の高温が示された場合、又は前記双方向インタフェースで外部信号が受信された場合のいずれかの場合に、抑圧ロジックがプロセッサの動作を抑圧する。

(もっと読む)

タイマ回路、その制御方法、マイクロコンピュータ及び空気清浄機

【課題】クロック信号が切り替えられた際の不具合の発生を低減する。

【解決手段】本発明に係るタイマ回路110は、入力クロック信号115を用いてカウント値134をカウントするカウンタ123と、入力クロック信号115が変更された際に、基準値135として第3設定値133を選択する選択部125と、カウント値134が基準値135分変化したタイミングで変化するタイマ出力信号116を生成する比較部127と、現在のカウント値より大きい値を第3設定値133として演算する第3設定値演算部124とを備える。

(もっと読む)

クロック生成回路、それを用いたプロセッサシステム、及びクロック周波数制御方法

【課題】システムクロック信号の周波数を切り換えた場合の通信応答性を向上させること。

【解決手段】選択信号ss1に基づいて、互いに周波数の異なる第1のクロック信号ck1及び第2のクロック信号ck2の一方をシステムクロック信号cksとして選択するシステムクロック選択回路SEL1と、システムクロック信号cksを分周し、複数の分周クロック信号を生成する分周回路103と、選択信号ss1と分周比設定信号ss2とに基づいて、複数の分周クロック信号から通信クロック信号ckioを選択し、選択信号ss1の切り換わりタイミングに同期して選択された通信クロック信号ckioへ切り換える通信クロック選択回路SEL2と、を備えるクロック生成回路CG。

(もっと読む)

通信システム及びそれに用いられる通信ノード

【課題】通信装置内の内部回路の一部を停止させるのみならず、通信装置内の通信ユニットまでも停止させて、更なる省電力化を図る。

【解決手段】各々が通常モードと省電力モードとを有するノードがLANケーブルを介して相互に接続され、ピアトゥピアで通信を行う通信システムにおいて、各ノードは、他のノードとの間で行う通信の制御を担当する第1制御手段と、第1制御手段で担当しない制御を担当する第2制御手段と、第1制御手段に対して動作クロックを供給するクロック供給手段とを有し、第1制御手段は、ハブから送信される省電力モード切替信号を受信する受信手段と、ハブに対してモード切替することを示す信号を送信する送信手段と、送信手段に対して前記信号を送信するように指示するとともにクロック供給手段に対してモード切替を指示する状態遷移手段と、LANケーブルの電圧変化が所定の閾値を越えたか否かを検知する検知手段とを備える。

(もっと読む)

情報処理装置

【課題】余分な消費電力の発生を抑制することを課題とする。

【解決手段】情報処理装置は、割り込みコントローラへの割り込み要因の入力とともに、当該割り込みコントローラへのクロック信号を送信する。また、情報処理装置は、割り込みコントローラへ入力される割り込み要因がマスク対象である場合に、当該割り込みコントローラへのクロック信号の送信を停止する。また、情報処理装置は、DSPへの割り込み信号がマスク対象である場合に、割り込みコントローラへのクロック信号の送信を停止する。また、情報処理装置は、DSPへの割り込み信号の入力とともに、当該DSPへのクロック信号を送信する。また、情報処理装置は、DSPにおける処理の終了後、終了通知を受信し、割り込みコントローラ及びDSPへのクロック信号の送信を停止する。

(もっと読む)

情報処理装置及び情報処理装置の起動方法

【課題】起動時間を短縮できる情報処理装置及び情報処理装置の起動方法を提供する。

【解決手段】情報処理装置は、PLLを備え、低速の第1のクロック信号と第1のリセット信号とが入力し、前記第1のリセット信号の入力後、前記PLLの安定化期間経過後に、前記第1のクロック信号より高速の第2のクロック信号を出力するクロック生成部と、前記第2のクロック信号に基づいて、入力するデータを処理するデータ処理部と、内部メモリを備え、前記クロック生成部の前記PLLの安定化期間に、前記データ処理部に処理させる前記データの少なくとも一部を、外部メモリから前記内部メモリにロードするデータロード部と、を備える。

(もっと読む)

セルフリフレッシュ・モードのためのメモリ・デバイス制御

【課題】セルフリフレッシュ・モードのためのメモリ・デバイス制御を提供する。

【解決手段】メモリ回路において、メモリ・コントローラがパワーダウンおよびパワーオフされている間、DDR3 RDIMMなどのメモリ・デバイスがセルフリフレッシュ・モードで安全に動作することを保証するために、メモリ・デバイスのクロック・イネーブル(CKE)入力が、(i)メモリ・コントローラによって印加されたCKE信号と、(ii)パワー・モジュールによって供給された終端電圧の両方に接続される。メモリ・コントローラをパワーダウンするために、メモリ・コントローラはCKE信号をローに駆動し、パワー・モジュールは終端電圧をローに駆動し、パワー・モジュールはメモリ・コントローラをパワーダウンする。通常の動作を再開するために、パワー・モジュールはメモリ・コントローラをパワーアップし、メモリ・コントローラはCKE信号をローに駆動し、パワー・モジュールは、終端電圧をパワーアップする。

(もっと読む)

コンピュータ装置、CPUクロック調整方法

【課題】イベントに対するコンピュータ装置からのレスポンスを早くする。

【解決手段】本発明は、CPU1を有し、CPU1のクロック周波数を調整するコンピュータ装置に適用される。本発明のコンピュータ装置は、次に発生するイベントを予測するイベント予測手段313と、予測されたイベントが発生する前に、そのイベントに応じてCPU1のクロック周波数を事前に調整するクロック調整手段312と、を有する。

(もっと読む)

マイクロコンピュータ

【課題】チップ外に出力されるクロック信号と、チップ内のクロック信号との間の位相差を低減する。

【解決手段】第1クロック信号を発生可能な発振器(101)と、上記第1クロック信号とフィードバック信号との位相比較を行い、それに基づいて第2クロック信号を形成するPLL回路(102)とを設ける。さらに、上記第2クロック信号に基づいて、チップ内部に供給される第3クロック信号と、チップ外部に出力される第4クロック信号(CLK(φ))とを形成するクロックパルスジェネレータ(103)と、クロック遅延補正データが格納されるクロック遅延補正データ記憶部(105)とを設ける。上記PLL回路に、上記フィードバック信号を補正するための可変ディレイ回路(13)を設け、上記位相差低減のためのクロック遅延補正を行う。

(もっと読む)

画面表示制御装置およびこの画面表示制御装置の制御用プログラム

【課題】必要なときにのみクロックアップすることにより、画像メモリからの画像データの読出しを阻害することなく、画像メモリへの画像データの書込みを確実に行うとともに、コストダウンを図ることのできる技術を提供する。

【解決手段】画像データ書込要求信号と画像データ読出要求信号との受付けが重複したときにのみ、RAM制御部765は、高速モードの高クロックを生成するように、クロック切換部764に対してクロック切換信号を出力するため、必要なときにのみクロックを切換えてクロックアップすることにより、VRAM766からの画像データの読出しを阻害することなく、VRAM766への画像データの書込みを確実に行うことができる。また、必要なときのみクロックアップすることで、放射電磁波などを低減できるとともに省電力を図ることができるためコストダウンを図ることができる。

(もっと読む)

コンピュータ装置

【課題】RC発振器の周波数変動が大きい場合やRC発振器の周波数とUARTの通信速度が近い場合であっても、スタンバイ状態にあるマイクロコントローラを正常に起動させることができるようにする。

【解決手段】UART機能とスタンバイ機能を有するマイクロコントローラ1を備え、該マイクロコントローラがスタンバイ状態のとき該マイクロコントローラ用のCPUクロック発振器3が動作を停止するコンピュータ装置において、マイクロコントローラ1がスタンバイ状態のときUARTによるUART起動信号を受信すると割込み信号INTUを生成するUART起動回路10を備え、該割込み信号INTUによりCPUクロック発振器3が動作を開始するとともにマイクロコントローラ1が通常動作に復帰する。

(もっと読む)

デジタル処理コンポーネント内で使用する適応電圧スケーリングクロック発生器およびその操作方法

【課題】デジタル処理コンポーネントの電源レベルを調整して、適正な電力消費を実現する。

【解決手段】複数の動作周波数に変更することができるクロック信号を選択的にデジタル処理コンポーネント(100)に加えるクロック制御回路(705,710,715)が開示される。クロック制御回路(705,710,715)は(i)第1の動作周波数を第2の動作周波数に変更するコマンドを受信する、(ii)コマンドに応答して加えられたクロック信号をディセーブルする、(iii)第2の動作周波数を有するテストクロック信号を発生する、(iv)テストクロック信号を電源調節回路(125)に加える、および(v)電源調節回路(125)からの状態信号を感知するように操作できる。状態信号はデジタル処理コンポーネント(100)の電源レベルが第2の動作周波数に対して適切な最適値に調節されていることを示す。

(もっと読む)

携帯電子装置及び動作クロック制御方法

【課題】 電池駆動の携帯電子装置で、動作クロック周波数の適切な制御を行い、低消費電力化を図る。

【解決手段】 第1部品回路と、第1部品回路との間でデータを授受する第2部品回路と、前記データを授受する経路内に設けられたFIFOとを備える携帯電子装置の動作クロック制御方法において、FIFOが単位時間内で一杯または空になる回数を計数し、該計数値に応じて第1部品回路の動作クロックの周波数変更を行う。

(もっと読む)

クロック制御回路およびそれを搭載した半導体集積装置

【課題】ダブルエッジトリガ型フリップフロップ回路に対するクロック信号の供給を停止させるとき、当該フリップフロップ回路が保持するデータが不必要に更新されてしまうことがある。

【解決手段】エッジ検出回路61は、第1クロック信号を受け、そのエッジを検出すると、所定幅のパルス信号を出力する。論理ゲートは、エッジ検出回路61の出力信号と、ダブルエッジトリガ型フリップフロップ回路の使用状態を示すイネーブル信号とを受け、イネーブル信号が有意な期間、エッジ検出回路61の出力信号に追従する信号を出力し、イネーブル信号が非有意な期間、非有意なレベルの信号を出力する。トグル型フリップフロップ回路は、論理ゲートの出力信号を受け、所定幅のパルス信号を検出するたびに、論理レベルが反転する信号を、第2クロック信号として出力する。

(もっと読む)

動的電圧制御方法および装置

【課題】プロセッサに供給する電源電圧及びクロック周波数を制御して消費電力を低減する。

【解決手段】プロセッサのクロック周波数要求を特定し、このクロック周波数要求を支援する電圧要求を特定する、動的電力コントローラが提供される。この動的電力コントローラは、クロック周波数要求および電圧要求によって定義される電力状態に、プロセッサを遷移させる。特に、電圧要求によって示される電圧レベルがプロセッサに供給されるとともに、周波数要求によって示される周波数分配がプロセッサのクロック信号に提供される。

(もっと読む)

クロック制御回路および半導体集積回路

【課題】回路設計を容易に行うことができる。

【解決手段】半導体集積回路10は、クロック制御回路11と、モジュール12〜14とを有している。クロック制御回路11は、半導体集積回路10の外部から入力され、他の回路(図示せず)との同期を取るためのシステムクロックsys_CLKおよびモジュール12〜14を動作させるためにそれぞれ供給されるinput信号群およびモジュール12〜14からそれぞれ出力されるoutput信号群に基づいて、モジュール12〜14をそれぞれ所定期間だけ動作させるために必要なクロックCLKを生成し、モジュール12〜14に供給する。すなわち、外部からモジュール12〜14をクロック制御するための専用信号を受け取ることなく、また、モジュール12〜14の内部でクロック制御するためだけの専用回路を設計することなくクロックCLKの制御を行っている。

(もっと読む)

半導体装置

【課題】回路モジュール間の転送の要求と応答を中継するルータを用いた半導体装置のシステム性能を低下させることなく前記ルータによる電力消費を低減する。

【解決手段】半導体装置はリクエスト信号(req)により転送を要求することが可能な複数の第1回路モジュール(102)と、レスポンス信号(res)により前記転送要求に応答することが可能な複数の第2回路モジュール(103)と、前記第1回路モジュールと第2回路モジュールとの間において転送の要求と応答を中継するルータ(104)とを有する。ルータは、レジスタの設定値で指定される所定期間に一群の前記第1回路モジュールから転送要求がないとき、新たに前記一群の第1回路モジュールから転送要求があるまで、当該一群の第1回路モジュールからの転送要求を処理する回路部分の同期クロック信号を停止する。

(もっと読む)

計算機システム、プロセッサ装置および計算機システムの制御方法

【課題】低消費電力モードへの移行の応答性の大幅に改善し、消費電力を削減する計算機システムを提供する。

【解決手段】本発明の計算機システムは、実行状態と停止状態とを有するプロセッサ装置と、プロセッサ装置からのコマンド要求に従って機能ブロックをアクセスするアクセス制御手段とを備え、プロセッサ装置は、スリープ要求信号を受けると、スリープ応答信号を応答するとともに、停止状態に遷移することを示す停止通知信号をアクセス制御手段に出力し、アクセス制御手段は、停止通知信号を受けたとき、プロセッサ装置からコマンド要求が出力されている場合、コマンド要求を受理した後に、コマンド要求の入力をマスクし、プロセッサ装置からコマンド要求が出力されていない場合、コマンド要求の入力をマスクし、停止通知信号が解除された場合に、マスクを解除する。

(もっと読む)

クロック周波数制御装置

【課題】 フレームの情報が格納されているヘッダの解析から、そのフレームを処理する音声処理回路の処理が破綻しないように最大のクロック周波数に決定していたが、メインデータの内容によっては処理が速く終わっており過剰な周波数のクロック供給がなされていた。

【解決手段】 入力データ信号を処理する信号処理回路への供給クロックを、周波数判定回路で判定した最大周波数より低い周波数を供給し、周波数決定回路により1フレームの処理状況に応じてクロックを変化させることにより、消費電力を低減させることが可能である。

(もっと読む)

データ処理装置

【課題】連続したデータを信号処理するためにかかる消費電力を削減することができるデータ処理装置を提供する。

【解決手段】第1のデータ格納部110に格納されたデータに複数の信号処理を施す第1の信号処理部120と、第1の信号処理部120によって処理されたデータを格納する第2のデータ格納部112と、第2のデータ格納部112に格納されたデータを実時間処理で読み出して信号処理を行う第2の信号処理部130と、データの特徴に基づいて各信号処理をパイプラインステージに割り振ったパイプライン構成で第1の信号処理部120にデータを処理させると共に、各信号処理を実時間処理より速い速度で行わせることで間欠動作させるよう第1の信号処理部120を制御する信号処理制御部150と、間欠動作の停止期間に第1の信号処理部120および信号処理制御部150に対するクロックや電源の供給を制限するクロック/電源制御部160とを備える。

(もっと読む)

1 - 20 / 97

[ Back to top ]