Fターム[5B125BA14]の内容

リードオンリーメモリ (43,397) | メモリ種別 (5,638) | PROM (323) | ヒューズ (118)

Fターム[5B125BA14]に分類される特許

1 - 20 / 118

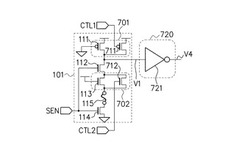

ヒューズ素子読み出し回路

【課題】十分な読み出しマージンを確保し、ヒューズ素子のデータ読み出しの際に誤判定を防止することができるヒューズ素子読み出し回路を提供することを課題とする。

【解決手段】切断済みと未切断とで抵抗値が異なる第1のヒューズ素子(115)と、通常モードと試験モードとで異なる抵抗値を有する第1の抵抗回路(701,702)と、前記第1のヒューズ素子の抵抗値及び前記第1の抵抗回路の抵抗値に応じた読み出し電圧を出力する読み出し電圧出力回路(101)とを有することを特徴とするヒューズ素子読み出し回路が提供される。

(もっと読む)

半導体記憶素子及び半導体記憶装置

【課題】LSI素子の性能劣化及びヒューズ素子の欠陥の増加を抑制できる半導体記憶素子及び半導体記憶装置を提供する。

【解決手段】半導体記憶素子100は、第1ヒューズ線111と、第1ヒューズ線111と並列接続された第2ヒューズ線112とを有し、切断されているか否かによって2値のデータを保持するヒューズ素子110と、一端がワード線130に接続されており、ヒューズ素子110に電流を流すか否かを選択する選択素子120と、を備える。

(もっと読む)

半導体記憶装置、及び半導体記憶装置の動作方法

【課題】光学的に書き込み状態が解析されることがなく、安価に実現することのできる、半導体記憶装置及びその動作方法を提供すること。

【解決手段】半導体記憶装置は、書込み処理が行われていない第1半導体記憶素子と、書込み処理が行われた第2半導体記憶素子とを具備する。前記第1半導体記憶素子及び前記第2半導体記憶素子は、それぞれ、不純物が注入された半導体層を備える抵抗部と、前記抵抗部に接続される、第1コンタクトと、前記抵抗部に接続される、第2コンタクトとを具備する。前記第1半導体記憶素子における前記半導体層の不純物の活性化率は、前記第2半導体記憶素子のそれとは異なっている。

(もっと読む)

多値ROMセル及び半導体装置

【課題】集積度が高く、製造ばらつきの影響が小さく、製造歩留まりの高い多値ROMセルを提供する。

【解決手段】多値ROMセルは、ROMセルトランジスタTrと、複数のビット線BT1〜BT3と、第1金属配線31〜44とを具備している。ROMセルトランジスタTrは、基板表面の領域に設けられている。複数のビット線BT1〜BT3は、基板表面の上方に設けられ、Y方向に伸び、Z方向に並んで配置されている。第1金属配線31〜44は、ROMセルトランジスタTrのソース・ドレイン22の一方に接続され、複数のビット線BT1〜BT3の各々の近傍にまで連なる。第1金属配線31〜44は、複数のビット線BT1〜BT3のうちのいずれかに接続されているか、又は、いずれにも接続されていない。

(もっと読む)

書き込み制御回路及び半導体装置

【課題】電気的に1回限りの書き込みが行われる記憶素子への誤書き込みを抑制する。

【解決手段】入力部11は、電気的に1回限りの書き込みが行われる記憶素子(電気ヒューズ素子2)への書き込みを指示する複数パルスの書き込み信号を入力し、書き込み制御部12は、入力された書き込み信号のパルス数が所定数に達するまで、電気ヒューズ素子2への書き込みを無効状態にすることで、書き込み信号の信号線にノイズやグリッジのような連続性の少ないパルスがのっても、これらのパルスにより直ちに書き込みトランジスタ3がオンすることが抑制される。

(もっと読む)

メモリシステム

【課題】1つの実施形態は、例えば、不揮発性メモリデバイスの信頼性を改善できるメモリシステムを提供することを目的とする。

【解決手段】1つの実施形態によれば、不揮発性メモリデバイスとモニタ部と変更部とを有することを特徴とするメモリシステムが提供される。不揮発性メモリデバイスは、データを記憶する。モニタ部は、前記不揮発性メモリデバイスに対するデータの書き込み処理及び消去処理による前記不揮発性メモリデバイスの特性をモニタする。変更部は、前記モニタされた前記不揮発性メモリデバイスの特性に応じて、前記書き込み処理に要する時間が目標値に一致するように、書き込み動作とベリファイ動作とが交互に繰り返される前記書き込み処理における書き込み開始電圧の値と書き込み電圧の増加幅との少なくとも一方を変更する。

(もっと読む)

半導体記憶装置

【課題】1つの実施形態は、例えば、出荷後においてメモリセルの動作特性を変更できる半導体記憶装置を提供することを目的とする。

【解決手段】1つの実施形態によれば、メモリセルアレイと記憶部と選択部と起動処理部と動作制御部とを有することを特徴とする半導体記憶装置が提供される。メモリセルアレイでは、複数のメモリセルが配列されている。記憶部は、選択される候補となる複数の動作パラメータを予め記憶する。選択部は、ユーザからの変更指示に応じて、前記複数の動作パラメータのうち前記メモリセルを動作させるために使用すべき動作パラメータを選択する。起動処理部は、ユーザからの起動指示に応じて、電源を起動するとともに、前記選択部により選択された動作パラメータを前記記憶部から読み出して使用可能な状態に設定する。動作制御部は、前記起動処理部により使用可能な状態に設定された動作パラメータを使用して、前記メモリセルを動作させる。

(もっと読む)

ランダム・アクセス電気的プログラム可能なEヒューズROM

【課題】ランダム・アクセス電気的プログラム可能なeヒューズROMを提供する。

【解決手段】1回プログラム可能な読み出し専用メモリ(OTPROM)が、アグレッシブにスケール縮小された、シリサイド移動可能なeヒューズの2次元配列において実施される。ワード・ライン選択は、VDDにおいて動作するデコード論理によって実施され、一方ビット・ライン・ドライブは、VDDとプログラミングのためのより高い電圧VPとの間でスイッチ切替えされる。OTPROMは、それゆえコストを加算することなしに他の技術と適合可能で、統合することができ、そして、ヒューズ・プログラミングの間、電圧降下を最小にする高電流経路の最適化をサポートする。プログラム可能参照を有する差動センス増幅器は、センス・マージンを改善するために使用され、個々のヒューズに設けられるセンス増幅器の代りに、ビット・ライン全体をサポートすることができる。

(もっと読む)

書き込み制御回路及び半導体装置

【課題】電気的に1回限りの書き込みが行われる記憶素子への誤書き込みを抑制する。

【解決手段】書き込み制御部11は、電気的に1回限りの書き込みが行われる記憶素子(電気ヒューズ素子2)への書き込みを、書き込みを指示する書き込み信号に応じて制御し、電圧検出部12は、電源電圧、または電気ヒューズ素子2へ供給される書き込み電圧の立ち上がり時に、一定期間、書き込み信号に係わらず電気ヒューズ素子2への書き込みを書き込み制御部11に停止させる。

(もっと読む)

不揮発性半導体記憶装置

【課題】データの信頼性を維持しつつ、書き込み時間を短縮する。

【解決手段】制御回路6は、選択ワード線に書き込みパルス電圧を印加することにより選択ワード線に沿った1ページのメモリセルに対する書き込み動作を実行した後、データ書き込みが完了したか否かを確認するベリファイ読み出し動作を実行する。データ書き込みが完了しなかった場合に書き込みパルス電圧を所定のステップアップ電圧の分だけ上昇させるステップアップ動作が実行される。ビットスキャン回路は、ベリファイ読み出し動作のセンスアンプ回路に保持された読み出しデータに基づいて、同時に読み出された複数のメモリセルのうち、所定の閾値電圧に達したと判定されるメモリセルの数が所定数以上となったか否かを判定する。制御回路は、前記ビットスキャン回路の判定結果に基づいて、ステップアップ電圧の大きさを変化させる。

(もっと読む)

半導体メモリおよび半導体メモリの製造方法

【課題】 リファレンスメモリセルの閾値電圧を設定するための試験時間を短縮する。

【解決手段】 記憶部は、リファレンスメモリセルのいずれかである選択リファレンスメモリセルを示す情報を記憶する。デコード部は、リアルメモリセルがアクセスされるときに、記憶部に記憶されている情報に応じて選択リファレンスメモリセルに対応する1つの選択信号を出力し、複数のリファレンスセルトランジスタの閾値電圧を設定するときに、複数のリファレンスメモリセルにそれぞれ対応する複数の選択信号を出力する。スイッチ回路は、選択信号をそれぞれ受けてオンし、リファレンスメモリセルのドレインをリファレンスグローバルビット線にそれぞれ接続する。制御部は、リファレンスセルトランジスタの閾値電圧を設定するときに、リファレンスワード線およびリファレンスグローバルビット線をそれぞれ所定の電圧に設定する。

(もっと読む)

不揮発性メモリを備える半導体装置及び不揮発性メモリに対するアクセス制御方法

【課題】電源投入後システムリセットが完了する前にヒューズメモリやアンチヒューズメモリの様なリード動作によりストレスが生じる不揮発性メモリへの不必要なリードアクセスが連続することを防止する半導体装置を提供する。

【解決手段】nワード(nは2以上の整数)のデータを記憶し、チップイネーブル信号がアクティブなときにアクセスクロックに同期してアクセス可能な不揮発性メモリと、アクセスクロックを計数し、計数値がnに達すると、不揮発性メモリに対するアクセスを禁止し、チップイネーブル信号が非アクティブになるとリセットされるカウンタ回路と、を備える。好ましくはさらに揮発性メモリを備え、システムリセットにより、不揮発性メモリのデータを揮発性メモリへ転送し、不揮発性メモリへのリードアクセスに代えて、揮発性メモリへアクセスする。

(もっと読む)

メモリシステム

【課題】複数の不揮発性半導体メモリを有するメモリシステムで発生する消費電力のピークを低く抑えることができる。

【解決手段】チップ1は、コントローラ20から第1制御信号を受け取ると、第1動作のうちの第1サブ動作を実行して、第1動作を中断する。コントローラ20は第1動作が中断されると、第2制御信号をチップ2に送信する。第2制御信号を受け取ると、チップ2は第2動作のうちの第3サブ動作を実行して、第2動作を中断する。コントローラ20は第2動作が中断されると、第3制御信号をチップ1に送信する。第3制御信号を受け取ると、チップ1は第1動作を再開し、第2サブ動作を実行する。コントローラ20は第2サブ動作が終了すると、第4制御信号をチップ2に送信する。第4制御信号を受け取ると、チップ2は第2動作を再開し、第4サブ動作を実行する。

(もっと読む)

半導体装置、メモリ装置への書込方法、メモリ装置からの読出方法、及び半導体装置の製造方法

【課題】電極へのチャージアップの有無を解析する手法を用いても、書き込まれた情報を解析することができない半導体装置を提供する。

【解決手段】第1半導体素子100は基板上に形成されており、第1絶縁膜、第1電極、及び第1拡散層を備えている。第2半導体素子200は基板に形成されており、第2絶縁膜、第2電極、及び第2拡散層を備えている。第2電極は第1電極に接続している。制御トランジスタ300は、ソース及びドレインの一方が第1電極及び第2電極に接続しており、ソース及びドレインの他方がビットラインBL1に接続しており、ゲート電極がワードラインWL1に接続している。第1電位制御ラインSL1−1は第1拡散層に接続しており、第1拡散層の電位を制御する。第2電位制御ラインSL1−2は第2拡散層に接続しており、第2拡散層の電位を制御する。

(もっと読む)

半導体装置及びその駆動方法

【課題】現行プロセスを用いて追加工程なしに製造でき、高い信頼性を有する多値化された電気ヒューズを有する半導体装置を提供する。

【解決手段】第1フィラメントFS1と、第1フィラメントFS1に接続された第2フィラメントFS2とを有する電気ヒューズ素子を有し、第1フィラメントFS1の第2フィラメントFS2との接続端と反対の端部に接続された第1フィラメントFS1と第2フィラメントFS2の直列抵抗を読み出す直列読み出し部RDSとを有する構成とする。

(もっと読む)

マルチチップパッケージおよびメモリチップ

【課題】消費電流のピーク値を低減する。

【解決手段】複数のメモリチップと、クロック発生回路と、クロック配線とを備える。複数のメモリチップは、夫々、メモリセルアレイと、メモリセルアレイに印加する電位を生成する電位発生回路と、メモリセルアレイに電位発生回路が生成した電位を印加してメモリセルアレイに対するアクセスを行う周辺回路とを備えている。クロック発生回路は、クロック信号を生成する。クロック配線は、クロック発生回路が生成したクロック信号を複数のメモリチップの夫々に共通入力する。ここで、複数のメモリチップは、夫々、クロック配線から入力されるクロック信号にメモリチップ毎に異なる時間の遅延を加えるクロック遅延回路をさらに備え、周辺回路は、電位発生回路が生成した電位をクロック遅延回路が遅延させたクロック信号に基づくタイミングでメモリセルアレイに印加する。

(もっと読む)

ストリング選択線及びビット線の改善されたコンタクトレイアウトを有する3次元メモリアレイ

【課題】インターコネクト及びコンタクト用の実装面積が小さい3次元集積回路メモリ用の構造を低製造コストで提供する。

【解決手段】3次元メモリデバイスは、絶縁材料21,22,23,24で分離され、復号化回路を介してセンスアンプに結合可能なビット線BLnとして導電材料の複数の帯片の形状をしている。導電材料帯片11,12,13,14は、スタック横面に側面を有する。ワード線WLn,WLn+1の複数の導電線16,17は行デコーダに結合でき、複数のスタック上で直交して延びる。導電線は、スタックの表面に共形である。記憶素子は、スタック上の半導体材料帯片の側面と導電線の間の交点の界面領域の多層アレイに設けられる。3次元メモリは、複数層に対する2つの最小線幅のマスクで作られる。半導体材料帯片の端部に階段構造が含まれる。半導体材料帯片に平行な金属層上と、ワード線に平行な上部金属層上にSSLインターコネクトを含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルの閾値電圧分布を狭くした不揮発性半導体記憶装置を提供することを目的とする。

【解決手段】不揮発性半導体記憶装置のデータ書き込み部は、書き込みループとして、プログラム動作、及び第1のベリファイ動作を順次実行する第1の動作モードと、プログラム動作、第1及び第2のベリファイ動作を順次実行する第2の動作モードとを有し、第1のベリファイ動作では、第1のメモリセルに接続されたビット線及び第1のメモリセルに隣接する第2のメモリセルに接続されたビット線をプリチャージした上で、第1のメモリセルのデータを検証し、引き続き、第2のベリファイ動作において、第2のメモリセルの書き込みが完了している場合に、第2のメモリセルに接続されたビット線をプリチャージすることなく、第1のメモリセルに接続されたビット線をプリチャージした上で、第1のメモリセルのデータを検証する。

(もっと読む)

不揮発性半導体記憶装置

【課題】適切なステップ幅のプログラム電圧を用いてデータを書き込む不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、選択ワード線にプログラムに必要なプログラム電圧を印加するプログラム動作及び選択ワード線にベリファイに必要なベリファイ電圧を印加するベリファイ動作からなる書き込みループを、選択ワード線で選択される複数のメモリセルからなるページ単位で、データが書き込まれるまでプログラム電圧を所定のステップ幅で変化させながら繰り返し実行するデータ書き込み部と、ページに属するメモリセルのエンデュランスを判定するエンデュランス判定部とを備え、データ書き込み部は、エンデュランスに応じたステップ幅のプログラム電圧を選択ワード線に供給することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】追加のマスクや追加のプロセスを必要とせず、トランジスタを含む半導体装置に搭載することが可能なメモリ素子を実現する。

【解決手段】半導体装置を、絶縁膜17と金属膜又は金属化合物膜19とを積層した構造を有するメモリ素子16と、メモリ素子16と同一の積層構造を有するゲート構造を持つトランジスタとを備えるものとする。

(もっと読む)

1 - 20 / 118

[ Back to top ]