Fターム[5B125CA02]の内容

リードオンリーメモリ (43,397) | 目的、効果 (6,321) | 節電、低消費電力化、低電力化 (411)

Fターム[5B125CA02]の下位に属するFターム

Fターム[5B125CA02]に分類される特許

1 - 20 / 102

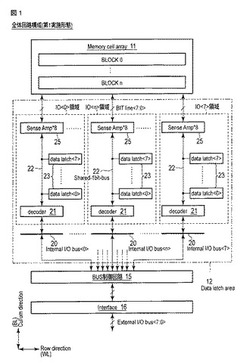

半導体記憶装置

【課題】微細化に対して有利な半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、複数のメモリセルが配置されるメモリセルアレイ11と、前記複数のメモリセルのデータをラッチし、前記メモリセルアレイのデータの入力または出力(I/O)ごとに分割して配置される複数のアドレス領域(IO<0>領域〜IO<7>領域)と、前記複数のアドレス領域に対応して配置され、それぞれが前記複数のアドレス領域と電気的に直列に接続される内部バス配線20と、前記内部バス配線のデータ転送を制御する制御回路15とを具備する。

(もっと読む)

不揮発性半導体記憶装置

【課題】低消費電流で正確なデータ読出を行なうことが可能な不揮発性半導体記憶装置を提供する。

【解決手段】このフラッシュメモリでは、4つのメモリマットMAT0〜MAT3の各々にセンスアンプSA0〜SAmを設け、通常の読出動作モードでは、全メモリマットMAT0〜MAT3のセンスアンプSA0〜SAmに参照電圧VRを供給し、低速読出モードでは、選択されたメモリマットMATのセンスアンプSA0〜SAmのみに参照電圧VRを供給する。したがって、低消費電力で正確なデータ読出を行なうことができる。

(もっと読む)

半導体記憶装置

【課題】読出速度が速い半導体記憶装置を提供する。

【解決手段】フラッシュメモリ3は、選択ビット線BLをプリチャージするプリチャージ回路45と、定電流源50と、電流検知型のセンスアンプ23と、選択ビット線BLがメモリアレイMA2に属する場合は、選択ビット線BLおよび定電流源50をそれぞれセンスアンプ23の入力ノードLBT,LBBに接続し、選択ビット線BLがメモリアレイMA3に属する場合は、選択ビット線BLおよび定電流源50を入力ノードLBB,LBTに接続する切換回路SWT2,SWB2,SWとを含む。したがって、ビット線BLのプリチャージとデータ読出を並列に実行できる。

(もっと読む)

半導体記憶装置

【課題】インタリーブ動作を実行可能に構成され且つLMアドレススキャン動作を実行する半導体記憶装置における消費電力の削減、及び動作の高速化を図る。

【解決手段】複数のカラムのうちの少なくとも1つは、複数ビットのデータの書き込み動作の進行状況を示すLMフラグデータを記憶するためのLMカラムである。カラム制御回路の各々は、対応するメモリコアにLMカラムが存在するか否かを確認するためのLMアドレススキャン動作をする。そのLMアドレススキャン動作の結果をレジスタに格納し、その後の各種動作においては、前記データラッチ回路に保持されたデータが第1のデータである場合、そのメモリコアにおいて前記LMカラムからLMフラグデータを読み出す動作を実行する一方、前記レジスタに保持されたデータが第2のデータである場合、そのメモリコアにおいて前記LMカラムからLMフラグデータを読み出す動作を実行しない。

(もっと読む)

半導体記憶装置

【課題】複数のメモリマクロを備え、かつメモリマクロへの入出力を並行して行なうことができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置1は、複数個のメモリマクロ2_0〜2_Nと、外部と接続される複数個の外部端子P0_0〜PN_3を備える。各外部端子P0_0〜PN_3は、対応するメモリマクロと接続される。

(もっと読む)

半導体メモリ

【課題】メモリの動作特性を改善する。

【解決手段】本実施形態の半導体メモリは、複数のしきい値にそれぞれ対応するデータを記憶する複数のメモリセルを含むメモリセルアレイ1と、複数のトランジスタと外部からのデータ又はメモリセルからのデータを保持するフリップフロップを有する複数のラッチ341と、複数のラッチ有するバッファ回路32と、トランジスタをオフすることにより複数のラッチ341のうちいずれかを非アクティブ状態にする制御回路と、を含む。

(もっと読む)

半導体記憶装置

【課題】GIDLによるホールの発生効率を向上させることが可能な半導体記憶装置を提供する。

【解決手段】フィン3の両側にゲート絶縁膜5を介して設けられ、フィン3にチャネル領域を形成するゲート電極Gと、チャネル領域間のボディ領域にホールを閉じ込めるポテンシャルバリアを形成する不純物拡散層6と、チャネル領域を挟み込むようにしてフィン3に形成されたソース層S/ドレイン層Dとを備え、データ‘1’が書き込まれる際にゲート電圧が負電位かつ基板バイアス電圧およびドレイン電圧が正電位に設定される。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減しつつ、高速に動作させる。

【解決手段】半導体装置の回路が複数の回路ブロックに分割され、前記回路ブロックがそれぞれ正常に動作し得る最小限度の電圧を供給する複数の電圧供給回路を備え、各前記回路ブロックへの最小限度の電圧を供給する制御内容を記憶する電源電圧制御メモリを有し、前記電源電圧制御メモリの記憶する制御内容に従って前記電圧供給回路が各前記回路ブロックに供給する電圧を切り替える電源切り替え手段を備えた半導体装置を用いる。

(もっと読む)

不揮発性半導体メモリ

【課題】プログラム時のピーク電流の抑制とビット線の充電時間の短縮を可能にする。

【解決手段】実施形態の不揮発性半導体メモリは、プログラム時に固定電位VSを発生し、ソース線CELSRCに固定電位VSを転送するセルソースドライバ16と、プログラムデータを一時的に記憶するデータラッチ回路14と、プログラム時に、第1及び第2ビット線の一方にデータラッチ回路14を接続し、第1及び第2ビット線の他方にソース線CELSRCを接続するフックアップ回路13と、ソース線CELSRCの電位レベルを検出するレベル検出回路17と、プログラム時に、ソース線CELSRCの電位レベルが閾値を越えたときに第1及び第2ビット線の充電が完了したと判断し、かつ、第1及び第2ビット線の充電期間を可変にする制御回路18とを備える。

(もっと読む)

半導体装置

【課題】リーク電流が発生しにくく、低消費電力化に好適な半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体基板12内に埋め込まれてX方向に並列して延在する複数のビット線BLと、X方向と交差するY方向に延在するワード線と、ビット線BLと前記第2配線との交点に設けられたメモリセルMと、複数のビット線BLのうち最外列のビット線BLの外側に設けられ、X方向に延在してビット線BLと並走するダミービット線DBLとを含み、ダミービット線DBLが、半導体基板12に供給される電位と同じ電位が供給されるダミービット線(第1ダミー配線)DBL<0>、DBL<1>、DBL<2>を含むことを特徴とする。

(もっと読む)

データ処理装置

【課題】チップ占有面積の増大及び消費電力増大を生ずることなく、比較的容易にオンチップのEEPROMのリードアクセスを高速化することができるデータ処理装置を提供する。

【解決手段】データ処理装置にオンチップされた前記不揮発性メモリには、不揮発性メモリセルのアレイ(10)からロウアドレス系選択動作でビット線に読み出されたデータの全部又は一部をラッチするプリリードキャッシュ部(15)と、プリリードキャッシュ部にラッチされたデータの一部をカラム系選択動作で選択する選択回路(16)とを設け、プリリードキャッシュ部にラッチされたデータのアドレス情報を保持し、保持したアドレス情報と同一のアドレス情報による不揮発性メモリに対するリードアクセスに際してプリリードキャッシュ部への新たなデータのラッチを抑制すると共に、プリリードキャッシュ部にラッチされているデータを前記選択部に選択させる制御を行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】適切なステップ幅のプログラム電圧を用いてデータを書き込む不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、選択ワード線にプログラムに必要なプログラム電圧を印加するプログラム動作及び選択ワード線にベリファイに必要なベリファイ電圧を印加するベリファイ動作からなる書き込みループを、選択ワード線で選択される複数のメモリセルからなるページ単位で、データが書き込まれるまでプログラム電圧を所定のステップ幅で変化させながら繰り返し実行するデータ書き込み部と、ページに属するメモリセルのエンデュランスを判定するエンデュランス判定部とを備え、データ書き込み部は、エンデュランスに応じたステップ幅のプログラム電圧を選択ワード線に供給することを特徴とする。

(もっと読む)

半導体装置

【課題】メモリ回路を含む半導体装置の低消費電力化を図ることを課題とする。

【解決手段】メモリ回路を含む半導体装置において、メモリ回路はワード線とビット線で規定される領域に設けられた半導体素子を有するメモリセルと半導体素子を有さないメモリセルを含み、該半導体素子には、酸化物半導体を用いて形成したオフ電流が極めて低いトランジスタを用いるため、読み出し精度が高まり、低電圧動作が可能となる。また、メモリセルは、ハイまたはローのいずれか一方のデータを記憶し、半導体素子を有するメモリセルは、前記データを構成するハイおよびローのうち、少ない方を記憶し、半導体素子を有さないメモリセルは、多い方を記憶する。

(もっと読む)

メモリチップおよびマルチチップパッケージ

【課題】入力データの取りこぼしを発生させることなく入力バッファの消費電力を低減する。

【解決手段】アドレスサイクル識別回路74は、書き込み先アドレスの入力サイクルの終了を検知してチップ選択信号の出力タイミングよりも早いタイミングでアドレス最終サイクル信号を出力し、バッファ制御部(アンド回路75、オア回路76、オア回路72)は、アドレス最終サイクル信号がHighとなっている間、チップ選択信号の状態に関わらず入力バッファ61を活性状態とする。

(もっと読む)

不揮発性半導体記憶装置

【課題】

本発明は、オペアンプを用いずに、メモリセルの信頼性を向上可能な不揮発性半導体装

置を提供する。

【解決手段】

本発明の一態様の不揮発性半導体記憶装置は、複数のメモリセルを備えたメモリセルア

レイ10と、前記複数のメモリセルの行方向に配列されたメモリセルに共通に接続された

複数のワード線WLと、選択されたワード線WLに接続されたメモリセルにプログラム電

圧をステップアップさせて書き込むたびに、クロック信号の周期を長くするクロック信号

周期制御部22を有し、前記クロック信号を用いて所望の出力電圧を発生する電圧発生装

置13とを備え、前記クロック信号周期制御部22は、前記プログラム電圧をステップア

ップさせて書き込むときの昇圧速度を、初期のプログラム電圧で書き込むときの昇圧速度

と略等しくするように制御することを特徴とする。

(もっと読む)

半導体記憶装置

【課題】読み出し時の消費電力を低減することが可能な半導体記憶装置を提供する。

【解決手段】メモリセルアレイ1は、複数のワード線、及び複数のビット線に接続され、複数のメモリセルがマトリックス状に配置されて構成されている。制御回路7は、複数のメモリセルに対するデータの書き込み、及び読み出しを制御する。制御回路7は、メモリセルアレイの複数の第1メモリセルにデータを書き込む時、複数の第1メモリセルと同時に選択される第2メモリセルに第1フラグデータを設定し、第2メモリセルに第1フラグデータが設定されていない場合、複数の第1メモリセルからデータを読み出さず、第1論理レベルのデータを出力し、第2メモリセルに第1フラグデータが設定されている場合、複数の第1メモリセルからデータを読み出す。

(もっと読む)

半導体記憶装置

【課題】電力消費をより低減可能な新たなビット線階層化方式を備えた半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、行列状に設けられた複数のメモリブロックBと、複数のメモリブロックBに対応して設けられた複数の主ビット線GLとを具備する。メモリブロックBは、行列状に設けられた複数のメモリセルCと、列ごとに設けられた複数の副ビット線BLと、列及び行ごとに設けられ、複数のメモリブロックBに共通である複数のワード線WLと、対応する主ビット線GLを複数の副ビット線BLのいずれかに接続するスイッチ回路SCとを備える。読出し対象の対象セルC1の読出し動作時に、対象セルC1に対応する主ビット線GL1を選択し、対象セルC1の列に対応する副ビット線BL1をスイッチ回路SC1により選択し、複数のワード線WLのうち、対象セルC1の列及び行に対応するワード線WL1を選択する。

(もっと読む)

半導体装置

【課題】昇圧回路の出力側に抵抗を挿入しつつも、内部電源電圧として十分な電圧を確保するとともに、抵抗での消費電力を削減する。

【解決手段】

半導体装置1aは、外部電源電圧VDDに応じた昇圧幅で内部電源電圧VCCを昇圧する昇圧回路10aと、外部電源電圧VDDと所定のリファレンス電圧VREF1とを比較する外部電圧レベル比較回路21aと、昇圧回路10aの出力端子に接続された可変抵抗を有する可変抵抗回路20aとを備え、可変抵抗回路20aは、外部電圧レベル比較回路21aの比較結果に応じて可変抵抗の抵抗値を制御する。

(もっと読む)

記憶装置、半導体装置

【課題】消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提供を目的の一つとする。

【解決手段】記憶素子として機能するトランジスタに蓄積された電荷を保持するためのスイッチング素子として、酸化物半導体膜を活性層として用いたトランジスタを、記憶装置の各メモリセルに設ける。また、記憶素子として用いるトランジスタは、第1のゲート電極と、第2のゲート電極と、第1のゲート電極と第2のゲート電極の間に位置する半導体膜と、第1のゲート電極と半導体膜の間に位置する第1の絶縁膜と、第2のゲート電極と半導体膜の間に位置する第2の絶縁膜と、半導体膜に接するソース電極及びドレイン電極と、を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルの微細化が進展しても回路面積を増大させることなく読み出しを行う。

【解決手段】

中間分布LMのベリファイ動作のためのベリファイ電圧VLMが、負の値に設定されている。中間分布LMのベリファイ動作時においては、ソース線CELSRC、及びウエルSWには正の電圧Vsrc、Vwellを印加しつつ、選択メモリセルMnの制御ゲートには、ベリファイ電圧VLMに対応した電圧を印加する。一方、選択メモリセルMnに隣接する非選択メモリセルMn+1、Mn−1の制御ゲートには、通常の読み出し動作で用いられる読み出しパス電圧Vreadよりも小さい読み出しパス電圧Vread’が印加される。

(もっと読む)

1 - 20 / 102

[ Back to top ]