Fターム[5B125CA07]の内容

リードオンリーメモリ (43,397) | 目的、効果 (6,321) | 小型化、高密度化、高集積化 (714) | 共通化、兼用化 (140)

Fターム[5B125CA07]に分類される特許

1 - 20 / 140

暗号化演算装置を搭載する不揮発性半導体記憶装置

半導体記憶装置

【課題】半導体記憶装置の回路面積を削減する。

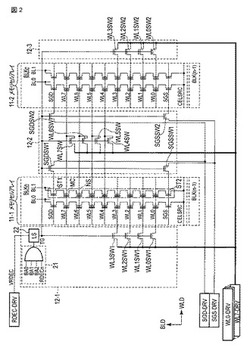

【解決手段】半導体記憶装置10は、複数のメモリセルを有する第1のブロックを含むメモリセルアレイ11−1と、複数のメモリセルを有する第2のブロックを含むメモリセルアレイ11−2と、メモリセルアレイ11−1及び11−2に配設された複数のワード線と、複数のワード線のそれぞれに電圧を転送する複数の転送ゲートSWを有するロウデコーダ12とを含む。第1のブロックに配設された複数のワード線は、第1及び第2のグループを有し、第2のブロックに配設された複数のワード線は、第3及び第4のグループを有する。上記第1及び第3のグループは、転送ゲートSWを共有する。

(もっと読む)

不揮発性プログラマブルスイッチ

【課題】セル面積の小さい不揮発性プログラマブルスイッチを提供する。

【解決手段】第1配線に接続される第1端子と第2配線に接続される第2端子と第3配線に接続される第3端子とを有する第1不揮発性メモリトランジスタと、第4配線に接続される第4端子と第2配線に接続される第5端子と第3配線に接続される第6端子とを有する第2不揮発性メモリトランジスタと、第2配線にゲート電極が接続されたパストランジスタと、を備え、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも高い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が増加し、第2不揮発性メモリトランジスタの閾値電圧が低下し、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも低い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が低下し、第2不揮発性メモリトランジスタの閾値電圧が増加する。

(もっと読む)

半導体記憶装置及び半導体記憶素子

【課題】素子の面積を増大させることなく、かつ、コントロールゲート電圧を制御しなくとも、低電圧で書き込み量を大幅に増やすことが可能であり、また、安定して十分な書き込みを行うことが可能である不揮発性半導体装置を提供すること。

【解決手段】ドレインアバランシェホットエレクトロンにより書き込みを行う半導体記憶素子であって、第1導電型の半導体基板に形成された第2導電型の第1の半導体層と、前記第1の半導体層上に絶縁膜を介して設けられたフローティングゲートと、前記フローティングゲート下部の前記第1の半導体層の表面に形成されたチャネル領域と、前記チャネル領域に接触するように前記第1の半導体層上に設けられた第1導電型のソース領域及びドレイン領域とを有するMOSトランジスタであって、前記チャネル領域が2種類以上のキャリア濃度の分布をもつ半導体記憶素子とした。

(もっと読む)

揮発性メモリ装置のマルチレベルセルプログラム方法

【課題】頁バッファをプレーンの中央部に位置させ、上側メモリレジスタと下側メモリレジスタを区分させる不揮発性メモリ装置を提供する。

【解決手段】第1メモリセルグループと接続される第1レジスタ及び第2メモリセルグループと接続される第2レジスタを含む頁バッファが提供され、各メモリセルに対して下位ビットプログラムを完了する段階と、第1レジスタのデータラッチ部の第1ノードに上位ビットデータを設定する段階と、上位ビットプログラムを行う段階と、第1検証電圧以上にプログラムされた場合、第1ノードに第1データを設定する段階と、第2検証電圧以上にプログラムされた場合、第1ノードに第1データと相反したレベルの第2データを設定する段階と、第3検証電圧以上にプログラムされた場合、第1ノードに第1データを設定する段階と、第1ノードに設定されたデータにより上位ビットプログラムを繰り返す段階を含む。

(もっと読む)

双方向分割ゲートNANDフラッシュメモリ構造及びアレイ、そのプログラミング方法、消去方法及び読み出し方法、並びに、製造方法

【課題】NANDフラッシュメモリ構造において、各セルについてのライン数を削減して、不揮発性メモリデバイスのピッチを改善すること。

【解決手段】分割ゲートNANDフラッシュメモリ構造が、第1伝導型の半導体基板上に形成される。このNAND構造は、第2伝導型の第1領域と、基板内にこの第1領域から間隔をおいて配置されてこの第1領域との間にチャネル領域を定める、第2伝導型の第2領域と、を備える。各々が上記チャネル領域から絶縁された複数の浮動ゲートが、互いに間隔をおいて配置される。各々が上記チャネル領域から絶縁された複数の制御ゲートが、互いに間隔をおいて配置される。該制御ゲートの各々は、1対の浮動ゲートの間にあって該1対の浮動ゲートに容量的に接続される。各々が上記チャネル領域から絶縁された複数の選択ゲートが、互いに間隔をおいて配置される。該選択ゲートの各々は、1対の浮動ゲートの間にある。

(もっと読む)

半導体記憶装置

【課題】回路面積の縮小を図る。

【解決手段】半導体記憶装置は、第1メモリセルに接続される第1ワード線CG1と、第2メモリセルに接続される第2ワード線CG2と、各メモリセルに対する書き込み動作を制御し、第1ワード線および第2ワード線と電気的に接続された電源回路21を有する制御回路2と、第1ワード線と電源回路の間に設けられた第1転送スイッチCGSW1と、第2ワード線と電源回路の間に設けられた第2転送スイッチCGSW2と、を具備する。制御回路は、第1メモリセルに対する書き込み動作において、第1時刻で、第1転送スイッチおよび第2転送スイッチをオンし、第1ワード線および第2ワード線を昇圧させて、第1時刻後の第2時刻で、電源回路と第2ワード線との電気的な接続を切断して第2ワード線を浮遊状態とし、第2ワード線は書き込みパス電圧まで到達する。

(もっと読む)

不揮発性半導体記憶装置

【課題】読み出し動作を正確に実行する。

【解決手段】 制御回路は、メモリトランジスタの読み出し動作を実行する際、選択メモリトランジスタに接続される選択ワード線には、第1の電圧を印加する。選択メモリトランジスタを除く非選択メモリトランジスタに接続される非選択ワード線には、メモリトランジスタの保持データに拘わらずメモリトランジスタを導通させる第2の電圧を印加する。ビット線には、第3の電圧を印加する。ソース線のうち、選択メモリブロック中の前記選択メモリトランジスタが含まれるメモリストリングに接続される選択ソース線には第3の電圧より小さい第4の電圧を印加する。ソース線のうち、選択メモリブロック中の非選択のメモリストリングが接続される非選択ソース線には第3の電圧と略同一の第5の電圧を印加する。

(もっと読む)

不揮発性半導体記憶装置および記憶方法

【課題】メモリユニットの過消去/過書込を回避するとともに書込時間を短縮する。

【解決手段】メモリ制御回路は、メモリユニット(MU11)に格納されたデータ値を読み出すリード動作を実行し、リード動作によって読み出されたデータ値の反転値(XRD1)がメモリユニット(MU11)に書き込まれるようにメモリユニット(MU11)の第1および第2のフローティングゲートの電荷量を制御する反転書込動作を開始し、メモリユニット(MU11)への反転値(XRD1)の書き込みが完了する前に反転書込動作を終了し、メモリユニット(MU11)に書き込むべき書き込みデータ値(WD1)がメモリユニット(MU11)に書き込まれるようにメモリユニット(MU11)の第1および第2のフローティングゲートの電荷量を制御する通常書込動作を実行する。

(もっと読む)

NAND型フラッシュメモリ

【課題】ROMフューズブロックの領域の増加を抑制しつつ、試験中に新たに発生したバッドブロックの情報をより多く記憶することが可能なNAND型フラッシュメモリを提供する。

【解決手段】NAND型フラッシュメモリは、電源投入時において、第1の判定信号が入力され、第1の判定信号の論理をシフトさせながら記憶し、その後、テストモードにおいて、第2の判定信号が入力され、第2の判定信号のバッドブロックの判定に対応する論理のみがアドレスが対応する通常ブロックの論理に上書きされ、且つ、アドレス指定に連動して、記憶している論理が割り当てられたバッドブロックフラグ信号を順次出力するシフトレジスタ回路を備える。

(もっと読む)

不揮発性半導体記憶装置の領域設定方法および不揮発性半導体記憶装置

【課題】カンパニー領域専用のブロックが不要な不揮発性半導体記憶装置の領域設定方法を提供する。

【解決手段】不揮発性半導体記憶装置1のメモリセルアレイ2のブロックに不良ブロックが含まれていた場合に、ブロックにユーザー領域とカンパニー領域とを設定する方法において、メモリセルアレイは複数のバンクに分かれていて、各バンクはユーザー領域として使用する複数の通常ブロックと、1つ以上の冗長ブロックとを有していて、カンパニー領域を所定バンクの冗長ブロックに初期設定するステップと、通常ブロックのうちのいずれかが不良ブロックであった場合に、当該不良ブロックの代わりに使用する代替ブロックを、当該不良ブロックが属するバンクの冗長ブロックに設定するステップと、代替ブロックがカンパニー領域と重なった場合に、カンパニー領域を、空いている冗長ブロックに移動させるステップとを有している。

(もっと読む)

半導体記憶装置

【課題】チップ面積を縮小する。

【解決手段】半導体記憶装置は、メモリ10と、メモリ10との間のデータ転送を行い、第1のビット幅でデータを転送する第1のモードと、第2のビット幅でデータを転送する第2のモードとを有するデータ転送部17とを含む。データ転送部17は、メモリ10から読み出された第1のデータを保持する第1のラッチ回路70と、第1のモードにおいて、第1のデータのうち第1のビット幅を有する第2のデータを保持し、第2のモードにおいて、第1のデータのうち第2のビット幅を有する第3のデータを保持する第2のラッチ回路71と、第1のラッチ回路70と第2のラッチ回路71とを接続し、第1及び第2のモードで共有されるデータバスとを含む。

(もっと読む)

不揮発性半導体メモリ

【課題】 読み出し動作を高速に実行し、読み出しマージンを向上する。

【解決手段】 複数の不揮発性のレギュラーメモリセルにそれぞれ接続された所定数のレギュラービット線および所定数のレギュラーワード線とを各々含む一対のメモリ領域を有するレギュラーセクタと、一対のメインビット線と、一対のメモリ領域の間に配置され、一方および他方のメモリ領域のレギュラービット線を一方および他方のメインビット線にそれぞれ接続するスイッチと、リファレンスメモリセル、リファレンスビット線、リファレンスワード線を有するリファレンスセクタと、読み出し動作時に、リファレンスビット線を、データが読み出されるレギュラーメモリセルに接続されるメインビット線と異なるメインビット線に接続するリファレンススイッチと、メインビット線の電圧差を差動増幅するレギュラーセンスアンプとを有している。

(もっと読む)

電圧発生回路

【課題】 回路面積を縮小することが可能な電源発生回路を提供する。

【解決手段】 第1の昇圧回路11は、第1、第2動作モードにおいて、第1の電圧VPPを出力する。第1の出力回路15,16,17は、第1の昇圧回路に接続され、第1動作モード時に第1の電圧を第2の電圧VPGMHとして出力する。整流回路12は、第1の昇圧回路11に接続され、第1動作モード時に第1の電圧より低い第3の電圧VPGMINTを出力する。第2の出力回路18,19,20は、第1の昇圧回路11に接続され、第2動作モード時に整流回路12を短絡するとともに、第1の電圧VPPを第4の電圧VERAとして出力する。検知回路13は、第1、第2の出力回路から供給される第2、第4の電圧をそれぞれ検知する。

(もっと読む)

半導体記憶装置

【課題】面積縮小が可能なセンスアンプを備えた半導体記憶装置を提供すること。

【解決手段】本実施形態に係る半導体記憶装置は、データ(“0”または“1”)を保持するメモリセルが配置されたメモリセルアレイと、偶数ビット線と、奇数ビット線と、複数のセンスアンプとを備え、前記センスアンプは、前記メモリセルから読み出された前記データを保持するラッチ回路(PDC)と、配線(83)にゲートが接続され、前記データの読み出し時、前記配線の電位に応じて前記ラッチ回路に読み出し前記データを供給する第1トランジスタ(79)と、前記データの演算時、前記ラッチ回路に保持された前記データを前記配線に転送する第2トランジスタ(73)と、前記データの書き込み時、前記ラッチ回路に保持された前記データを前記配線に転送する第3トランジスタ(72)とを具備する。

(もっと読む)

メモリシステム

【課題】SLCフラッシュメモリとMLCフラッシュメモリとのそれぞれのメリットを状況に応じて得る。

【解決手段】実施の形態によるメモリシステム1は、MLCフラッシュメモリ112と、ブロック管理部102と、転記部(107、108および109)と、を備える。MLCフラッシュメモリ112は、SLCモードおよびMLCモードのいずれでもデータの書込みが可能な複数のブロックを含む。ブロック管理部102は、有効データを格納しないブロックをフリーブロックとして管理する。転記部は、ブロック管理部102が管理するフリーブロックの数が所定の閾値Tbf以下である場合、有効データを格納する1つ以上の使用ブロックを転記元ブロックとして選択し、転記元ブロックに格納されている有効データをフリーブロックにMLCモードで転記する。

(もっと読む)

半導体記憶装置

【課題】 面積の小さな半導体記憶装置を提供する。

【解決手段】 半導体記憶装置は、ラッチ回路を含んだバッファ13を含んでいる。所定数のラッチ回路からラッチ回路群が複数構成され、各ラッチ回路群において各ラッチ回路はそれぞれが転送回路を介して共通線に共通に接続されている。エラー訂正部3は、共通線と接続され、供給されたデータに含まれるエラービットの検出および訂正を行なう。データ転送制御部22は、ベリファイの対象のメモリセルからデータをバッファに読み出させ、所定数のラッチ回路群にわたって順次各ラッチ回路群中のラッチ回路が保持するデータの全てを対応する共通線に部分ベリファイデータとして読み出す。ベリファイ制御部21は、エラー訂正部に所定数のラッチ回路群の各々からの部分ベリファイデータの集合からなるベリファイデータに対してエラー検出を行なわせてベリファイデータ中のフェイルビットの有無を判定する。

(もっと読む)

不揮発性半導体記憶装置

【課題】 データの出力方向に柔軟性を持たせながら、小型化を図ることを可能とする不揮発性半導体記憶装置を提供する。

【解決手段】 不揮発性半導体記憶装置は、複数のメモリプレーンに跨ってワード線方向に沿って延びるワード線方向データバス線と、ワード線方向データバス線とビット線とを電気的に接続するか否かを切り替えるビットストリング選択回路と、ワード線方向データバス線に接続されるサブラッチ回路とを備える。ワード線方向データバス線、ビットストリング選択回路及びサブラッチ回路は、複数のメモリ領域の間においてワード線方向に沿って延びる帯状領域に設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】追加のマスクや追加のプロセスを必要とせず、トランジスタを含む半導体装置に搭載することが可能なメモリ素子を実現する。

【解決手段】半導体装置を、絶縁膜17と金属膜又は金属化合物膜19とを積層した構造を有するメモリ素子16と、メモリ素子16と同一の積層構造を有するゲート構造を持つトランジスタとを備えるものとする。

(もっと読む)

半導体記憶装置

【課題】各種の積層型マルチチップパッケージにおいて、各チップにチップアドレスを付して、各チップを区別することができる半導体記憶装置を提供する。

【解決手段】このメモリはイネーブル信号を受けるパッドをチップ間において共通に接続した複数のチップを積層して構成されている。チップアドレスメモリは自己のアドレスを示すチップアドレスを記憶できる。判定部は選択アドレスをチップアドレスと比較して一致判定を行う。制御信号設定部は判定部の判定に応じて制御信号を有効又は無効に設定する。チップアドレス設定部は複数のメモリセルに関するフェイルビット数に応じてチップアドレスをチップアドレスメモリへ格納するか否かを決定する。各チップは、メモリセルアレイ、チップアドレスメモリ、判定部、制御信号設定部およびチップアドレス設定部を備える。コントローラは、フェイルビット数に基づいて各チップに異なるチップアドレスを割り当てる。

(もっと読む)

1 - 20 / 140

[ Back to top ]