Fターム[5B125DB11]の内容

リードオンリーメモリ (43,397) | 書込動作 (3,780) | 書込信号制御 (1,782)

Fターム[5B125DB11]の下位に属するFターム

書込パルス電圧値制御 (722)

書込パルス幅制御 (94)

書込パルス印加回数制御 (63)

書込電流制御 (36)

所定量の電荷を注入 (28)

書込回数に対応して制御 (64)

メモリセルのしきい値レベルに対応して制御 (244)

多値の書込データに対応して制御 (406)

Fターム[5B125DB11]に分類される特許

1 - 20 / 125

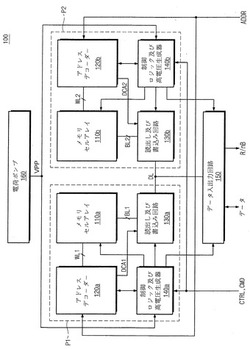

不揮発性メモリ装置及び不揮発性メモリ装置を制御するコントローラの動作方法

【課題】向上された動作速度を有する不揮発性メモリ装置及び不揮発性メモリ装置を制御するコントローラの動作方法を提供する。

【解決手段】本発明の不揮発性メモリ装置は、データのプログラム、読出し又は消去を遂行する第1プレーン、データのプログラム、読出し又は消去を遂行する第2プレーン、及び第1プレーン又は第2プレーンから共通バスを通じて伝送されるデータを外部へ出力し、外部から受信されるデータを、共通バスを通じて第1プレーン又は第2プレーンへ伝送するデータ入出力回路を含む。第1プレーンでプログラム、読出し又は消去が遂行される時、データ入出力回路は共通バスを通じて第2プレーンとデータを交換する。

(もっと読む)

フラッシュメモリの制御装置

【課題】フラッシュメモリの寿命を延ばすことができる、フラッシュメモリの制御装置を提供する。

【解決手段】フラッシュメモリの複数のブロックを、低頻度データブロックと高頻度データブロックに分ける。低頻度データブロックには、更新頻度の低いデータとして予め設定された低頻度データを記憶する。一方、高頻度データブロックには、更新頻度の高いデータとして予め設定された高頻度データを記憶する。そして、フラッシュメモリに新たに記憶させるデータの種類が低頻度データであれば低頻度データブロックに記憶させ、高頻度データであれば高頻度データブロックに記憶させる。

(もっと読む)

書き込み制御回路及び半導体装置

【課題】電気的に1回限りの書き込みが行われる記憶素子への誤書き込みを抑制する。

【解決手段】入力部11は、電気的に1回限りの書き込みが行われる記憶素子(電気ヒューズ素子2)への書き込みを指示する複数パルスの書き込み信号を入力し、書き込み制御部12は、入力された書き込み信号のパルス数が所定数に達するまで、電気ヒューズ素子2への書き込みを無効状態にすることで、書き込み信号の信号線にノイズやグリッジのような連続性の少ないパルスがのっても、これらのパルスにより直ちに書き込みトランジスタ3がオンすることが抑制される。

(もっと読む)

半導体不揮発性記憶装置

【課題】回路規模を削減する。

【解決手段】第1、第2の電源電圧を供給する第1、第2の電圧電源と、前記第1の電源電圧を検知する第1の検出回路と、ワード線を駆動するワード線駆動回路とを有し、前記ワード線駆動回路が、前記第1の電源電圧を供給され、出力信号を第1のノードに出力する第1のバッファ回路と、前記第1、第2の電源電圧を供給され、前記第1のノードの信号レベルに応じて前記ワード線を駆動する第2のバッファ回路を備え、前記第1のバッファ回路は、入力信号に応じて前記第1の電源電圧を出力信号として出力し、前記第1の検出回路は、前記第1の電源電圧の検知結果に応じて前記第1のノードのレベルを固定することで、前記第2のバッファ回路が前記第2の電源電圧で前記ワード線を駆動させる半導体不揮発性記憶装置。

(もっと読む)

メモリシステム

【課題】

実施形態は、動作効率の低減を防止可能なメモリシステムを提供する。

【解決手段】

本実施形態のメモリシステムによれば、半導体チップの内部温度とアクセス可否とを対応づけたデータを保持する第1記憶部と、前記半導体チップの内部温度を計測する温度計測部と、前記データから、計測された内部温度に対応するアクセス可否を算出し、アクセス可の半導体チップに対して、シーケンスを実行し、アクセス否の半導体チップに対して、シーケンスを実行しない制御部とを備えることを特徴とする。

(もっと読む)

半導体記憶装置

【課題】ベリファイ・フェイル数を精度良くカウント可能な半導体記憶装置を提供すること。

【解決手段】実施形態の半導体記憶装置1は、複数のメモリセルMTと、論理ゲートチェーン52と、カウンタ30を備える。メモリセルMTは、いずれかのカラムに関連付けられ、データ保持可能である。論理ゲートチェーン52は、いずれかのカラムに対応付けられ、且つ対応付けられたカラムにおけるベリファイ・フェイルの有無を示す論理レベルを次段に出力するように直列接続された複数の論理ゲート51を含む。カウンタ30は、直列接続の最終段の論理ゲートによる、ベリファイ・フェイルがあることを示す論理レベルの出力回数をカウントする。論理ゲートチェーン52は、各々の論理ゲート51の出力する論理レベルの示す内容が、ベリファイ・フェイルのあるカラムに対応する論理ゲート51を境界にして反転するように構成される。

(もっと読む)

半導体記憶装置

【課題】 各種のデータ転送が可能な半導体記憶装置を提供する。

【解決手段】 メモリセルアレイ10は、複数の不揮発性メモリセルが配置されている。RAM(Random Access Memory)30は、メモリセルアレイ10に書き込まれるデータ、又は読み出されたデータを保持する。制御部4は、RAMを用いた第1の動作モードと、RAMを用いない第2の動作モードを制御する。データ転送部17は、第2の動作モードにおいて、データの書き込み時、データバスDIRを介して入出力部40から供給されたデータをバッファ部12に転送し、バッファ部12に転送されたデータをエラー訂正部20に転送し、エラー訂正部20において、生成されたパリティデータをバッファ部12に転送する。

(もっと読む)

半導体記憶装置、及び記憶方法

【課題】書き込みデータにおける値の偏りを平準化する際に要する時間を短縮する。

【解決手段】半導体記憶装置は、第1の値と、第2の値とのいずれかを示すデータを記憶するメモリセルを複数有するメモリアレイと、メモリアレイに記憶させたデータにおいて、第1の値の数と、第2の値の数とのいずれが多いかを判定する転送済データ判定部と、外部から入力されるデータのデータ量がメモリアレイへの書き込み単位に達するごとに、メモリアレイに書き込むデータにおいて、第1の値と、第2の値とのいずれの値が多く含まれているかを判定する書込データ判定部と、転送データ判定部の判定結果及び書込データ判定部の判定結果に応じて、各ビットの値を反転させた書き込みデータと、書き込みデータとのいずれかを選択してメモリアレイに記憶させる書込データ選択部を備えている。

(もっと読む)

不揮発性半導体記憶装置およびそのデータ書き込み方法

【課題】負荷を平均化して複数ビットの同時書き込み処理を行うことができる不揮発性半導体記憶装置およびその書き込み制御方法の提供を図る。

【解決手段】書き込み対象の全ビットに対して割り当てる識別符号を生成する識別符号生成回路120〜1231と、最大同時書き込み可能ビット数を超えない範囲において、前記生成された識別符号に基づいて平均化された同時書き込みを行うビット数を算出する同時書き込みビット数算出回路15と、前記算出された同時書き込みビット数に従って書き込み範囲を算出する書き込み範囲算出回路16と、書き込みデータ、前記生成された識別符号および前記算出された書き込み範囲に基づいてプログラムパルスを生成するプログラムパルス生成回路130〜1331と、を有する。

(もっと読む)

半導体集積回路装置およびメモリの管理方法

【課題】製造コストを抑制し、小型化が可能な半導体集積回路装置およびメモリの管理方法を提供する。

【解決手段】半導体集積回路装置は、不揮発性メモリと、記憶部と、演算部と、を備える。不揮発性メモリは、第1および第2の領域を有する。記憶部は、前記第1の領域に外部からプログラムをダウンロードするための第1のプログラムを記憶した。演算部は、前記第1のプログラム、および、前記第1のプログラムにより前記第1の領域にダウンロードされたプログラムを実行する。前記第1の領域は、前記ダウンロードされたプログラムにより書き込みおよび消去可能であるが、前記第2の領域は、前記ダウンロードされたプログラムにより消去できない。

(もっと読む)

不揮発性半導体記憶装置、及び、メモリシステム

【課題】データ保持特性を向上することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、複数のメモリセルをそれぞれ含む複数のブロックを有し、前記複数のブロックのうちの通常ブロックに、通常のデータが記憶され、前記複数のブロックのうちのタイムコードブロックに、前記通常ブロック毎に設定され且つ前記通常ブロックの最後の書き込み動作を実行した時間に対応する時間データを含むタイムコードが記憶されたメモリセルアレイを備える。前記不揮発性半導体記憶装置は、前記タイムコードブロックから前記タイムコードを読み出し、現在の時間を取得し、読み出された前記タイムコードの時間データの時間と前記現在の時間との時間差が規定値よりも大きくなる選定された前記通常ブロックに対して、データを読み出し、消去し、且つ、読み出されたデータを書き込み、前記現在の時間の時間データに対応する新たなタイムコードを、選定された前記通常ブロックに対応させて、前記タイムコードブロックに書き込む。

(もっと読む)

不揮発性半導体記憶装置

【課題】 本実施形態は、消去動作中に読み出し又は書き込み動作要求が発生した場合、要求発生から短時間で読み出し又は書き込み動作を実行することが可能であり、しかも、消去動作再開後、過消去状態の発生を防止可能な不揮発性半導体記憶装置を提供する。

【解決手段】 メモリセルアレイ1は、複数のメモリセルがマトリックス状に配置されている。制御部7は、メモリセルMCのデータを消去する。制御部7は、メモリセルMCの消去動作中に、第1のコマンドに応じて消去動作を中断させ、前記中断前の消去条件を保持し、第2のコマンドに応じて保持された消去条件に基づき消去動作を再開させる。

(もっと読む)

マルチチップパッケージおよびメモリチップ

【課題】消費電流のピーク値を低減する。

【解決手段】複数のメモリチップと、クロック発生回路と、クロック配線とを備える。複数のメモリチップは、夫々、メモリセルアレイと、メモリセルアレイに印加する電位を生成する電位発生回路と、メモリセルアレイに電位発生回路が生成した電位を印加してメモリセルアレイに対するアクセスを行う周辺回路とを備えている。クロック発生回路は、クロック信号を生成する。クロック配線は、クロック発生回路が生成したクロック信号を複数のメモリチップの夫々に共通入力する。ここで、複数のメモリチップは、夫々、クロック配線から入力されるクロック信号にメモリチップ毎に異なる時間の遅延を加えるクロック遅延回路をさらに備え、周辺回路は、電位発生回路が生成した電位をクロック遅延回路が遅延させたクロック信号に基づくタイミングでメモリセルアレイに印加する。

(もっと読む)

半導体メモリ

【課題】 メモリセル間の容量干渉を低減し、かつ短時間でデータの書込みを行うことができる半導体メモリを提供する。

【解決手段】 本発明の半導体メモリ10は、行列状に配列されかつi値データを記憶可能な不揮発性のメモリセルを含み、複数のメモリセルが直列に接続されて1つのセルユニットを構成し、各ユニットセルが対応する列方向のビット線に接続され、行方向のメモリセルが対応するワード線に接続されたメモリセルアレイと、ページを選択する選択手段と、書込みデータを保持する保持手段と、保持手段に保持された書込みデータを用いて選択されたページに書込みを行う書込み制御手段とを有する。書込み制御手段は、選択ページに書込みを行うDBL書込みシーケンスと、DBL書込みシーケンス後に、選択ページを複数のグループに分割し、分割されたグループ毎に書込みを行うOneway書込みシーケンスとを有する。

(もっと読む)

メモリモジュールとコントローラ

【課題】フラッシュメモリのアクセス時間とSDRAMのアクセス時間との整合を図り、大容量フラッシュメモリを含むメモリモジュールとコントローラを提供する。

【解決手段】フラッシュメモリと、SDRAMと、フラッシュメモリ及びSDRAMの夫々のアクセスを制御し、外部からのストア命令に従って、SDRAMに記憶されるデータをフラッシュメモリに転送するための制御回路とそれに結合された複数の入出力端子を含む。制御回路は、ストア命令に従ってSDRAMに記憶されるデータをフラッシュメモリに転送している間に、SDRAMからのデータ読出し命令が入力された場合において、そのデータ転送を中断し、読み出し命令に従ってSDRAMに記憶されるデータを外部に出力するよう制御する。

(もっと読む)

電源切換回路、不揮発性記憶装置、集積回路装置及び電子機器

【課題】メモリーセルのデータが意図せずに書き換えられることを防止できる電源切換回路、不揮発性記憶装置、集積回路装置及び電子機器等を提供すること。

【解決手段】電源切換回路は、第1の高電位電源VPP及び第1の高電位電源VPPよりも低電位の第2の高電位電源VDDのいずれか一方を選択して、供給電源として出力する電源選択回路100と、切換制御信号SGに基づいて電源選択回路100を制御する制御回路200とを含む。制御回路200は、第1、第2の高電位電源VPP、VDDの電圧レベルが共に立ち上がるまでは、電源選択回路100が供給電源として第1の高電位電源VPPを出力しないように電源選択回路を制御し、第1、第2の高電位電源VPP、VDDの電圧レベルが共に立ち上がった後に、切換制御信号SGに基づいて、電源選択回路100が第1、第2の高電位電源VPP、VDDのいずれか一方を供給電源として出力するように電源選択回路100を制御する。

(もっと読む)

不揮発性フラッシュメモリ

【課題】低消費電力、低減されたリーク問題、および単純なプロセスを伴った新規なフラッシュメモリ、新規なプログラミング方法、およびそのセンシングスキームを提供する。

【解決手段】ワード線218、第1のビット線204、および第2のビット線206を備えた不揮発性メモリセル200を動作させる方法は、メモリセル200をプログラミングする工程を有し、そのプログラミングする工程が、高い正電圧のバイアスを第1のビット線に印加し、接地バイアスを第2のビット線に印加し、高い負電圧のバイアスをワード線に印加することを備え、正帯電ホールが誘電体層212を介してトラッピング層214に突き抜けるようにする。

(もっと読む)

半導体記憶装置

【課題】 半導体記憶装置において、キャッシュリードの速度を向上可能とする。

【解決手段】 記憶素子MCは、k値の閾値(kは2以上の自然数)を有する。第1及び第2の記憶回路10は、メモリセルより読み出されるデータ、又は外部から入力されるデータを記憶する。制御部7は、第1の記憶回路及び第2の記憶回路のデータに応じて、記憶素子をn値(n<=k)の閾値に設定する書き込み動作を行い、記憶素子の少なくとも1値の書き込みが終了した場合、書き込み動作を一旦中断して、メモリセルからの読み出し動作を行い、この読み出されたデータを第1の記憶回路に記憶し、書き込み動作を再開する。

(もっと読む)

半導体記憶装置

【課題】メモリセルに負の閾値電圧を設定することができ、しかも安定な動作が可能な半導体記憶装置を提供する。

【解決手段】ワード線、及びビット線に接続された複数のメモリセルがマトリックス状に配置され、前記メモリセルに負の閾値電圧を設定することが可能なメモリセルアレイと、前記ワード線、及びビット線の電位を制御する制御回路と、前記制御回路は、前記ビット線のうち第1のビット線BLoに接続されたメモリセルから負の閾値電圧の読み出し動作を行なう場合、前記第1のビット線に隣接して配置された第2のビット線BLeと、前記メモリセルアレイが形成されたウェルと、前記メモリセルアレイのソース線SRCに、正の第1の電圧Vfixを供給し、選択セルのワード線に前記第1の電圧より低い正の電圧を供給する。

(もっと読む)

メモリ制御装置、及びメモリ制御方法

【課題】プログラムの暴走により、意図しないメモリへの書き込みを防止する。

【解決手段】メモリ書き込み制御装置は、命令を実行する処理部17と、処理部17から不揮発性メモリ11への書き込み命令信号が入力されると、電源電圧に基づいて、不揮発性メモリ11への書き込みを許可するプロテクト部(プロテクト回路10)と、を備える。処理部17のCPU5がユーザプログラムの命令を実行する電圧と、メモリへの書き込みの命令を実行する電圧とを異なる範囲に設定し、電源電圧に応じて、不揮発性メモリ11への書き込みを制御する。

(もっと読む)

1 - 20 / 125

[ Back to top ]