Fターム[5B125DB16]の内容

リードオンリーメモリ (43,397) | 書込動作 (3,780) | 書込信号制御 (1,782) | 所定量の電荷を注入 (28)

Fターム[5B125DB16]に分類される特許

1 - 20 / 28

不揮発性プログラマブルスイッチ

【課題】セル面積の小さい不揮発性プログラマブルスイッチを提供する。

【解決手段】第1配線に接続される第1端子と第2配線に接続される第2端子と第3配線に接続される第3端子とを有する第1不揮発性メモリトランジスタと、第4配線に接続される第4端子と第2配線に接続される第5端子と第3配線に接続される第6端子とを有する第2不揮発性メモリトランジスタと、第2配線にゲート電極が接続されたパストランジスタと、を備え、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも高い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が増加し、第2不揮発性メモリトランジスタの閾値電圧が低下し、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも低い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が低下し、第2不揮発性メモリトランジスタの閾値電圧が増加する。

(もっと読む)

半導体記憶装置

【課題】読出速度が速い半導体記憶装置を提供する。

【解決手段】フラッシュメモリ3は、選択ビット線BLをプリチャージするプリチャージ回路45と、定電流源50と、電流検知型のセンスアンプ23と、選択ビット線BLがメモリアレイMA2に属する場合は、選択ビット線BLおよび定電流源50をそれぞれセンスアンプ23の入力ノードLBT,LBBに接続し、選択ビット線BLがメモリアレイMA3に属する場合は、選択ビット線BLおよび定電流源50を入力ノードLBB,LBTに接続する切換回路SWT2,SWB2,SWとを含む。したがって、ビット線BLのプリチャージとデータ読出を並列に実行できる。

(もっと読む)

半導体記憶装置およびデータ書込み方法

【課題】MOS構造を有する各メモリセルにおいて信頼性が高い2ビットのデータの記憶が容易な半導体記憶装置およびデータ書込み方法を提供する。

【解決手段】MOS構造を有するメモリセル10は、ゲート電極13の第1半導体領域121側に設けられた第1記憶部141と、ゲート電極13の第2半導体領域122側に設けられた第2記憶部142とを有する。第1記憶部141に電子を保持させる第1電荷移動ステップと、第2記憶部142に電子を保持させる第2電荷移動ステップとを交互に行うことで、第1記憶部141および第2記憶部142の双方に所定量の電子を保持させる。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルに保持されたデータの信頼性を向上させることを可能にした不揮発性半導体記憶装置を提供する。

【解決手段】一態様に係る不揮発性半導体記憶装置は、メモリセルアレイ、及び制御回路を有する。メモリセルアレイは、複数の閾値電圧分布を保持可能に構成された複数のメモリセル、及び複数のメモリセルのゲートに共通接続された複数のワード線を含む。制御回路は、メモリセルに少なくとも一部が負の閾値電圧分布を与え、これによりメモリセルのデータを消去する消去動作の実行後、メモリセルに正の複数通りの閾値電圧分布のうち最も低い閾値電圧分布を与える複数回の第1書込動作を実行する。制御回路は、複数回の第1書込動作の実行時に消去動作及び第1書込動作を除くその他の動作を実行させる第1実行命令をコントローラから受け付けた場合、複数回の第1書込動作の間にその他の動作を実行する。

(もっと読む)

半導体不揮発性メモリ及びデータ書き込み方法

【目的】迅速に且つ精度良く書込データに対応した所定量の電荷をメモリセルの電荷蓄積部に蓄積させることが可能な半導体不揮発性メモリ及びデータ書き込み方法を提供することを目的とする

【構成】書込データに対応した書込電圧をメモリセルのドレイン領域又はソース領域に印加することにより、このメモリセルに形成されている電荷蓄積部に電荷を注入するにあたり、電荷蓄積部に蓄積された電荷量の増加に応じて書込電圧を低減する。

(もっと読む)

プログラム電流クランプを有する不揮発性メモリ素子及び関連する方法

【課題】 本発明は、プログラム電流クランプを有する不揮発性メモリ素子及び関連する方法を提供する。

【解決手段】 選択トランジスタとメモリ・トランジスタとを有する不揮発性メモリ・セルをプログラミングする方法が提供される。当該方法は:前記メモリ・セルの第1の入力に予め設定された制限電流を印加する段階;前記メモリ・セルの第2の入力に電気的に接続された電流制限回路に制限電圧を印加する段階;前記メモリ・セルの電圧降下を安定化させるために制限電圧を印加する段階;前記電流制限回路により決定された予め設定された制限された電流で前記メモリ・セルをプログラミングするために、前記メモリ・セルに傾斜したゲート電圧を印加する段階;を有する。

(もっと読む)

半導体不揮発性メモリ装置

【課題】 占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】 ドレイン領域内のトンネル領域と微細穴に埋め込まれる形で形成されたフローティングゲート電極の側面との間にはトンネル絶縁膜を設け、微細穴に接するドレイン領域の表面付近には、電気的にフローティング状態である第1導電型のトンネル防止領域を設けた。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】ドレイン領域内のトンネル領域には、ドレイン領域と同一の電位に固定されたドレイン領域に比べて不純物濃度の低い第2導電型の領域と、不純物濃度の低い第1導電型の領域とを形成し、不純物濃度の低い第2導電型の領域と、不純物濃度の低い第1導電型の領域のそれぞれの上面に、フローティングゲート電極への電子注入用と電子引き抜き用のトンネル絶縁膜を独立して設けた。また、データ書き換え時に印加されるストレスが偏らないように、電子引き抜き用のトンネル絶縁膜に比べて電子注入用のトンネル絶縁膜の面積を大きくあるいは厚くした。

(もっと読む)

半導体不揮発性メモリ

【課題】 本発明は、不揮発性メモリ・セルにおける電荷貯蔵層を論理工程において形成する方法を提供する。

【解決手段】 論理工程において不揮発性メモリ・セルにおける電荷貯蔵層を形成する方法は、基板のアクティブ領域の上にセレクト・ゲートを形成するステップ、その基板のアクティブ領域に部分的に重なる長いポリシリコン・ゲートを形成するステップ、及びその長いポリシリコン・ゲートの間に電荷貯蔵層を充填するステップを含む。

(もっと読む)

不揮発性半導体メモリ

【課題】データ書込み時における電流量の変化を抑制し、メモリセルへのデータ書込みを高精度に行うことができる不揮発性半導体メモリを提供する。

【解決手段】複数のメモリセルと、複数のメモリセルに接続されたワード線と、複数のメモリセルの各々に接続されたビット線と、を含み、ビット線から少なくとも2つを選択し、選択されたビット線に接続されたメモリセルに対して、電源供給ラインから同時に電流を供給してデータを書込む不揮発性半導体メモリであって、複数のメモリセルの各々に蓄積された電荷量を測定する電荷量測定部と、ビット線の各々に接続された電流路切替回路と、を有し、選択されたビット線に接続された電流路切替回路は、電荷量測定部による電荷量の測定値に応じて、メモリセル又は所定端子のいずれかに対して選択的に電源供給ラインから電流を供給すること。

(もっと読む)

半導体不揮発記憶回路

【課題】データが書き込まれていない状態(製造直後の状態)で、データ読み出し時の出力論理が不定とならない不揮発性メモリセルを提供する。

【解決手段】半導体不揮発記憶回路は、1ビットのデータを格納するメモリセルCELとして、第1トランジスタN1と、第1トランジスタN1よりもオン電流の高い第2トランジスタN2と、を一対としたトランジスタペアを集積化して成り、前記メモリセルは、第2トランジスタN2のオン電流が第1トランジスタN1のオン電流よりも高い状態をデータ「0」の記憶状態とし、逆に第2トランジスタN2のオン電流が第1トランジスタN1のオン電流よりも低い状態をデータ「1」の記憶状態とする。

(もっと読む)

NAND型フラッシュメモリ

【課題】メモリセルの閾値電圧の分布幅の拡大を抑制することが可能なNAND型フラッシュメモリを提供する。

【解決手段】NAND型フラッシュメモリは、半導体基板表面のウェル上に第1の絶縁膜を介して形成され周囲から絶縁された電荷保持層と、前記電荷保持層との間に第2の絶縁膜を介して設けられた制御ゲートと、を有し、且つ前記電荷保持層に保持された電荷量に応じた閾値電圧に対応して情報が記憶されるメモリセルトランジスタと、前記制御ゲートに印加する電圧、および前記ウェルに印加する電圧を制御することにより、前記メモリセルトランジスタの動作を制御する制御回路と、を備える。

(もっと読む)

半導体装置、及び、記憶セルの記憶状態の補正方法

【課題】データ化けの防止の対処の時間を短縮できる半導体装置を提供する。

【解決手段】不揮発性の記憶セルの蓄積状態が経時劣化し蓄積状態の書き込み時の制御ゲートの閾値電圧Vfより低く制御ゲートの通常読出し時電圧Vreadより高い蓄積劣化検出電圧VchkHに、閾値電圧が達した場合に蓄積処理をし、不揮発性の記憶セルの消去状態が経時劣化し消去状態の書き込み時の制御ゲートの閾値電圧Veより高く制御ゲートの通常読出し時電圧Vreadより低い消去劣化検出電圧VchkLに、閾値電圧が達した場合に消去処理をする半導体装置であって、その蓄積処理によって、閾値電圧を、蓄積状態の書き込み時の制御ゲートの閾値電圧Vfより低く、蓄積劣化検出電圧VchkHより高く設定し、その消去処理によって、閾値電圧を、消去状態の書き込み時の制御ゲートの閾値電圧Veより高く、消去劣化検出電圧VchkLより低く設定する。

(もっと読む)

不揮発性半導体メモリ装置の消去方法

【課題】保持特性に優れた不揮発性半導体メモリ装置の消去方法を提供することである。

【解決手段】ソース・ドレイン領域2、3が離間して形成された半導体基板1と、半導体基板1上に形成された第1の絶縁層7と、第1の絶縁層7上の第1の領域10に形成された第1のゲート電極5と、第1の絶縁層7上の第2の領域11、12に形成された電荷蓄積層8と、電荷蓄積層8上に形成された第2の絶縁層9と、第2の絶縁層9上に形成された第2のゲート電極4、6と、を有する不揮発性半導体メモリ装置の消去方法は次のステップを有する。ソース・ドレイン領域から電荷蓄積層にホットホールを注入するステップ。電荷蓄積層の第1のゲート電極側の領域にチャネルホットエレクトロンを注入するステップ。

(もっと読む)

不揮発性記憶装置の書込み処理の改善

【課題】不揮発性記憶装置の書込み処理で、部分的な書換え可能とし、書込みマージンを増やし、書き込み時間を短縮する。

【解決手段】消去処理を不要とし、書込み処理で電荷の抜取りを書込み値に応じて実施して、記憶内容の部分的書換えを可能にする。書込み非対象のワード線とビット線には中位から1/3の逆電圧を加え、書込み非対象の記憶素子への誤書込みを防ぐ。書込み値に応じて、電荷の調整開始電圧を変更し、書込み値に係らず並行して書込みを実行し、電荷の調整回数を減少させて、書込み時間を短縮する。

(もっと読む)

半導体装置へのデータ書き込み方法、半導体装置

【課題】フラッシュメモリのメモリセルへの書き込み時に、絶縁膜に電荷が残っている場合でも書き込み確認処理を安定して行うことができる方法を提供する。

【解決手段】半導体基板10にソースS及びドレインDが形成されており、ソースSとドレインDに挟まれた領域の半導体基板10上に、絶縁層12に囲まれた浮遊ゲート13と制御ゲート11とが積層された半導体記憶装置1にデータを書き込む方法である。まず、制御ゲート11に所定の電圧を印加し、ドレインDに正電圧を印加し、ソースSに接地電圧を印加して浮遊ゲート13に電荷を注入する。次いで、制御ゲート11に所定の電圧と同じ極性の電圧を印加し、ドレインDに負電圧を印加し、ソースSに接地電圧を印加して浮遊ゲート13に注入された電荷の確認を行う。

(もっと読む)

NAND型フラッシュメモリ

【課題】メモリセルのしきい値電圧の分布幅の拡大を抑制することが可能なNAND型フラッシュメモリを提供する。

【解決手段】NAND型フラッシュメモリ100の前記制御回路は、書き込み動作時に、前記制御ゲートと前記ウェルとの間に、書き込み電圧を印加することにより、前記電荷保持層に電荷を注入し、その後、ベリファイリード動作を行う前に、前記制御ゲートと前記ウェルとの間に前記書き込み電圧とは逆極性であり前記書き込み電圧よりも絶対値が小さいデトラップ電圧を印加することにより、前記ウェルと前記電荷保持層との間に設けられた酸化膜または窒化された酸化膜にトラップされた電荷をデトラップする。

(もっと読む)

不揮発性メモリ素子の動作方法

【課題】不揮発性メモリ素子の動作方法を提供する。

【解決手段】本発明は、複数のメモリセルを含む不揮発性メモリ素子において、複数のメモリセルのうち、データが記録された選択されたメモリセルに隣接するように連結された少なくとも一つのメモリセルのチャンネルを通じて、選択されたメモリセルのチャンネルにブースト電圧を誘導して記録されたデータを安定化させるステップを含むことを特徴とする不揮発性メモリ素子の動作方法を提供する。

(もっと読む)

情報書込方法、情報読出方法、半導体装置、及び半導体装置の製造方法

【課題】半導体装置の製造工程数を少なくする為に、トランジスタを不揮発メモリ素子として利用する為の情報書込方法を提供する。

【解決手段】第1ゲート絶縁膜及び第1ゲート電極を具備する第1トランジスタ10b、並びに第1ゲート絶縁膜と同じ厚さの第2ゲート絶縁膜及び第1ゲート電極と同じ形状の第2ゲート電極を具備していて第1トランジスタと同一導電型の第2トランジスタ10bを具備する半導体装置に情報を書き込む情報書込方法であって、第1ゲート絶縁膜に電子又は正孔を捕捉させて、第1トランジスタの閾値電圧の絶対値を低下させて規定値超にし、かつ第2トランジスタの閾値電圧の絶対値を規定値未満に維持することにより、第1トランジスタ10b及び第2トランジスタ10bの一方に0を記憶させ、他方に1を記憶させて情報を書き込む。

(もっと読む)

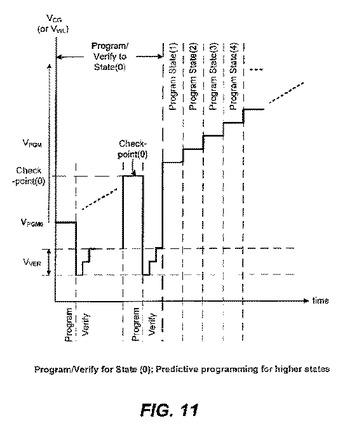

不揮発性メモリと予測プログラミングの方法

1つの範囲のしきい値電圧レベルのうちの1つにそれぞれプログラムされ得るメモリセルのアレイを有する不揮発性メモリにおいて、予測プログラミングモードが提供され、このモードにおいて、所与のメモリセルを所与の目標しきい値電圧レベルにプログラムするためにどれほどのプログラミング電圧レベルを印加する必要があるかを所定関数が予測する。このようにして、ベリファイ動作を行う必要はなく、これによりプログラム動作の性能を大幅に改善する。1つの好ましい実施形態では、所定関数は線形であり、プログラムされる各メモリセルのために1つ以上のチェックポイントにより較正される。チェックポイントは、問題のメモリセルをベリファイされる指定されたしきい値電圧レベルにプログラムする実際のプログラミング電圧である。  (もっと読む)

(もっと読む)

1 - 20 / 28

[ Back to top ]