Fターム[5B125DE08]の内容

リードオンリーメモリ (43,397) | その他の動作 (2,583) | エラー検出訂正動作 (491)

Fターム[5B125DE08]に分類される特許

1 - 20 / 491

メモリシステム及びそれのブロック複写方法

ホスト装置、装置、システム

不揮発性メモリにおける書き込み欠陥からのデータ保護

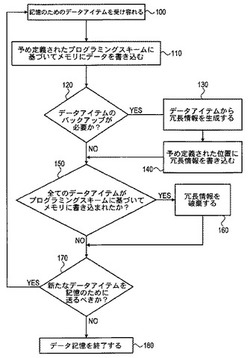

【課題】メモリ装置の書き込み欠陥からデータを保護するための方法及びシステムを提供する。

【解決手段】この方法は、データアイテムのセットにわたる冗長情報を計算し、データアイテムを、メモリに記憶するために送信することを含む。冗長情報は、データアイテムがメモリに首尾良く書き込まれるまでの間のみ保持され、次いで、破棄される。データアイテムは、それをメモリに書き込むのに欠陥が生じたとき、冗長情報を使用して回復される。

(もっと読む)

メモリシステム及びそれの動作方法

【課題】動作速度及び電力消耗を減らすことができるメモリシステム及びそれの動作方法が提供される。

【解決手段】本発明の実施形態によるメモリシステムは不揮発性メモリ装置と、前記不揮発性メモリ装置を制御するように構成されたメモリ制御器と、を含み、前記メモリ制御器は前記不揮発性メモリ装置から読み出されたデータのエラーの位置情報を含むエラーフラッグ情報を前記不揮発性メモリ装置へ提供する。

(もっと読む)

半導体ディスク寿命監視装置

【課題】不揮発性の半導体ディスクの寿命を監視する半導体ディスク寿命監視装置を提供する。

【解決手段】半導体ディスク5−1〜5−Kの書込み制御を行うファイルシステム3と、当該ファイルシステム3と前記半導体ディスク5−1〜5−Kを接続するインタフェースドライバ4を備え、当該インタフェースドライバ4により書込みが行われる半導体ディスク5−1〜5−Kの寿命を予測する半導体ディスク寿命監視装置1であって、前記ファイルシステム3からの書込みを書込情報として測定する測定部7と、前記測定結果を累積し第1の保存データ32として保存する保存部8と、前記保存した累積書込情報に基づいて、半導体ディスク5−1〜5−Kの寿命を予測する。

(もっと読む)

メモリ装置

【課題】、復号効率のよいメモリカード3を提供する。

【解決手段】メモリカード3は、複数のメモリセル13Dと、HB読み出し電圧とSB読み出し電圧とを、メモリセル13Dに印加する制御を行うCPUコア11と、閾値電圧をもとにLLRテーブルから取得したLLRに基づき軟判定復号を行うECC部1と、を具備し、第1のLLRテーブル20Aから取得したLLRに基づいた復号が失敗した場合に、最高電圧の第1のHB読み出し電圧H07を中心とする閾値電圧分布を測定し、閾値電圧分布の最小頻度電圧VMと第1のHB読み出し電圧H07との差である第1のシフト値ΔV1が「負」の場合には、第2のLLRテーブル20Bから取得したLLRに基づき復号を行い、第1のシフト値ΔV1が「正」の場合には、第3のLLRテーブル20Cから取得したLLRに基づき復号を行う。

(もっと読む)

不揮発性メモリ装置及びそのソフト判定読出し方法

【課題】不揮発性メモリ装置に対して、読出し/プログラム時間を短縮できる、向上された読出しスキームを提供する。

【解決手段】本発明の一特徴に係る不揮発性メモリ装置のソフト判定読出し方法は、ソフト判定読出し命令を受信し、選択されたワードラインへ読出し電圧を印加し、前記選択されたワードラインの選択されたメモリセルに各々連結されたビットラインをプリチャージし、前記ビットラインのプリチャージされた電圧及び前記選択されたワードラインに供給された読出し電圧は変化されない状態で、前記選択されたメモリセルの状態を連続的に感知することを含む。

(もっと読む)

不揮発性メモリ装置のデータリード方法、及びそれを行う装置

【課題】新たなリードパラメータで不揮発性メモリ装置をリードするリードリトライを行う方法、該方法を行う装置を提供する。

【解決手段】リードリトライ動作及び/またはその部属的なリードリトライ動作は、リードリトライ動作が保証(warranted)されるか否かを判断する前に初期化されるか、完了することができる。例えば、NANDフラッシュメモリ装置のページは、新たなリード電圧レベルをページのワードラインに印加して、リードリトライ動作でリードされうる。例えば、リードリトライ動作は、エラー訂正動作でターゲットページのデータの以前リードページのエラーを訂正不能と判断される前に、ターゲットページで行われる。

(もっと読む)

メモリ装置およびメモリ装置の制御方法

【課題】メモリセル31が劣化した場合にも、誤り訂正回路20の回路面積を増大させることなく誤り訂正を行うことができるメモリ装置2を提供する。

【解決手段】実施の形態のメモリ装置2は、メモリ部30と、制御部11と、補正部41と、誤り検出訂正部40とを具備する。メモリ部30は、データを記憶する複数のメモリセル31からなる。制御部11は、電荷量に対応した閾値電圧を読み出すためにメモリセル31にHB読出電圧HVと、補間読出電圧AVと、を印加する制御を行う。補正部41は読み出された、閾値電圧Vthから決定されたビットデータを反転する。誤り検出訂正部40は、補正部41で反転されたビットデータを含めた所定長のデータ列を、硬判定復号符号により復号処理を行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】 不揮発性半導体記憶装置の信頼性を、より向上させる技術が望まれている。

【解決手段】 閾値レベルの相違によって少なくとも4つのデータ状態が定義され、複数のデータ状態の各々に、複数ビットで構成される値が割り当てられるメモルセルがメモリ部に複数配置される。コントローラが、メモリセルの各々が記憶する複数ビットのうち、少なくとも1つのビットを、「正常」及び「異常」のいずれかの状態を表すエラー訂正ビットとし、他のビットを、データを記憶するためのデータビットとする。複数のデータ状態を、閾値レベルの大きさの順番に並べたとき、連続する4つのデータ状態のうち、閾値レベルが最小及び最大のデータ状態のエラー訂正ビットに「正常」を割り当て、閾値レベルが中間の2つのデータ状態のエラー訂正ビットに「異常」を割り当てる。周期的にメモリセルのエラー訂正ビットのデータを読み出し、読み出された値が「異常」である場合には、当該メモリセルのエラー訂正ビットを「正常」に再設定する。

(もっと読む)

情報処理装置及び半導体記憶装置

【課題】製造コストの低減に対して有利な情報処理装置及び半導体記憶装置を提供する。

【解決手段】実施形態によれば、ホスト装置と、前記ホスト装置にバスを介して接続された半導体記憶装置とを備える情報処理装置であって、前記ホスト装置は、メインメモリを備え、前記半導体記憶装置は、第1の論物変換テーブル及びデータを格納する不揮発性半導体メモリと、前記第1の論物変換テーブルの一部である第2の論物変換テーブルを格納する記憶部と、前記第2の論物変換テーブルを参照し前記不揮発性半導体メモリにアクセスする制御部とを備え、前記第1の論物変換テーブルの少なくとも一部が前記メインメモリ上にコピーされ、前記第2の論物変換テーブルに前記制御部がアクセスする論理アドレス又は物理アドレスが登録されていない場合、前記メインメモリ上の第3の論物変換テーブルの一部が前記第2の論物変換テーブルにコピーされる。

(もっと読む)

半導体記憶装置

【課題】ライトパラメータを効率よく探索することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、パラメータセットを初期値から変更して生成した新たな2以上のパラメータセットを用いて半導体メモリセルに情報を書き込み、その半導体メモリセルについて変換回路の出力を取得し、変換回路の出力の最大値が得られたパラメータセットと、最小値が得られたパラメータセットとをパラメータ空間上で結ぶ延長上に位置する、他のパラメータセットを、新たな初期値として設定して検証を再実施し、書き込んだ情報と読み出した情報が一致する半導体メモリセルについては、初期値を用いた検証を終了する。

(もっと読む)

不揮発性メモリ装置、不揮発性メモリ装置の消去方法、不揮発性メモリ装置の動作方法、不揮発性メモリ装置を含むメモリシステム、メモリシステムの動作方法、不揮発性メモリ装置を含むメモリカード、及びソリッドステートドライブ

【課題】向上された信頼性を有する不揮発性メモリ装置、不揮発性メモリ装置の消去方法、不揮発性メモリ装置の動作方法、不揮発性メモリ装置を含むメモリシステム、及びメモリシステムの動作方法が提供される。

【解決手段】本発明の消去方法は複数のメモリセルに消去電圧を供給する段階、複数のメモリセルのワードラインに読出し電圧に読出し動作を遂行する段階、及び複数のメモリセルのワードラインの少なくとも1つのワードラインに消去検証電圧を利用して消去検証動作を遂行する段階を含む。消去検証電圧は読出し電圧より低い。

(もっと読む)

半導体装置

【課題】データの信頼性の向上を実現可能な半導体装置を提供する。

【解決手段】例えば、それぞれ独立の内部電源生成回路VGEN1〜VGEN3を持つ3個の不揮発性メモリモジュールFMD1〜FMD3を備える。外部書き込みデータが入力された際には、それを2分割したデータの一方がFMD1のデータ領域DT[1a]に書き込まれ、他方がFMD2のデータ領域DT[1b]に書き込まれる。更に、この2分割したデータによってパリティデータが生成され、それがFMD3のデータ領域PT[1]に書き込まれる。このDT[1a],DT[1b],PT[1]への書き込みは、互いに重複しない期間で行われ、また、各データ領域(例えばDT[1a])に書き込みを行う前後で対応する書き込みスタンプ領域(例えばPS[1a])に識別子が書き込まれる。

(もっと読む)

フラッシュメモリ装置

【課題】フラッシュメモリ装置において、ブロック間で最新値をコピーしている間にリセットが発生した場合であっても、真の最新値を認識することにある。

【解決手段】ブロック管理値をアクティブ状態とする際に、ブロック管理値がブロック毎に異なるとともに順に大きくなるように設定される。例えば、ブロック管理値として第1のブロックB1には「$1111」が、第2のブロックB2には「$1112」が記憶される。このため、たとえ、アクティブ状態であるブロックが複数存在する場合であっても、ブロック管理値が大きいブロックの最新値を読み出すことで、真の最新値を読み出すことができる。

(もっと読む)

記録再生装置

【課題】フラッシュメモリの劣化をより迅速に検出できる。

【解決手段】速度導出部180は、SSD136に対するデータの読み書き速度を導出する。速度保持部138は、速度導出部が導出した読み書き速度を保持する。劣化判定部182は、任意の時点のSSDに対するデータの読み書き速度の、速度保持部に保持されている任意の時点より前の読み書き速度に対する変化率を導出し、導出された変化率が所定の閾値以下となると、SSDが劣化していると判定する。報知部184は、劣化判定部が、SSDが劣化していると判定した場合、その旨報知する。

(もっと読む)

不揮発性半導体メモリシステムおよびそれを備えたストレージデバイス

【課題】大量のビットエラーの修復が可能で、かつデータの長期保証が可能な不揮発性半導体メモリシステムを提供する。

【解決手段】不揮発性半導体メモリシステムは、メモリコア(10)と、コントローラ(20)と、コマンドに従って、コントローラ(20)を制御するデータ修復システム(30)とを備え、データ修復システム(30)は、メモリセルのしきい値を変化させるしきい値変更機能と、メモリセルにゲート電圧を印加して、データを読み出すデータ読出機能と、読み出したデータとゲート電圧とに基づいて、しきい値を算出するしきい値算出機能と、しきい値変更機能の動作結果と、算出したしきい値とに基づいて、真のデータを判別する判別機能と、判別機能による判別結果に基づいて、ビットエラーを修復する修復機能とを有しており、これら機能のうち、コマンドを実行するために必要な機能を動作させて、コマンドの実行結果を出力する。

(もっと読む)

不揮発性メモリ装置

【課題】信頼性を向上させることができる不揮発性メモリ装置の提供。

【解決手段】メモリセルアレイの選択されたページからデータを読み出すか、或いはメモリセルアレイの選択されたページへ書き込むように構成されたページバッファ回路と、選択されたページに割り当てられたシードに基づいて、ページバッファ回路へ伝送されるか、或いはページバッファ回路から伝送されるデータをランダム化及びデランダム化するように構成されたランダム化及びデランダム化回路と、を有し、選択されたページは複数のセグメントで構成され、ランダム化及びデランダム化回路は、選択されたページに割り当てられたシードに基づいて選択されたページのアクセス要請されたセグメントの各々に対するランダムシークェンスを生成するように構成され、シードにしたがって反復的に生成されたランダムシークェンスに基づいて各アクセス要請されたセグメントのデータをランダム化及びデランダム化するように構成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルから正確にデータを読み出すことのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施の形態に係る不揮発性半導体記憶装置は、複数のメモリセルを備えたメモリセルアレイと、選択メモリセルに読み出し電圧を印加するとともに、非選択メモリセルに読み出しパス電圧を印加して読み出し動作を実行する制御回路とを備える。制御回路は、選択メモリセルの制御ゲート電極とソースとの間の電圧を第1の値に設定して選択メモリセルの閾値電圧を読み出す第1の読み出し動作と、選択メモリセルの制御ゲート電極とソースとの間の電圧を第1の値より小さい第2の値に設定して選択メモリセルの閾値電圧を読み出す第2の読み出し動作とを実行可能に構成される。制御回路は、第2の読み出し動作を実行する場合、選択メモリセルの制御ゲート電極の電圧を0又は正の値に保ちながら制御ゲート電極とソースとの間の電圧を第2の値に設定する。

(もっと読む)

不良ビットエラーを処理するシステムおよび方法

【課題】半導体不揮発性メモリ装置における不良ビットエラーを補償する。

【解決手段】装置は、メモリ装置120から古いページを受け取り、そのページが不良ビットを有するか否かを決定する不良ビット検出モジュール116を含む。装置は、新しいページを生成する不良ビット修正モジュール118を含む。不良ビット修正モジュール118は、不良ビットの位置を特定し、不良ビットの好適値を決定し、不良ビットのユーザ値を決定する。不良ビット修正モジュール118は、古いページの実質的なデータに対応するビット列に好適値を挿入し、好適値が挿入されたビット列を記録する。不良ビット修正モジュール118は、古いページのアドレスに新しいページを格納する。

(もっと読む)

1 - 20 / 491

[ Back to top ]