Fターム[5C024HX23]の内容

光信号から電気信号への変換 (72,976) | 回路構成 (15,472) | A/D変換、D/A変換 (1,126)

Fターム[5C024HX23]の下位に属するFターム

リファレンス電圧調整 (46)

Fターム[5C024HX23]に分類される特許

101 - 120 / 1,080

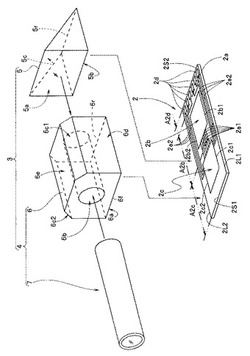

撮像装置

【課題】固体撮像素子の厚みをより薄く形成して内視鏡挿入部の細径化を図ることが可能で、取り扱いの容易な撮像装置を提供すること。

【解決手段】撮像装置1は、基板2aの一面を、被検体の光学像の撮像信号を生成する受光部2bを設けた受光部領域A2b、生成した撮像信号の信号処理及び受光部2bを駆動する駆動信号の生成を行う回路部2cを設けた回路部領域A2c、及び複数の電極パッド2dを設けた端子部領域A2dに区分した固体撮像素子2と、被検体の光学像を結像するための対物レンズ群7bを備えたユニット本体7およびユニット本体7が固設される保持枠6を備えて構成される対物レンズユニット4、及び対物レンズユニット4を通過した光学像を固体撮像素子2の受光部2bに導くプリズム5を有する対物光学部3と、備え、プリズム5を基板2aの受光部領域A2b上に配置し、保持枠6を回路部領域A2c上に配置している。

(もっと読む)

固体撮像装置、撮像装置、および信号読み出し方法

【課題】複数の基板を有する固体撮像装置の画素から複数の読み出し方式により信号を読み出すと共に、複数の読み出し方式のうち少なくとも1つの読み出し方式により1枚の基板のみを使用して信号を読み出す。

【解決手段】本発明の一態様に係る固体撮像装置は、複数の基板が接続部によって電気的に接続されている固体撮像装置であって、第1〜第n(nは2以上の整数)の読み出し方式のそれぞれに対応して信号の読み出しを可能にする回路要素を含む第1〜第nの回路セットを有し、複数の基板のうちの1枚の基板のみに配置された回路要素を使用して、光電変換素子による信号の発生から、第1〜第nの読出し方式のうち少なくとも1つの読み出し方式による信号の読み出しまでの動作が完了するよう、光電変換素子、読み出し回路、および少なくとも1つの読み出し方式に対応した回路セットが1枚の基板に配置されていることを特徴とする。

(もっと読む)

固体撮像装置及びカメラモジュール

【課題】高い色再現性と高感度とを実現可能とする固体撮像装置及びカメラモジュールを提供すること。

【解決手段】固体撮像装置11は、イメージセンサ22を有する。イメージセンサ22は、複数の画素セルを備える。複数の画素セルは、各色光を分担して検出する。複数の画素セルは、第1の緑色用画素セル及び第2の緑色用画素セルを含む。第1の緑色用画素セルは、第1の波長域の第1緑色光を検出する。第2の緑色用画素セルは、第2の波長域の第2緑色光を検出する。第2の波長域は、第1の波長域を含む。第1の緑色用画素セルが最大感度を示す波長と、第2の緑色用画素セルが最大感度を示す波長とは、略同じである。第2の緑色用画素セルの分光感度特性を表す関数の半値幅は、第1の緑色用画素セルの分光感度特性を表す関数の半値幅より大きい。

(もっと読む)

固体撮像装置およびカメラシステム

【課題】画素信号を加算して読み出す場合において、カラム処理の回数を減らすことが可能となり、その結果として、回路の低消費電力化や更なる高速撮像を実現することが可能な固体撮像装置およびカメラシステムを提供する。

【解決手段】画素配列の1列に対して複数の列信号線が配線され、複数の列信号線に画素の位置する行に応じて規則的に接続さている画素アレイ部と、画素アレイ部から複数の画素単位で画素信号の読み出しを行い、読み出し信号に対してカラム単位でカラム処理を行うカラム処理部を含む画素信号読み出し部とを有し、画素信号読み出し部は1つのカラム処理部の入力に対して、並列に接続された複数のキャパシタを介してカラムに対応する列に配線された1または複数の列信号線を接続可能なカラム入力部を含み、カラム入力部は複数のキャパシタとカラムに対応する複数の列信号線との接続状態を変更可能なスイッチを含む。

(もっと読む)

固体撮像装置、撮像装置及び画像生成方法

【課題】加算単位を重畳させて画素加算を行うことが可能な固体撮像装置、撮像装置及び画像生成方法等を提供すること。

【解決手段】撮像装置は、画素アレイ部と、行走査部4と、A/D変換部と、水平演算部8と、垂直演算部9を含む。加算対象となる画素の範囲である加算単位の列範囲を水平加算範囲とし、行範囲を垂直加算範囲とする。この場合に、水平演算部8は、行の画素値のうち水平加算範囲に含まれる画素値を、各列に重み付けして加算し、加算された画素値を水平加算画素値として出力する。垂直演算部9は、その水平加算画素値のうち垂直加算範囲に含まれる水平加算画素値を加算し、加算された水平加算画素値を加算画素値として出力する。水平演算部8は、第1の水平加算範囲と、第1の水平加算範囲と共通の画素を含む第2の水平加算範囲とを、水平加算範囲として水平加算画素値を出力する。

(もっと読む)

固体撮像装置およびカメラ

【課題】消費電力の低減に有利な技術を提供する。

【解決手段】画素アレイは、複数の列信号線を有し、各画素ユニットは、1つの光電変換素子と、前記光電変換素子で生じた電荷に応じた信号を前記列信号線に出力する増幅トランジスタとを有し、増幅トランジスタに電流を供給するカスコード電流源と、第1バイアス回路と、第2バイアス回路とを備え、前記増幅トランジスタと前記カスコード電流源とによってソースフォロア回路が構成され、前記第1バイアス回路は、前記カスコード電流源が動作状態、及び非動作状態であるときにおける第1トランジスタの電流駆動能力が同じになるように第1ノードの電圧を決定し、前記第2バイアス回路は、前記カスコード電流源が動作状態であるときの第2トランジスタの電流駆動能力よりも非動作状態であるときの前記第2トランジスタの電流駆動能力が小さくなるように第2ノードの電圧を決定する。

(もっと読む)

固体撮像装置

【課題】画素用電源としてアナログ電源を使用した場合においても、画素飽和信号量のばらつきの増大を抑制する。

【解決手段】画素アレイ部1は、光電変換した電荷を蓄積する画素2がマトリックス状に配置され、アナログ電圧安定化回路7は、アナログ電圧が所定値を超える場合、アナログ電圧を画素2の電源電圧として供給し、アナログ電圧が所定値以下の場合、アナログ電圧を昇圧してから画素2の電源電圧として供給する。

(もっと読む)

撮像装置、撮像方法

【課題】ローリングシャッタ歪みが小さい複数の被写体領域サイズの動画像を、不連続性を生じることなく低消費電力で得ることができる撮像装置等を提供する。

【解決手段】複数の画素が2次元状に配置された画素部21と、画素部21から読み出したアナログの画像データを一時的にアナログ記憶するフレームメモリ23と、を有する撮像素子3と、1回の露光により得られた全画素の画像データを画素部21から読み出してフレームメモリ23に記憶させる第1の読出制御を行うとともに、フレームメモリ23に記憶されている全画素の画像データから、全画素数よりも画素数が少ない画像データを、被写体領域サイズを異ならせるように、複数回に渡って非破壊読出する第2の読出制御を行う第1〜第3読出制御部22,24,25と、を備えた撮像装置。

(もっと読む)

撮像装置

【課題】シーンに適した高精度なフラッシュの発光制御を行えるようにする。

【解決手段】被写界を撮像する画像用の受光素子と、被写界からの光を測光する測光用の受光素子とを備える撮像素子と、画像用の受光素子の信号を用いて、被写界の中から特定の被写体を検出する検出部と、被写界を照明するフラッシュ装置と、特定の被写体に対応する測光用の受光素子の出力信号の積分値が予め定められた値に達した場合にフラッシュ装置の発光を停止するように制御する制御部とを備える。

(もっと読む)

固体撮像素子およびその駆動方法、カメラシステム

【課題】レート変換のためにバッファが不要で、低回路規模化、低消費電力化を図ることが可能な固体撮像素子およびその駆動方法、カメラシステムを提供する。

【解決手段】レート変換情報に応じて、カラム処理部で処理されたデータのレート変換制御を行うレート変換制御部を有し、レート変換制御部は、第2の周波数の第2のクロックである基準クロックを基に、第1のクロックを生成してカラム処理部に供給する第1のレート変換器と、第2の周波数の第2のクロックである基準クロックを基に、データレートに応じて変化する第3の周波数の第3のクロックを生成する第2のレート変換器と、カラム処理部で処理されたデータのレートを加算処理を含んだ処理により変換し、変換後または変換前のデータを第2のデータとして出力するデータレート変換部と、第3のクロックに同期してデータレート変換部による第2のデータを出力するデータ出力部と、を含む。

(もっと読む)

固体撮像装置、撮像システム

【課題】高フレームレートの映像出力に適した固体撮像装置を提供する。

【解決手段】マトリクス状に配列された複数の光電変換部と、列ごとに設けられ、各光電変換部で生成された信号電荷を電荷パケットとして転送する複数の垂直転送器とを含む撮像部101と、撮像部101から複数の電荷パケットを受け取って転送する水平転送器106と、水平転送器106における所定個数の転送段ごとに1つの転送段は分岐転送段106Aであり、各分岐転送段106Aに、隣接する転送段106Bとは異なる方向に隣接して設けられ、分岐転送段106Aから電荷パケットを取得して保持する複数の取り出し部107と、各取り出し部107に隣接して設けられ、取り出し部107から電荷パケットを取得し、電圧信号に変換して出力する複数の出力回路108と、を備える。

(もっと読む)

撮像方法および撮像装置

【課題】奥行計測用に発光させた光の反射光から被写体を撮像する場合、簡単な回路構成で外光や雑音の影響をなくし計測精度を向上させること。

【解決手段】1フレーム期間内に、2つの露光期間A,Bと、一方の露光期間Bに一致する1つの発光期間と、3つの出力期間C,A,Bを設ける。出力期間Cでは、映像信号を含まないランダム雑音を出力し、出力期間Aでは、露光期間Aの映像信号とランダム雑音とを出力し、出力期間Bでは、露光期間Aの映像信号と露光期間Bの映像信号とランダム雑音とを出力する。出力された3つの期間の信号を演算して、外光による映像信号とランダム雑音を除去して発光のみによる映像信号を取得する。

(もっと読む)

部品実装装置における画像読取装置および画像読取方法

【課題】画像信号へのノイズの混入を生じることなく画像信号の出力を効率化して、部品の画像読取りの高速化を実現することができる部品実装装置における画像読取装置および画像読取方法を提供する。

【解決手段】ラインセンサから出力された画像信号をAD変換処理後に画像形成部に出力するに際し、AD変換処理後の画像信号30a1についてAD変換処理に伴って生じる応答遅れに相当する画像信号30a*を、直後にAD変換処理される後続の画像信号30a2に時系列を合致させて結合して画像形成部に対して出力する画像調整処理を実行する。これにより、ラインセンサにおいて電荷の転送を行っている間にもAD変換処理部を継続して駆動させることが可能となり、AD変換処理の中断に起因する画像信号へのノイズの混入を防止しながら画像信号の出力を効率化して部品の画像読取りの高速化を実現することができる。

(もっと読む)

A/D変換装置、A/D変換方法および固体撮像装置

【課題】出力分解能を犠牲にすることなく、消費電力を低減することができるA/D変換装置、A/D変換方法および固体撮像装置を提供する。

【解決手段】

アナログ入力信号に応じてパルス信号を遅延させるn(n:正の整数、n≧2)個の遅延素子が円環状に接続され、第1の時刻から第2の時刻までパルス信号を伝播させるパルス遅延回路と、第1の時刻から第2の時刻よりも短い第3の時刻までの周回数をカウントするカウンタ回路と、第3の時刻までの周回数を上位ビットラッチ値として出力する上位ビットラッチ回路と、第3の時刻の位置を第1の下位ビットラッチ値として出力し、第2の時刻の位置を第2の下位ビットラッチ値として出力する下位ビットラッチ回路と、第1の時刻から第2の時刻までの周回数の上位ビット推定値と第2の下位ビットラッチ値とに基づいて、アナログ入力信号の大きさに応じたデジタル出力値を生成するデジタル演算回路と、を備える。

(もっと読む)

センサ装置並びにこれを用いた焦点検出装置、AE用検出装置及びカメラ

【課題】光電変換素子アレイ部の複数の光電変換素子の増幅後の出力信号が適正レベルであるか否かの判定に関する処理量を、ピーク値を利用する場合の処理量に比べて抑える。

【解決手段】センサ装置は、複数の光電変換素子31aを有する光電変換素子アレイ部31Aと、今回の電荷蓄積動作による前記複数の光電変換素子31aの出力を増幅する増幅器33Aと、カウンタ38と、判定部51とを備える。カウンタ38は、1つ以上の基準レベルのそれぞれに関して、前記複数の光電変換素子31aのうちの2つ以上の光電変換素子31aのうち、増幅器33Aにより増幅された出力が当該基準レベル以上であるか又は当該基準レベル以下である光電変換素子の数をカウントする。判定部51は、カウンタによりカウントされたカウント値に基づいて、増幅器33Bにより増幅された出力が適正レベルであるか否かを判定する。

(もっと読む)

固体撮像素子

【課題】画素トランジスタにおける欠陥の異常成長を抑制する固体撮像素子を提供する。

【解決手段】半導体基板101のPウェル102の内部に形成され、入射光を光電変換する受光領域103と、Pウェル102の内部に形成されたウェル領域104と、Pウェル102の内部において、ウェル領域104に隣接して形成された素子分離領域105と、素子分離領域105の上に形成されたダミー素子109とを備える。

(もっと読む)

撮像装置

【課題】A/D変換回路によるアナログ・デジタル変換動作に伴う消費電力を低減し、かつ、高い精度の変換結果を得ることができる撮像装置を提供する。

【解決手段】画素が行列状に複数配置された画素部と、対応する列の画素信号の大きさに応じた遅延時間でパルス信号を走行させる遅延素子が円環状に複数段連結された複数のパルス走行回路と、対応する1つの遅延素子からの遅延出力信号が入力され、入力信号を反転した第1の反転信号を出力する第1の反転回路と、第1の反転信号を反転した第2の反転信号を出力する第2の反転回路とを具備した複数のラッチ回路と、ラッチ回路による反転動作を制御するラッチ制御回路と、を備え、パルス走行期間に遅延出力信号の反転動作を禁止し、パルス走行期間が終了する前の予め定めたラッチタイミングのときに遅延出力信号の反転動作を許可し、ラッチ期間に第1の反転回路に第2の反転信号の反転動作を行わせる。

(もっと読む)

固体撮像装置用信号処理装置

【課題】面積の増加を抑制しつつ、フレームレートを向上できる固体撮像装置用信号処理装置を提供する。

【解決手段】本発明に係るアナログフロントエンド200は、CCD部100により出力されるアナログ信号を処理するアナログフロントエンド200であって、前記アナログ信号を増幅するアンプ201と、時系列に入力される、アンプ201により増幅されたn個のアナログ信号を保持するためのn個の容量203を含むマルチホールド回路210と、n個の容量203に保持されているn個のアナログ信号をn個のデジタル信号に変換するAD変換回路211とを備える。

(もっと読む)

イメージセンサ及びその駆動方法

【課題】入射フォトンのカウントを低消費電力で行う。

【解決手段】イメージセンサは、複数の画素を有する。前記複数の画素は、それぞれ、光電変換を行う光電変換部と、参照電圧保持容量と、前記光電変換部の出力電圧と前記参照電圧保持容量の電圧とが2つの入力ノードにそれぞれ入力され、前記2つの入力ノード間の電圧差を増幅して出力する差動増幅器と、前記光電変換部の出力電圧を所定の電圧にリセットするリセット回路と、前記差動増幅器の前記2つの入力ノード間に設けられ、導通することにより、前記参照電圧保持容量の電圧を前記光電変換部の出力電圧にするスイッチとを有する。

(もっと読む)

固体撮像装置

【課題】オーバーレンジのアナログデジタル変換において、隣接する2つのサブレンジの境界付近における入出力特性の不連続性を低減することができる固体撮像装置を提供する。

【解決手段】カウンタ782は、第2の変換ステージにおいて、クロックに応じてインクリメントされる。ランプ電圧発生部618は、カウンタ782の値に応じた大きさのランプ電圧を出力する。第2の変換ステージにおいて、カウンタ782の初期値がSであり、カウンタの取りうる値はサブレンジに対応してM個で、隣接するそれぞれのオーバーラップ領域に対応してL個である。シーケンサは、第1の電圧と第2の電圧の差が、カウンタ782の値が(S+L)のときのランプ電圧の値である第1ランプ電圧とカウンタ782の値が(S+L+M−1)のときのランプ電圧の値である第2ランプ電圧との差に等しくなるように調整部613に調整させる。

(もっと読む)

101 - 120 / 1,080

[ Back to top ]