Fターム[5C024HX23]の内容

光信号から電気信号への変換 (72,976) | 回路構成 (15,472) | A/D変換、D/A変換 (1,126)

Fターム[5C024HX23]の下位に属するFターム

リファレンス電圧調整 (46)

Fターム[5C024HX23]に分類される特許

161 - 180 / 1,080

固体撮像装置

【課題】固体撮像装置を大型化させることなく、A/D変換回路の動作に起因する入力およびGNDの電圧レベルの変動を低減し、出力するデジタル値の変動(誤差)を低減することができる固体撮像装置を提供する。

【解決手段】光電変換素子のリセット信号と画素信号とを出力する画素が二次元の行列状に複数配置された画素部と、所定の1つの画素からのリセット信号および画素信号が順次入力される第1の容量と、画素信号とリセット信号との差を保持する第2の容量とを具備し、差分信号を出力するアナログ信号処理部と、差分信号の大きさに応じた遅延時間でパルス信号を遅延させる遅延素子がリング状に複数段接続された遅延回路と、パルス信号の遅延回路内の伝播を検出した結果に基づいたデジタル信号を生成するアナログ・デジタル変換器と、アナログ信号処理期間とサンプリング期間とで第1の容量の接続を切り替える切り替え回路と、を備える。

(もっと読む)

タイル構成可能なパッケージング構造によるマルチ・スライスCT検出器

【課題】検出器性能を高めつつスライスを増加させた取得を提供する。

【解決手段】各々の検出器モジュール(20)が、モジュール・フレーム(52)と、モジュール・フレーム(52)のZ軸に沿って整列してモジュール・フレーム(52)に設けられ、物体によって減弱したX線を受光してディジタル信号へ変換する複数のタイル構成可能なサブ・モジュール(56)と、複数のサブ・モジュール(56)に接続されてディジタル信号を受け取る電子回路基板(32)とを含んでいる。各々のサブ・モジュール(56)がさらに、検出器素子のアレイ(60)と、検出器素子のアレイ(60)からのアナログ電気信号をディジタル信号へ変換するASIC電子回路パッケージ(68)と、ASIC電子回路パッケージ(68)に接続されて、ディジタル信号を受け取って電子回路基板(32)へ転送するフレックス回路(76)とを含んでいる。

(もっと読む)

固体撮像装置

【課題】高精度にA/D変換を行い、固体撮像装置の規模の増加を最小限に抑える。

【解決手段】パルス遅延部101は、パルスを伝達する複数の遅延素子を含む。下位ビットラッチ部103は、停止信号を遅延させた遅延停止信号が入力されたときに複数の遅延素子の出力信号をラッチする。カウンタ部102は、複数の遅延素子の1つの出力信号に基づいてパルスの周回数をカウントする。第1の上位ビットラッチ部105は、停止信号が入力されたときにカウンタ部102の出力信号の少なくとも最下位ビットをラッチする。第2の上位ビットラッチ部104は、遅延停止信号が入力されたときにカウンタ部102の出力信号をラッチする。補正部013は、第1の上位ビットラッチ部105と第2の上位ビットラッチ部104の出力信号を比較した結果および下位ビットラッチ部103の出力信号に基づいて、カウンタ部102によるカウントの結果を補正する。

(もっと読む)

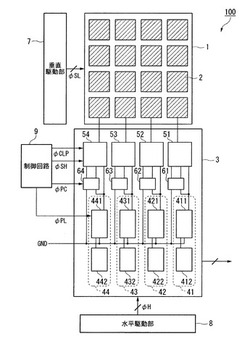

固体撮像装置

【課題】ダミー画素領域の増大を抑えつつ、非直線性ばらつきを除去するための補正式を算出することができる固体撮像装置を提供する。

【解決手段】画素アレイ3において、有効画素1は、少なくとも、入射光量に基づく画素信号を出力し、ダミー画素2は、与えられた基準電圧の電圧値に基づく画素信号を出力する。制御回路8は、ダミー画素2に、少なくとも、第1の基準電圧を与えてiフレーム分のダミー画素2の画素信号を読み出し、第2の基準電圧を与えてjフレーム分のダミー画素2の画素信号を読み出す制御を行う。補正式算出回路9は、少なくとも、第1の基準電圧が与えられたときに読み出されたiフレーム分のダミー画素2の画素信号をアナログ・デジタル変換した値と、第2の基準電圧が与えられたときに読み出されたjフレーム分のダミー画素2の画素信号をアナログ・デジタル変換した値とから、A/D変換器6の非直線性を補正する補正式を算出する。

(もっと読む)

固体撮像装置

【課題】回路規模を増大させることなく、かつ、ダイナミックレンジを低下させることなく横筋状ノイズ補正を可能とする固体撮像装置を提供する。

【解決手段】所定の時間間隔で、複数のAD変換部により変換された単位画素のデジタル信号から光学的な黒レベルを示すクランプ値を演算するクランプ演算回路190と、前記クランプ値に基づき、列AD変換部120に、対応する列の単位画素のデジタル信号であってオフセット信号成分を除くデジタル信号に変換させる制御部とを備え、クランプ演算回路190は、前記クランプ値と、1つ前に演算した過去クランプ値との差が予め定められた下限値以下の場合には、所定の時間間隔を長くして前記クランプ値の次のクランプ値を演算し、前記クランプ値と過去クランプ値との差が予め定められた上限値以上の場合には、所定の時間間隔を短くして前記クランプ値の次のクランプ値を演算する。

(もっと読む)

撮像装置

【課題】温度によって暗電流の発生量が異なる場合に画像処理に必要なダイナミックレンジを維持できる撮像装置を提供する。

【解決手段】複数の画素が配列された撮像部と、前記撮像部から読み出される信号に第1ゲインを乗算する第1ゲイン乗算部と、前記撮像部から読み出される信号から暗電流成分を減算する暗電流補正部と、前記暗電流補正部が減算後の信号に第2ゲインを乗算する第2ゲイン乗算部と、前記撮像部近傍の温度を計測する温度計測部と、前記温度計測部が計測した温度に応じて、前記第1ゲインと前記第2ゲインとのトータルゲインが一定になるように、前記第1ゲインと前記第2ゲインの割合を可変して前記第1ゲイン乗算部と前記第2ゲイン乗算部とに設定するゲイン制御部とを備える。

(もっと読む)

熱型光検出器、熱型光検出装置、電子機器および熱型光検出器の製造方法

【課題】 熱型光検出器の検出感度を向上させること。

【解決手段】 熱型光検出器は、基板10と、基板に対して空洞部102を介して支持される支持部材215と、支持部材に支持される熱検出素子230と、熱検出素子と接続部CNによって接続され、平面視で接続部よりも広い面積を有し、かつ熱検出素子230上に形成されている集熱部FLを備える熱伝達部材260と、熱伝達部材260と熱検出素子230との間において、熱伝達部材260に接して形成されている、第1光吸収層270と、熱伝達部材260上において、熱伝達部材260と接して形成されている第2光吸収層272と、を有する。

(もっと読む)

放射線画像撮影装置、放射線画像撮影プログラム、及び放射線画像撮影方法

【課題】装置が大型化するのを抑制しつつ、照射された放射線量に応じて精度良く、増幅率の設定ができる、放射線画像撮影装置、放射線画像撮影プログラム、及び放射線画像撮影方法を提供する。

【解決手段】放射線が照射されると、当該放射線に応じて発生した電荷の電荷蓄積期間に放射線検出用の画素20Bから出力された電気信号に基づいて、制御部106が信号検出回路105の増幅回路50の増幅率を決定し、決定した増幅率を増幅回路50に対して設定することにより、増幅回路50の増幅率を制御する。放射線検出素子10の信号検出回路105では、当該電荷蓄積期間に蓄積された電荷に応じた電気信号が、設定された増幅率により増幅回路50で増幅され、ADC54によりデジタル信号に変換されて制御部106へ出力される。

(もっと読む)

画像信号処理装置および固体撮像装置

【課題】OB画素から読み出された黒レベルが一定になるように黒レベルを補正する。

【解決手段】フィードバッククランプ回路102は、CMOSセンサ101のOB画素から読み出された黒レベルが目標値に近づくようにクランプパラメータPCを増減させる。この時、フィードバッククランプ回路102は、CMOSセンサ101のOB画素から読み出された黒レベルに基づいてクランプパラメータPCの変化量を制御する。

(もっと読む)

固体撮像装置

【課題】リニアログ特性の固体撮像装置において、ダイナミックレンジを拡大する。

【解決手段】TG6は、判定部14により高輝度状態にあると判定された場合、電流源ISが生成する電流を低輝度露光状態の場合に比べて増大させ、コンデンサCINのセトリング期間を短くする。これにより、カラムADC31がノイズ信号をサンプルホールドするためのサンプルホールド期間が短縮され、読出期間において、PDから溢れてFDに流れる信号電荷量が少なくなる。これにより、ノイズ信号のレベルの低下が抑制され、白黒反転現象が抑制され、ダイナミックレンジが拡大する。

(もっと読む)

撮像素子および撮像装置

【課題】画素情報量の低減を回避しつつ飽和信号量の向上を図る。

【解決手段】CMOSセンサ23は、斜め画素配列により複数の画素が配置された画素アレイ31と、画素アレイ31の偶数列の画素から出力される画素信号をデジタル変換する列並列AD変換回路35−1と、画素アレイ31の奇数列の画素から出力される画素信号をデジタル変換する列並列AD変換回路35−1と、列並列AD変換回路35−1および列並列AD変換回路35−2から出力される画素データを加算するロジック回路32とを備える。そして、列並列AD変換回路35−1および列並列AD変換回路35−2は、フリップフロップ、第1のラッチ回路、および第2のラッチ回路を含むカウンタを有する。本発明は、例えば、斜め画素配列で画素が配置された撮像素子に適用できる。

(もっと読む)

パルス走行位置検出回路、A/D変換回路および固体撮像素子

【課題】高精度でパルス信号の走行位置を検出することができ、狭小な場所にも配置することができるパルス走行位置検出回路、これを用いたA/D変換回路、およびこのA/D変換回路を用いた固体撮像素子を提供する。

【解決手段】印加された電源または該電源に応じた電流源に応じた遅延時間でパルス信号を遅延させる複数の遅延素子を具備した同一の構成の遅延回路が、少なくとも1つのフィードフォワード回路が形成されるように、直列の円環状に複数段連結されたパルス走行回路と、複数の遅延回路のそれぞれから出力される出力信号を検出して保持した情報を走行位置の情報として出力するラッチ回路とを備え、それぞれの遅延回路は、第1の遅延素子と、構造が異なる第2の遅延素子とを具備し、少なくとも1つの遅延回路内にパルス信号の走行を開始させる起動信号を入力し、他の遅延回路内に、少なくともパルス信号が走行している間は所定の固定電圧を入力する。

(もっと読む)

撮像装置

【課題】カラム部内で2進化および減算を行うことが可能となり、信号の位相合わせを簡略化することができる撮像装置を提供する。

【解決手段】ラッチ部107は、VCO101から出力される第1の下位位相信号および第2の下位位相信号をラッチする。下位計数部21は、ラッチ部107に保持された第1の下位位相信号、第2の下位位相信号に応じて第1の下位計数信号、第2の下位計数信号を生成し、各下位計数信号に基づく計数値の差に応じて、フラグ信号を含む下位差分信号を生成して出力する。上位計数部22は、VCO101から所定の周期で第1の画素信号に応じて出力される第1の上位計数信号に基づく計数値と、VCO101から所定の周期で第2の画素信号に応じて出力される第2の上位計数信号に基づく計数値との差に応じて、上位差分信号を生成し、フラグ信号に基づいて上位差分信号から所定の数を減算処理し、減算処理後の上位差分信号を出力する。

(もっと読む)

放射線撮影装置

【課題】放射線検出パネルの外周部に設けられた機能素子に対する電源部からのノイズの影響を抑制する。

【解決手段】放射線を検出する放射線検出パネルと、前記放射線検出パネルの外周部の4辺のうち3辺に設けられ、所定の機能を有し、少なくとも1つがA/D変換器である機能素子と、前記放射線検出パネルの裏面に配置され、かつ、平面視における前記放射線検出パネルの中心部に配置され、前記放射線検出パネルを含む構成部の少なくとも一部へ電力を供給する電源部と、を備えている。

(もっと読む)

オフセット除去回路、サンプリング回路及びイメージセンサ

【課題】オフセット除去回路、サンプリング回路及びイメージセンサを提供する。

【解決手段】イメージセンサは基準電圧を受信し、リセット電圧と前記基準電圧の電圧差である複数の第1電圧を保存する複数のデカプリングキャパシタを含み、複数のデータ電圧及び前記複数の第1電圧に基づいて複数の第2電圧を各々生成する複数のオフセット除去回路と、前記複数の第2電圧を複数のデジタル出力信号に変換するアナログ−デジタル変換部とを含む。オフセット除去回路は、デカプリングキャパシタが単位セルから受信されたリセット電圧と基準電圧との電圧差に相応する電荷を保存することによって単位セルのオフセットを除去する。

(もっと読む)

光電変換装置

【課題】光電変換装置を大型化させることなく、カラムA/D方式の光電変換装置と同等のデジタル値を出力することができる光電変換装置を提供する。

【解決手段】光電変換素子を有し、該光電変換素子への入射光量に応じた画素信号を出力する画素が、二次元のY行X列に複数配置された画素アレイと、画素アレイの列毎に読み出された画素信号の電圧の大きさに応じて周回するパルス信号を計測し、該計測したパルス信号の情報を出力するm(m≦X)個のパルス計測部と、パルス計測回路が計測したパルス信号の情報に基づいて、画素アレイの各列から読み出された画素信号に応じたデジタル値を出力するk(k<m)個のエンコーダ部と、m個のパルス計測部から出力されるパルス信号の情報を順次切り替えて、k個のエンコーダ部に入力させる切り替え部と、を備える。

(もっと読む)

放射線画像検出装置

【課題】放射線画像の信号からノイズ成分を確実に除去する。

【解決手段】FPD36には、画素37の複数列のグループ62毎に、画素37で蓄積された信号電荷を電気信号に変換して出力する信号処理回路40とノイズ検出素子63が配されている。ノイズ検出素子63は、画素37と同様の構成であるが電荷蓄積機能を有さず、その出力電圧信号Dnzはノイズ成分を表す。減算器64は、信号処理回路40から出力された画素37の電圧信号Diからノイズ検出素子63の電圧信号Dnzを減算する。

(もっと読む)

センサ装置

【課題】高精度化および動作速度の高速化を図ることが可能なセンサ装置を提供する。

【解決手段】センサ部1とチョッパアンプ3の一方の入力端子との間を接続する第1状態とチョッパアンプ3の一方の入力端子と他方の入力端子との間を短絡する第2状態とを切り替える第1の切替部2を備えている。制御回路(制御手段)9は、2つの積分器6,6の一方の積分器6の第2積分期間T2と他方の積分器6の第1積分期間T1とが重なるように第3の切替部5,5を制御する。ディジタル回路12は、制御回路9からの読み出しタイミング信号が入力される度に、ディジタル値を出力するように構成されている。ディジタル回路12は、第1状態のときに第1積分期間T1が設定された積分器6の第2積分期間T2に対応したカウント値と第2状態のときに第1積分期間T1が設定された積分器6の第2積分期間T2に対応したカウント値との差分値をディジタル値として出力する。

(もっと読む)

固体撮像装置

【課題】イメージセンサの画質の向上を図る。

【解決手段】実施形態の固体撮像装置は、複数の画素からの基準電圧と信号電圧とに対して信号処理を施して、前記基準電圧と前記信号電圧との差分値のデジタル値を出力するAD変換回路と、所定のパルス波形Vrp1,Vrp2の参照電圧VREFをAD変換回路に出力する参照電圧生成回路と、を具備する。参照電圧生成回路は、参照電圧VREFと基準電圧VRSTとを比較する第1の信号処理において、電流源回路から第1の電流を供給し、パルス波形Vrp1を生成し、第1の信号処理の後に、積分回路に電流源回路からの第2の電流を供給し、参照電圧VREFの電圧値を初期電圧にリセットし、参照電圧VREFと信号電圧VSIGとを比較する第2の信号処理において、パルス波形Vrp3を出力する。

(もっと読む)

固体撮像装置

【課題】画質の低下を抑制しつつ、動画に対してフリッカを抑圧することが可能な固体撮像装置を提供する。

【解決手段】信号処理回路14は、画素部Gの信号から測定された光量測定値AEに基づいて、偶数ラインの蓄積時間Tint1および奇数ラインの蓄積時間Tint2をフレームごとに制御させ、フリッカ補正回路11は、蓄積時間が互いに異なるラインごとの画素の信号OUTPに基づいて、画素部Gにて撮像された信号OUTPに発生するフリッカをラインごとに補正する。

(もっと読む)

161 - 180 / 1,080

[ Back to top ]