Fターム[5C094EB05]の内容

要素組合せによる可変情報用表示装置 (81,180) | 基板 (1,167) | 材質 (793) | 半導体基板 (36)

Fターム[5C094EB05]に分類される特許

1 - 20 / 36

発光装置

【課題】表示むらを抑制すること、又は異なる画素におけるトランジスタ特性のばらつきを低減すること、あるいは、発光素子の劣化等に伴う輝度の低下を抑制する事が可能な発光装置を提供する。

【解決手段】基板100の上に設けられたトランジスタ121と、発光素子109とを具備する画素部120を有し、トランジスタは、チャネル形成領域を形成する単結晶半導体層122を有し、基板と単結晶半導体層との間に、酸化シリコン層が設けられており、トランジスタのソース又はドレインと発光素子の電極とが電気的に接続され、発光素子の発光時にトランジスタを飽和領域で動作させる。また、発光素子の階調表示を、トランジスタのゲートに印加する電位を変化させることによって行う。

(もっと読む)

電気光学装置、電気光学装置の駆動方法および電子機器

【課題】シリコン基板にOLEDのような発光素子を含む画素回路を形成する。

【解決手段】画素回路が配列する表示部100と、表示部100から離間して囲むように設けられ、複数の画素回路を駆動する走査線駆動回路140、データ線駆動回路150とがシリコン基板に形成される。Nウェル104は、表示部100にわたって連続的に形成される。複数の画素回路の各々は、それぞれ複数のトランジスターを有し、当該トランジスターはNウェル104に共通に形成されるとともに、基板電位を共通である。表示部100におけるNウェル104は導電型の異なるP型半導体基板領域102で囲まれる。

(もっと読む)

アクティブマトリクス基板、電気光学装置及び電子機器

【課題】レイアウトの自由度を高め、基板上の熱源による表示品質の低下を防止できるアクティブマトリクス基板を提供する。

【解決手段】走査線22、データ線24及び画素26を含む画素回路と、半導体基板の一辺に沿って形成された複数のパッドを含む入力パッド部30と、高速シリアルインターフェース回路40と、高速シリアルインターフェース回路からの出力に基づいて階調データを生成するロジック回路50と、階調データに基づいて複数のデータ線を駆動するデータ線駆動回路60と、制御信号に基づいて走査線を駆動する走査線駆動回路70とを有し、半導体基板の一辺と画素回路との間で、該一辺側から順に、入力パッド部、高速シリアルインターフェース回路及びロジック回路が配置され、ロジック回路と画素回路との間に、データ線駆動回路及び走査線駆動回路の一方が配置される。

(もっと読む)

液晶表示装置

【課題】各画素内の正極性信号側画素回路部と負極性信号側画素回路部で互いに対になっている回路構成要素及び配線同士を、仮想の画素中心線に対して線対称で配置構成することにより、画素ピッチを増大させることなく液晶素子に正常な駆動電圧を印加する。

【解決手段】Vdd配線102、Cs1接続配線104、データ線Di+用配線106などの正極性信号側画素回路部の配線と、Vdd配線103、Cs2接続配線105、データ線Di-用配線107などの負極性信号側画素回路部の配線とは、画素中心線II−II’に対して対応する配線同士が線対称位置に配置されている。Vdd配線102とVdd配線103とは、1画素内の左右両端に配置されているため、左右両隣の画素のCs1接続配線、又はCs2接続配線からのクロストークを抑制するガードパターンの役割を果たしている。データ線Di+用配線106及びデータ線Di-用配線107は、画素の中心部付近に配置されている。

(もっと読む)

半導体装置

【課題】電極による可視光の反射率を向上させること。

【解決手段】半導体基板10の上方に設けられ、液晶層32を透過した光を反射する電極24と、前記電極上に形成された酸化シリコン膜26と、前記酸化シリコン膜上に形成された窒化シリコン膜28と、を具備し、前記酸化シリコン膜の膜厚をd1、前記窒化シリコン膜の膜厚をd2としたとき、d1が70nm以上80nm以下であり、かつd2が60nm以上70nm以下である半導体装置。

(もっと読む)

電界効果型トランジスタ、半導体メモリ、表示素子、画像表示装置及びシステム

【課題】比誘電率が高くリーク電流の少ない絶縁膜を提供する。

【解決手段】基板と、前記基板上に形成されたソース電極、ドレイン電極、及びゲート電極と、前記ゲート電極に所定の電圧を印加することによりソース電極とドレイン電極との間にチャネルが形成される半導体層を有し、前記ゲート電極と前記半導体層の間にゲート絶縁層と、を備え、前記ゲート絶縁層は、アルカリ土類金属の中から選ばれた1または2種類以上の元素と、Ga、Sc、Y、及びCeを除くランタノイドの中から選ばれた1または2種類以上の元素とを含むアモルファス複合金属酸化物絶縁膜により形成されていることを特徴とする電界効果型トランジスタを提供することにより上記課題を解決する。

(もっと読む)

表示モジュール及び表示装置

【課題】本発明は、エレメントの数量を減らして、電気エネルギーの消費を低く抑える表示モジュール及び表示装置を提供することを課題とする。

【解決手段】本発明の表示モジュール2は、第一基板21、第二基板22、駆動ユニット23、複数のデータライン及び複数のスキャンラインを備える。第一基板21は第一画素電極アレイ211を、第二基板22は第二画素電極アレイ221を有する。データラインは、それぞれ駆動ユニット23及び第一画素電極アレイ211に電気的に接続され、さらに、少なくとも一部のデータラインは、第一基板21を介して第二画素電極アレイ221に電気的に接続される。スキャンラインは、それぞれ駆動ユニット23及び第一画素電極アレイ211に電気的に接続され、且つ、第二画素電極アレイ221には電気的に接続されない。

(もっと読む)

アクティブマトリクス基板、アクティブマトリクス基板の製造方法、電子機器および電子機器の製造方法

【課題】製造が容易で高精細化が可能なアクティブマトリクス基板を提供する。

【解決手段】本発明のアクティブマトリクス基板は、第1電極(5d)と接続された第1画素電極(PE)と、第2電極(5d)と接続され、第1画素電極の隣に配置された第2画素電極(PE)と、平面視において第1電極と第2電極との間に設けられた第1共通電極(5s)と、第1共通電極に接続されたデータ線(DL)と、第1電極、第2電極および第1共通電極の形成領域に一体に形成された第1半導体膜(7)と、を有し、第1画素電極と電気的に接続される第1トランジスタ(T(00))は、第1電極と第1共通電極との間を第1チャネル領域とし、第2画素電極と電気的に接続される第2トランジスタ(T(01))は、第2電極と第1共通電極との間を第2チャネル領域とする。このように、1つの半導体膜を2つの画素に係る2つのトランジスタによって共有することで、構成を簡素化でき、画素の縮小化、画素ピッチの短縮化にも対応できる。

(もっと読む)

電気光学装置および電子機器

【課題】素子基板の基板本体として半導体基板を用いた場合でも、複雑なウエル構造や大掛かりな遮光構造を必要とせず、かつ、基板本体としてガラス基板などを用いた場合に比較して画素トランジスターの特性を大幅に向上することのできる電気光学装置、および当該電気光学装置を備えた電子機器を提供すること。

【解決手段】電気光学装置100の素子基板10では、基板本体として、単結晶シリコン基板からなる半導体基板11を用い、半導体基板11の表面に不純物を導入することによって、バックゲート構造を備えた画素トランジスター30の第1ゲート電極11a、および保持容量60の第1保持容量電極11bを同時形成する。また、第1ゲート絶縁層70の一部を保持容量用誘電体層70cとして利用する。

(もっと読む)

薄膜半導体基板およびその製造装置

【課題】フラットパネルディスプレイの大量生産を可能とし、かつ保管、運搬が容易で安価である。

【解決手段】プラスチック基板と対向して組み合わせてフラットパネルディスプレイとするための薄膜半導体アレイ3を有する単板状の絶縁基板4が長尺状のプラスチックフィルム2上に連続して貼合されてなる。また、フラットパネルディスプレイとする薄膜半導体基板を製造する装置であって、薄膜半導体アレイ3を保護するための保護フィルムが貼合された単板状の絶縁基板4を長尺状のプラスチックフィルム2上に連続して貼合する貼合部と、保護フィルムを加熱または紫外線照射により剥がす剥離部と、長尺状の保護フィルム6を長尺状のプラスチックフィルム2にラミネートして薄膜半導体アレイ3を保護するラミネート部と、長尺状の保護フィルム6をラミネートした長尺状のプラスチックフィルム2をロール状に巻き取る巻取り部とを有する。

(もっと読む)

表示装置

【課題】フラットな液晶表示パネルを湾曲することによって形成される円筒型液晶表示装置において、液晶表示パネルの端部の突き合わせ部における段差をなくする。

【解決手段】研磨によって薄くした液晶表示パネルを湾曲させて円筒型の表示装置を形成する。液晶表示パネルの端部どうしが突き合わされる部分には線Lが形成される。線Lにおける段差を小さくするために、カラーフィルタ基板20の端部E2における板厚TC2を、液晶表示パネルの他の端部E1におけるTFT基板10の板厚TT1およびカラーフィルタ基板20の板厚TC1の合計よりも大きくする。

(もっと読む)

保護板で被覆された電子表示装置の製造法

【課題】従来の欠点を改善した、電子表示装置の製造法を提供すること。

【解決手段】本発明は、保護板で被覆されたスクリーン(3)を有する電子表示装置(1)の製造法および、その装置を得るための前記スクリーンによって覆われた基板(2)に関する。この製造法は:a)実質的に架橋していない状態の接着剤(10)を、スクリーンの電気接続域(5)に接続域を接着剤から保護するための少なくとも1層の有機層(15)を形成したのちに、スクリーンの表面全体および/または保護板(11)の接合面(11a)全体に塗布する工程;接着剤を介してスクリーンに接合面を合わせる工程;c)保護板を通して放射線を照射して接着剤を架橋させる工程;およびd)接続域を覆っている部分の保護板を取り除き、それと同時もしくは、その後の表面処理によって、保護層を接続域から取り除いて、接続域を電気接触できるようにする工程、からなっている。本発明における保護層はジアミン類から誘導される化合物およびヘテロ環を有する有機金属錯体からなる群から選ばれる少なくとも1つの有機化合物を含有している。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】必要とされる機能に応じてトランジスタの電気特性を制御し、半導体装置の高性能化、低消費電力化を図ることを目的の一とする。また、そのような半導体装置を、作製工程を複雑化することなく、高い歩留まりで生産性よく作製することを目的の一とする。

【解決手段】半導体装置に含まれるトランジスタのしきい値電圧を制御するための一導電型を付与する不純物元素の添加を、半導体基板よりトランジスタの半導体層を分離し、絶縁表面を有する基板である支持基板上に転載する前に、半導体基板へ行う。

(もっと読む)

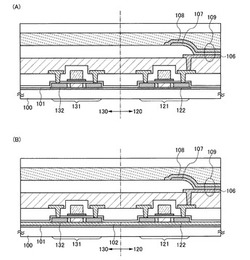

表示装置

【課題】表示装置の画素を構成する電界効果トランジスタの高性能化を実現し、且つ電界効果トランジスタの微細加工技術に依拠することなく、画素内の電界効果トランジスタ数を増やしても電界効果トランジスタ数の増加に伴い低下した画素の開口率を向上及び画素に占める電界効果トランジスタの面積の削減を図ることのできる表示装置を提供することを目的の一とする。

【解決手段】半導体基板より分離され、絶縁表面を有する支持基板に接合された半導体層を有する電界効果トランジスタが、平坦化層を層間に設けて複数積層された画素を複数具備する表示装置とする。

(もっと読む)

半導体装置、表示装置及びそれらの製造方法

【課題】耐熱性や接合強度等の信頼性を高めることができるとともに、高い生産性を得ることができる半導体装置、表示装置及びそれらの製造方法を提供する。

【解決手段】基板上に半導体素子を有する半導体装置であって、上記基板は、半導体素子が配置されている側の面に凸部を有し、上記半導体素子は、基板の凸部の上面に配置されている半導体装置、及び、上記半導体装置の製造方法であって、上記製造方法は、半導体素子又はその構成要素を基板の凸部の上面に転写する工程を含む半導体装置の製造方法。

(もっと読む)

SOI基板の製造方法及び半導体装置の作製方法

【課題】ガラス基板など耐熱温度が低い基板を用いた場合にも、実用に耐えうる単結晶半導体層を備えたSOI基板の製造方法を提供することを目的の一とする。また、そのようなSOI基板を用いた信頼性の高い半導体装置を作製することを目的の一とする。

【解決手段】半導体基板より分離され、絶縁表面を有する支持基板に接合された半導体層に高エネルギーを有する少なくとも一種類の粒子により該高エネルギーを供給することにより加熱し、加熱した半導体層表面に研磨処理を行う。高エネルギーの供給による加熱処理により半導体層の少なくとも一部の領域を溶融させ、半導体層中の結晶欠陥を低減させることができる。さらに、研磨処理によって半導体層表面を研磨し、平坦化することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】平坦な表面を持つ画素電極を有する半導体装置を得ることを課題とする。

【解決手段】基板上に、絶縁膜と、前記絶縁膜に埋め込まれた第1の画素電極と、前記絶縁膜上に島状単結晶半導体層と、ゲート絶縁膜及びゲート電極と、前記島状単結晶半導体層及び前記ゲート電極を覆う層間絶縁膜と、前記高濃度不純物領域と前記第1の画素電極を電気的に接続する配線と、前記層間絶縁膜、前記島状単結晶半導体層、前記ゲート電極を覆い、前記第1の画素電極上の領域が開口された隔壁と、前記画素電極上の、前記隔壁に囲まれた領域に形成された発光層と、前記発光層に電気的に接続された第2の画素電極とを有し、前記第1の画素電極の、前記発光層と接する面は平坦であり、前記絶縁膜と前記島状単結晶半導体層が接する面と、前記第1の画素電極と前記発光層が接する面は、略一致する半導体装置とその作製方法に関する。

(もっと読む)

表示装置

【課題】均一な特性を有するトランジスタを有し、さらに表示ムラや画質低下などを防止した高画質かつ高信頼性を付与した表示装置を提供することを目的とする。

【解決手段】単結晶半導体基板より分離、接合され、支持基板上に設けられた単結晶半導体層を用いることによって、均一な特性を有するトランジスタとすることができる。さらに、バイポーラトランジスタを有するリファレンス回路を有することにより、画素の発光素子に電流を供給して駆動する駆動トランジスタの温度依存性を補償する。

(もっと読む)

TFT基板及びその製造方法、これを用いた表示装置、並びに層間絶縁膜の評価方法

【課題】

本発明によるポリシリコンTFT基板においては、欠陥密度の少ない層間絶縁膜を用いることで、高性能なTFT特性を提供することを目的とする。また、層間絶縁膜のE'センター密度を事前に測定し、TFT特性の予測しておくことで、TFT基板の評価期間を短縮すること。

【解決手段】

基板1上に絶縁膜を形成する工程と、ポリシリコン膜4を形成する工程と、ゲート絶縁膜7を形成する工程と、ゲート電極8を形成する工程と、層間絶縁膜10を形成する工程と、ポリシリコン膜4と接続するソース・ドレイン配線11を形成する工程と、保護膜12を形成する工程とを備え、層間絶縁膜10のE'センター密度を1.0×1018spins/cm3以下とする。

(もっと読む)

薄膜トランジスタ装置及びその製造方法

【課題】

薄膜トランジスタの性能のばらつきの低減を図ることができる薄膜トランジスタ装置及びその製造方法を提供すること。

【解決手段】

本発明にかかる薄膜トランジスタ装置は、絶縁基板上1にソース領域2a、ドレイン領域2b及びチャネル領域2cを含むシリコン層2と、ゲート絶縁層3と、ゲート電極4とを有する薄膜トランジスタと、薄膜トランジスタを覆う層間絶縁層5と、層間絶縁層5に設けられたコンタクトホール6を介して、ソース領域2a、ドレイン領域2b及びゲート電極4に電気的に接続された配線7とを備えた薄膜トランジスタ装置である。配線7及び層間絶縁層5を覆い、配線7及び層間絶縁層5の表面凹凸を緩和する第一の上部絶縁層8aと、第一の上部絶縁層8aを覆う第二の上部絶縁層8bとを備え、第二の上部絶縁層8bの水素拡散係数が第一の上部絶縁層8aの水素拡散係数より小さいことを特徴とするものである。

(もっと読む)

1 - 20 / 36

[ Back to top ]