Fターム[5E034CB04]の内容

サーミスタ、バリスタ (5,260) | バリスタの種類 (261) | 皮膜型 (112)

Fターム[5E034CB04]の下位に属するFターム

Fターム[5E034CB04]に分類される特許

1 - 20 / 21

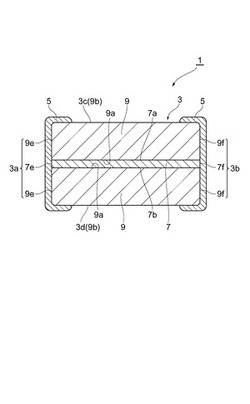

チップバリスタ

【課題】内部電極を備えることなく、ESD耐量を良好に維持しつつ、低静電容量化を図ることが可能なチップバリスタを提供すること。

【解決手段】素体3は、バリスタ部7と支持部9とを有している。バリスタ部7は、ZnOを主成分とし且つ副成分として希土類金属及びCoが含有する焼結体からなり、端子電極5に接続されるように素体3の一対の端面3a,3b間にわたって延び、電圧非直線特性を発現する。支持部9は、ZnOを主成分とし且つ副成分としてSr、Zr、及びCoを含有する焼結体からなり、端子電極5に接続されるように素体3の一対の端面3a,3b間にわたって延びている。バリスタ部7と支持部9とは、素体3の一対の端面3a,3b間にわたって延び且つ互いに接続される主面7a,7b,9a,9bを含んでいる。

(もっと読む)

保安器

【課題】劣化表示用の表示器の構造を簡単にし、表示器の表示部分を大きくして外部からの劣化表示の目視を容易にする。

【解決手段】保安器1は、線路に接続されるジャック盤10と、このジャック盤10に対して着脱可能に接続されるSPDプラグ40とにより構成されている。SPDプラグ40内には、線路から侵入する異常電圧等を抑制する保護素子と、劣化によってその保護素子が発熱する異常時にその保護素子を回路から切り離す切り離し部62と、連結部材51と、保護素子の劣化状態を表示する表示器70と、表示窓44等とが設けられている。切り離し部62の動作と連動して、ばね69の付勢力により連結部材51が上昇し、表示用テープ75が、案内突起72−1,72−2間に押し込まれる。これにより、テープ75で覆われていた着色面73が露出し、この表示面73の個所が表示窓44から目視できる。

(もっと読む)

電気的多層構成要素

互いに上下に配置された誘電層(2)および電極層(3)からなる積層体(1)を含む、電気的多層構成要素が記載される。電気的絶縁性の硬化要素(5)が少なくとも1つの電極層から隔てられて前記電極層と同一の誘電層上に配置され、前記硬化要素はそれを囲む誘電体材料と比較して大きい曲げ強度を有する。 (もっと読む)

電気的多層構成要素

並んで配置された誘電層(2)および電極層(3)の積層体(1)と、異なる極性を有する外部接点(4a、4b)と、を有し、前記外部接点(4a、4b)が、前記積層体(1)の外面(5a)に配置され、フリップチップ接点接続可能であり、前記電極層が、それぞれ1つの端部によって、同じ極性を有する外部接続部に接続される、電気的多層構成要素が示される。 (もっと読む)

回路保護素子及びその製造方法

本発明は回路保護素子及びその製造方法に関する。本発明による回路保護素子は、コイルパターン、内部電極、導電性物質が埋め込まれた孔及び磁性体物質が埋め込まれた孔が選択的に形成された複数のシートを有する共通モードノイズフィルターと、内部電極及びESD保護物質が埋め込まれた孔が選択的に形成された複数のシートを有するESD保護素子と、を備える。本発明によれば、ソレノイド型の共通モードノイズフィルターとESD保護素子を単一の素子として積層形成し、これを用いて電子機器の共通モードノイズとESDを同時に抑制することができる。このため、共通モードノイズとESDを保護するために個別素子を使用していた従来に比べて構成が簡素化されることから、電子機器のサイズ増加を防止することができ、入出力信号の歪みを防止することができて電子機器の信頼性を向上させることができる。 (もっと読む)

静電気対策部品の端面電極の導通確認方法

【課題】本発明は、簡単な構成により静電気対策部品の一対の端面電極の導通を確認でき、一対の裏面電極と一対の上面電極の電気的接続を保証することができる静電気対策部品の端面電極の導通確認方法を提供することを目的とするものである。

【解決手段】本発明の静電気対策部品の端面電極の導通確認方法は、第1の上面プローブ31を一方の上面電極22に、第2の上面プローブ32を他方の上面電極23に、第1の裏面プローブ33を一方の裏面電極27に、第2の裏面プローブ34を他方の裏面電極28にそれぞれ接触させ、さらに前記第1の裏面プローブ33と第2の裏面プローブ34との間を電気的に接続するように電流経路35を形成し、かつ前記第1の上面プローブ31と第2の上面プローブ32との間に電源装置36を接続したものである。

(もっと読む)

静電気対策部品およびその製造方法

【課題】本発明は、隣接する信号端子間でのクロストークの影響が少なく、信頼性に優れている複数回路用多端子タイプの静電気対策部品を提供することを目的とするものである。

【解決手段】本発明の静電気対策部品は、絶縁基板11の上面の長辺側両端部に形成された複数の上面電極17と、絶縁基板11の上面の短辺側両端部から中央部にかけて形成された上面グランド電極16と、複数の上面電極17と上面グランド電極16との間に形成されたギャップと、このギャップを充填する過電圧保護材料層20と、この過電圧保護材料層20を完全に覆う上面保護樹脂層21とを備え、前記過電圧保護材料層20を複数の上面電極17毎に独立するように形成したものである。

(もっと読む)

積層型電子部品

【課題】 積層体における端子電極の周辺部分にクラックが発生するのを防止することができる積層型電子部品を提供する

【解決手段】 積層型電子部品1においては、スルーホール131のうち、上面2bに最も近い位置に形成されたスルーホール131は、積層方向から見て端部3bと重なっていない。そのため、積層体2において本体部3aと端部3bとで挟まれた部分に生じる応力Pと、スルーホール131から積層方向に向かって積層体2に生じる応力Qとが集中するのを回避することができ、積層体2における端子電極31の周辺部分にクラックが発生するのを防止することが可能になる。

(もっと読む)

コヒーラ型サージアブソーバ

【課題】 従来型コヒーラを雷や強電力電路開閉時に生じる強電力サージ電流放電用に用いると、初期絶縁性は高いものの、コヒーラ自体が容易に焼損したり、一方でデコヒーア困難性が生じる傾向があり、使いづらいという問題点があった。

【解決手段】 そこで本発明者は、酸化物皮膜を有する金属粉末を電極間に介在させる従来型コヒーラでは、強大なサージ電力に対して安定したコヒーラ特性(短絡と開放)を期待する事が出来ない事を知り、種々実験探索の結果、半導体特性を持つ材料を、期待通りの特性を備え、自己デコヒーアする強電力サージ対応のコヒーラ型サージアブソーバを提供できる事を見出した。

更に圧密度を変化させる事により、コヒーラ特性(特に初期特性)を広範囲に変化させ得ることから、本発明では上記諸条件に加えて圧密度を変数とする各種用途の多変数コヒーラ型サージアブソーバを提供可能とした。

(もっと読む)

セラミックグリーンシート、積層型電子部品、及びその製造方法

【課題】 ナイフによる切断に好適なセラミックグリーンシート、そのようなセラミックグリーンシートが用いられてなる積層型電子部品、及びその製造方法を提供する。

【解決手段】 セラミックグリーンシート11は、その貯蔵弾性率が120MPa〜436MPaであるため、セラミックグリーンシート11が積層されてなるセラミックグリーン積層体12をナイフ13によって切断した際に、クラックやチッピングが発生するのを防止することができる。また、セラミックグリーンシート11は、その損失弾性率が12MPa〜56MPaであるため、セラミックグリーン積層体12をナイフ13によって切断した際に、セラミックミストが導体部の引出し端面を覆ったり、切断されたセラミックグリーン積層体12a同士が付着したりするのを防止することができる。

(もっと読む)

積層型チップバリスタ及び電子機器の製造方法

【課題】 実装面積を縮小することが可能な積層型チップバリスタを提供すること。

【解決手段】 積層型チップバリスタV1は、バリスタ素体1と、第1の外部電極5,6と、第2の外部電極7,8とを備える。第1の外部電極5,6は、バリスタ素体1の一方の主面2にそれぞれ形成される。第2の外部電極7,8は、バリスタ素体1の他方の主面3にそれぞれ形成される。バリスタ素体1は、バリスタ特性を発現する複数のバリスタ層と、それぞれ複数の第1の内部電極11及び第2の内部電極21とが積層された積層体として構成される。各第1の内部電極11は、第2の電極部分15及びスルーホール導体17を通して第1の外部電極5及び第2の外部電極7に電気的に接続される。各第2の内部電極21は、第2の電極部分25及びスルーホール導体27を通して第1の外部電極6及び第2の外部電極8に電気的に接続される。

(もっと読む)

積層装置、シートの積層方法、積層セラミック電子部品の製造方法

【課題】 積層・圧着時に上金型と下金型との間の圧力上昇によって上金型に吸着されたシートに穴が空くことを防止する。

【解決手段】 シート40aを吸着する吸着孔11を有し該シート40aを搬送する上金型10と、上金型10によって搬送されたシート40aを積層する下金型20と、を有し、上金型10と下金型20との対向面の中央部に、上金型10と下金型20との間の空気を排気する排気手段を有する。

(もっと読む)

積層型チップバリスタ

【課題】 バリスタ特性を良好に確保しつつ漏れ電流を減少させることができる積層型チップバリスタを提供すること。

【解決手段】 この積層型チップバリスタ1は、圧非直線特性を発現するバリスタ層11及び内部電極13,14を有する積層体3と、当該積層体3に形成され内部電極13,14に接続される外部電極5と、を備え、内部電極13,14は、バリスタ層11を挟むように設けられ、外部電極5は、内部電極13,14それぞれに接続されるように設けられ、内部電極13,14には、積層体3の積層方向に貫通する孔部13a,14aがそれぞれ形成されている。

(もっと読む)

急激な金属−絶縁体転移素子を用いた電気電子システム保護回路及びその回路を含む電気電子システム

定格標準電圧以上の高周波ノイズが、電気電子システムの電源ラインあるいは信号ラインを介して入るときに、当該ノイズを効果的に除去することができる急激なMIT素子を用いた電気電子システム保護回路及びその保護回路を含む電気電子システムを提供する。その電気電子システム保護回路は、ノイズから保護されるべき電気電子システムに並列連結される急激な金属−絶縁体転移素子(abrupt Metal−Insulator Transition device:以下、「急激なMIT素子」という。)を備える。電気電子システム保護回路は、定格標準電圧以上の電圧が印加されるときに発生するノイズ電流の大部分を急激なMIT素子側にバイパスさせることによって、電気電子システムを保護する。  (もっと読む)

(もっと読む)

積層セラミック部品

【課題】リード端子に機械的または急激な電気的な負荷がかかった場合においても、剥離や接合不良が生じない樹脂モールド型の積層バリスタを提供することを目的とする。

【解決手段】リード端子を、充分な長さを有する外部電極の回り込み部に設ける構成とすることにより、リード端子と外部電極との接続強度が増加し、機械的負荷や電気的負荷による故障が回避できるとともに、高エネルギーのサージを吸収した場合にも基板との接合を保つことができるチップ型積層バリスタとすることができる。

(もっと読む)

アレスタ

【課題】ブッシングの挿入孔内面とアレスタ素子積層体の外周に設けられたゴムモールド体外面との嵌合部の面圧を確保する。

【解決手段】アレスタは、ブッシング2を備えており、ブッシング2の先端部から後端部に向かって円錐状に広がるテーパ内面53bを有しており、このテーパ内面53bを介して上部挿入孔51aおよび下挿入孔52aが連通されている。高圧シールド体4は、シールド本体41を備えており、その側壁部41aの後端側端部の内側にテーパ内面53bが位置するように配置されている。アレスタモールド体6は、酸化亜鉛を主成分とする複数個のアレスタ素子61aを積層して成るアレスタ素子積層体61を備えており、アレスタ素子積層体61の外周にはシリコーンゴムなどから成るゴムモールド体67が設けられている。

(もっと読む)

積層型フィルタ

【課題】 バリスタ部とインダクタ部との剥離が生じ難い積層型フィルタを提供すること。

【解決手段】 好適な実施形態の積層型フィルタ10は、バリスタ部20とインダクタ部とが積層された構造を有している。バリスタ部30は、内部電極31a,32aを備えるバリスタ層31,32が積層されてなり、このバリスタ層は、ZnOを主成分とし、添加物として、Pr、Bi及びCoのうちの少なくとも一種の金属元素を含有している。また、インダクタ部20は、導体パターン21a〜24aを備えるインダクタ層21〜24が積層されてなり、このインダクタ層は、ZnOを主成分とし、添加物として、ZnOに対して0.02mol%以上2mol%以下のK、Na、Cs及びRbからなる群より選ばれる少なくとも一種の金属元素を含有しており、且つ、Pr、Bi及びCoを実質的に含有していないものである。

(もっと読む)

外部電極を備えた電子部品

本発明は、従来の熱硬化性導電ペーストの有する内部電極と外部電極の接合性の課題を解決し、基板への実装やメッキ処理に適した積層セラミック電子部品を提供しようとするものである。高融点の導電粒子、融点が300℃以下の金属粉末及び樹脂を含む熱硬化性導電ペーストで形成された外部電極を有することを特徴とする積層セラミック電子部品。  (もっと読む)

(もっと読む)

積層型バリスタ及びその製造方法

【課題】 内部電極の薄層化を図った場合でも、デラミネーションの発生を抑制しつつ、より一層大きなサージ耐量を得ることを可能とする積層型バリスタ、及びその製造方法を提供する。

【解決手段】 セラミック焼結体2内において、セラミック層を介して第1,第2の内部電極3,4が積層されており、第1,第2の内部電極3,4の第1,第2の外部電極5,6と接続されている接続端縁部を除く端縁部分である内部電極端縁部3c,4cの厚みが、内部電極端縁部3c,4cにより囲まれた内部電極中央部3a,4aの厚みの1.8〜4.0倍とされており、かつ内部電極端縁部3c,4cにおける貫通孔7aの存在割合が、内部電極中央部3a,4aにおける貫通孔7aの存在割合の0.017〜0.3倍の範囲とされている、積層型バリスタ1。

(もっと読む)

チップバリスタ

【課題】

サージに対する応答特性の向上を図る。

【解決手段】

バリスタ基板と、第1及び第2の外部電極と、バリスタ基板の第1の面上に形成され、第1及び第2の外部電極に接続され、当該第1及び第2の外部電極の幅より広い幅を有する信号用の導体層と、バリスタ基板の第1の面に対向する第2の面上に形成されるグランド用の導体層とを有する。このようにすれば信号用の導体層は低インピーダンス化され、さらに低ESLを実現することができる。従って、静電気等のサージに対する応答特性を向上させることができる。

(もっと読む)

1 - 20 / 21

[ Back to top ]