Fターム[5E034DB20]の内容

サーミスタ、バリスタ (5,260) | 構造(PTC、NTC、バリスタ) (356) | その他構造 (13)

Fターム[5E034DB20]に分類される特許

1 - 13 / 13

PTC素子用焼結体、その製造方法、PTC素子、及び発熱モジュール

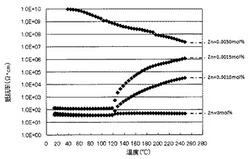

【課題】 Znを含むBaTiO3系のPTC素子用焼結体においてジャンプ特性に優れたPTC素子用焼結体、その製造方法、及びこのPTC素子用焼結体を用いたPTC素子、発熱モジュールを提供する。

【解決手段】 Ba、Tiを必須とするペロブスカイト系のPTC素子用焼結体であって、Znを焼結体全体に対して酸化物換算でZnO:0.0001−0.0030mol%含み、平均結晶粒径が10μm以上100μm以下であり、室温抵抗率Rrが1×105Ω・cm以下、抵抗温度係数αが0.5%/℃以上であることを特徴とする。

(もっと読む)

セラミック電子部品

【課題】内部電極と外部電極との接合強度を高めると共に、緻密な外部電極を得るセラミック電子部品を提供する。

【解決手段】本発明のセラミック電子部品は、セラミック素体と、前記セラミック素体の内部に設けられ、少なくともPdを含む内部電極と、前記セラミック素体の端面に設けられ、金属成分として少なくともCuとAgとを含むと共に、ガラス成分として結晶化ガラスを一種類以上含み、前記内部電極と導通する一対の外部電極とを有し、前記外部電極は、軟化点Tsが焼付温度よりも高い結晶化ガラスを50%以上含有する。

(もっと読む)

薄膜サーミスタ素子

【課題】 高い応答特性が得られると共に金属系の電極材料との密着性が良い保護膜が形成された薄膜サーミスタ素子を提供すること。

【解決手段】 アルミナ基板3と、アルミナ基板3上にサーミスタ材料で形成されたサーミスタ薄膜4と、サーミスタ薄膜4上に形成された一対の櫛形電極5と、櫛形電極5の少なくとも一部と共にサーミスタ薄膜4を覆うハフニウム酸化物またはハフニウム−金属酸化物で形成された保護膜6と、を備えている。

(もっと読む)

発光ダイオード、レーザーダイオード、フォトデテクタに適した電気的抵抗素子

本発明は電気的な抵抗素子に関している。この抵抗素子は、半導体材料によって形成された基体(2)と、この基体(2)と導電的に接続されている第1のコンタクト素子(5)と第2のコンタクト素子(6)とを有している。さらに前記基体(2)は第1の主要面(2a)を有しており、該第1の主要面(2a)内には凹部(3)が設けられており、前記第1のコンタクト素子(5)は前記凹部(3)内で少なくとも部分的に前記基体(2)と導電的に接続されており、前記基体(2)は、第2の主要面(2b)を有しており、該第2の主要面(2b)は前記第1の主要面(2a)と対向的に設けられており、前記第2のコンタクト要素(6)は第2の主要面(2b)に少なくとも部分的に前記基体(2)と導電的に接続されている。  (もっと読む)

(もっと読む)

温度センサ

【課題】広範囲な温度域にわたる温度計測と、特定の温度域における温度の高精度計測とを、従来より好適に両立できる温度センサを提供すること。

【解決手段】第1のサーミスタ素子54と第2のサーミスタ素子56とを、電気的に並列に接続した温度センサ1において、第1のサーミスタ素子54のB定数は1000〜2000Kで、第2のサーミスタ素子56のB定数は4000〜8000Kであり、且つ、第1のサーミスタ素子54のB定数と第2のサーミスタ素子56のB定数とが3.0倍以上異なる特性を有する。更に、所定温度より低温側にて、第1のサーミスタ素子54の抵抗値が第2のサーミスタ素子56の抵抗値より低く、且つ、所定温度より高温側にて、第1のサーミスタ素子54の抵抗値が第2のサーミスタ素子56の抵抗値より高い特性を有する。

(もっと読む)

樹脂封止型センサ

【課題】温度変化に起因して外装筒から封止樹脂が外れるのを防止し、耐久性を高めることができる樹脂封止型センサを提供する。

【解決手段】樹脂封止型センサ10は、金属製の外装筒15の内部に、封止樹脂14によってセンサ素子13を封止している。外装筒15は、軸方向に弾性変形可能な構造を有する。外装筒15は、周壁部23が線状部材24を螺旋状に巻回してなるコイルばねによって構成することができる。

(もっと読む)

サーミスタ素子とその製造方法

【課題】素体と外気との気密性が高く、比較的低温で処理することができ、サーミスタ素体と被覆材との反応が少なく、低温度から高温にわたり正確な温度検知が可能で、且つ安定性が高いサーミスタ素子とその製造方法を提供する。

【解決手段】サーミスタ素体10とその電極線12を被覆しシール性を有するコロイダルシリカを主成分とした第一の被覆材16と、電極線12が接続された耐熱リード線14と熱膨張係数が整合性を有する第二の被覆材18により覆われている。第二の被覆材18は、Mg2SiO4:Y2O3材料を主成分とする。第二の被覆材18は、耐熱衝撃性を有するセラミクスシール材として、コロイダルシリカと酸化鉄を主成分とする第三の被覆材20により覆われている。

(もっと読む)

多層式電気部品及び多層式電気部品を備えた回路

【解決手段】多層式電気部品は、交互に積層された複数のセラミック層(2)と複数の電極層(3)とを有する単一の基体(1)を備える。基体(1)は、互いに対向する2つの端面(4,4’)と、互いに対向する2つの側面(5,5’)とを備える。多層式電気部品は、複数の外部電極(6,6’)と、電極層(3)に配置された複数の内部電極(7,8,9)とを備え、複数の内部電極(7,8,9)が、少なくとも部分的に重なり合って重複領域を形成している。内部電極(7,8,9)のそれぞれは、外部電極(6,6’)に割り振られている。端面(4,4’)の一方から延びる少なくとも1つの第1内部電極(7)は、端面(4,4’)の他方から延びる少なくとも1つの第2内部電極(8)と重なっている。側面(5,5’)の1つから延びる少なくとも1つの第3内部電極(9)が第1内部電極(7)及び第2内部電極(8)に重なっている。 (もっと読む)

積層型チップバリスタ

【課題】クラックの発生及び、内部電極とスルーホール導体の接続不良を抑制することができる積層型チップバリスタを提供する。

【解決手段】内部電極21を、スルーホール導体27との接続部28において、スルーホール10の貫通方向に湾曲するように構成する。これにより、接続部28の湾曲面28aとスルーホール導体27との間に挟まれる領域Tを接続部28付近のバリスタ層9に形成する。この領域Tでは、バリスタ層9に対して内部電極21とスルーホール導体27の金属が拡散することによって金属濃度が高くなるため、焼成終了時において、内部電極41及びスルーホール導体47の収縮率と、バリスタ層9の他の領域の収縮率の中間の収縮率を有することとなる。これにより、内部電極41とスルーホール導体47とバリスタ層9が密集してクラックが発生し易い接続部28付近で、領域Tにより応力緩和する。

(もっと読む)

積層チップバリスタおよびその製造方法

【課題】素体の表面を保護しつつ、端子電極の形成部位以外の部位へのめっき金属の析出を抑制可能な積層チップバリスタおよびその製造方法を提供する。

【解決手段】本実施形態に係る積層チップバリスタ1は、半導体を主組成とした素体2と、素体2上に形成された端子電極8と、少なくとも端子電極8の形成部位以外の素体2の表層に形成された、アルカリ金属を含有する高抵抗層5と、高抵抗層5上に形成されたガラス層6と、を有する。

(もっと読む)

薄膜サーミスタ及び薄膜サーミスタの製造方法

【課題】 薄膜サーミスタ及びその製造方法において、小型化が可能で、サーミスタ薄膜自体にダメージを与えずに高精度に抵抗値調整可能にすること。

【解決手段】 表面にSiO2層2が形成されたシリコン基板3と、SiO2層2の上面にパターン形成されたサーミスタ薄膜4と、サーミスタ薄膜4上にパターン形成された一対の薄膜上電極5と、シリコン基板3の上面にサーミスタ薄膜4及び薄膜上電極5を覆って形成された絶縁性の保護膜6と、該保護膜6に形成された貫通孔の内面に一対の薄膜上電極5まで達した導電膜を形成した一対のスルーホール8と、保護膜6上に形成され一対のスルーホール8に一端が接続された一対の上部引き出し電極9と、を備え、一対の上部引き出し電極9の一部が、除去されて抵抗値調整されている。

(もっと読む)

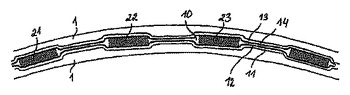

抵抗装置

第1の好ましい実施形態において、可撓式の柔軟な導電接続手段(12,14)によって第1の電極(201)が互いに導電接続されている抵抗素子(21,22,23)を含んでなる抵抗装置が提案される。前記接続手段は互いに隣接する2個の前記抵抗素子間に位置する区域において撓みが反転変化する。第2の好ましい実施形態において、柔軟な接続手段によって互いに接続されている抵抗素子(21,22,23)を含んでなる抵抗装置が提案される。前記抵抗素子(21,22,23)にはそれぞれ溝状の窪み(221,222)が配置されている。  (もっと読む)

(もっと読む)

温度検出素子

【課題】 温度検出素子において、製造コストの増大を抑制しつつ熱伝導性を向上を図ること。

【解決手段】 チップ状のサーミスタ素体2の表面に、第1の端子電極3と、第2の端子電極4と、絶縁性熱受容部6と、を設け、絶縁性熱受容部6が、サーミスタ素体2の少なくとも実装面となる側面2aに形成され側面2aで第1の端子電極3及び第2の端子電極4に対して面一な又は突出する厚さに設定されている。これにより基板に実装した状態で、基板に絶縁性熱受容部6が接触して効率的に基板からの熱をサーミスタ素体2に伝導させることができる。

(もっと読む)

1 - 13 / 13

[ Back to top ]