Fターム[5E070EA10]の内容

通信用コイル・変成器 (13,001) | 端子、リード(構成) (815) | その他の特徴 (14)

Fターム[5E070EA10]に分類される特許

1 - 14 / 14

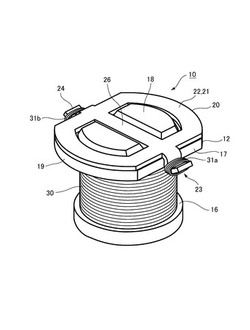

ドラムコアおよびこれを備える磁性素子

【課題】巻線に極細線を用いた場合にも巻線の断裂を防止することができるドラムコアの構造、およびかかるドラムコアを備える磁性素子を提供する。

【解決手段】ドラムコア10は、巻芯部と、この巻芯部の少なくとも一方の端部に形成された鍔部12と、可撓性のフィルム材で形成されて鍔部12に取り付けられたフィルム絡げ端子20と、を含んでいる。フィルム絡げ端子20に外力や熱衝撃が負荷されたとしても、このフィルム絡げ端子20が可撓性を有していることにより巻線30に与えられる応力が低減されるため、巻線30の断裂が防止される。

(もっと読む)

セラミック電子部品

【課題】外部電極を構成しているめっき膜が剥がれにくいセラミック電子部品を提供する。

【解決手段】セラミック電子部品1は、直方体状のセラミック素体10と、第1の外部電極13と、第2の外部電極14とを備えている。第1の外部電極13は、セラミック素体10の外表面の直上に形成されている第1のめっき膜13aを含む少なくともひとつのめっき膜からなる。第2の外部電極14は、セラミック素体10の外表面の直上に形成されている第2のめっき膜14aを含む少なくともひとつのめっき膜からなる。第1及び第2のめっき膜13a、14aのそれぞれの平面視における単位面積あたりの表面積が、1.02以上である。

(もっと読む)

電子部品

【課題】所望のフィルタ性能を確保しつつ、小型化且つ低背化され、低コストで製造可能な電子部品を提供する。

【解決手段】電子部品100は、磁性セラミック材料からなる基板11と、基板11の一方の主面に形成されたコイル導体を含む薄膜素子層12と、薄膜素子層12の主面にめっきにより形成された肉厚なバンプ電極13a〜13dと、バンプ電極13a〜13dの形成位置を除いた薄膜素子層12の主面に形成された絶縁体層14とを備えている。各バンプ電極13a〜13dはいずれも、絶縁体層14の主面に露出する第1の露出面と、絶縁体層14の端面に露出する第2の露出面を有しており、第1及び第3のバンプ電極13a,13cの第1の露出面の面積は、第2及び第4のバンプ電極13b,13dの第1の露出面の面積よりも大きい。

(もっと読む)

電子部品およびその製造方法

【課題】 チップ素体と外部電極との間の固着強度の向上が図られた電子部品およびその製造方法を提供する。

【解決手段】

本発明に係る積層チップインダクタ10の製造方法は、内部に所定の素子構造23が形成されたグリーン積層セラミック基板14を準備する工程と、グリーン積層セラミック基板14の一方面に、内側面15aが粗面化された複数の溝15を、並列するように所定間隔で形成する工程と、各溝15に導体ペースト17を充填する工程と、溝15に充填された導体ペースト17の表面を覆うように、各溝15に沿って延びる複数の電極パターン18を形成する工程と、各溝15に沿って切断して、グリーン積層セラミック基板14をチップ化する工程と、グリーン積層セラミック基板14をチップ化して得られたセラミックチップ22を焼成する工程とを含む。

(もっと読む)

金属端子付き電子部品及びその実装方法、並びにその製造方法

【課題】種々のリフロー条件にも耐えうる金属端子付き電子部品を提供すること。

【解決手段】セラミックコンデンサ1は、セラミック焼成体11と端子電極13とを有するコンデンサ素子3と、屈曲部5sを一端側に有する金属端子5と、金属端子5の一端側が端子電極13から張り出すように金属端子5をコンデンサ素子3に接合する接合部7とを備える。接合部7は、熱硬化性樹脂を含むはんだペースト27に含まれていたはんだによって端子電極13と金属端子5とを接合するはんだ接合部21と、はんだペースト27に含まれていた樹脂によってコンデンサ素子3と金属端子5とを接合する樹脂接合部23と、はんだ接合部21と樹脂接合部23との間の遷移領域を構成するはんだ樹脂混在部25とを有し、樹脂接合部23が、端子電極13の上面13aを覆うようになっている。

(もっと読む)

導電性ペーストおよびセラミック電子部品の製造方法

【課題】 セラミック電子部品の外部電極の形成に使用した場合に、リフトオフ(セラミックからの剥離)の発生する可能性が低い導電性ペーストを提供する。

【解決手段】 導電性金属粉末の焼結開始温度(℃)と、ガラスフリットのガラス転移点Tg(℃)とを、

(ガラスフリットのTg)−(導電性金属粉末の焼結開始温度)<100

の関係を満たすようにする。

(もっと読む)

電子部品及びその製造方法

【課題】本発明の目的は、渦電流の発生を抑制できる電子部品およびその製造方法を提供することである。

【解決手段】積層体12は、複数の絶縁体層16が積層されてなる。コイルLは、積層体12に内蔵され、かつ、z軸方向に沿って延在するコイル軸Axを有する。接続導体17は、絶縁体層16上に設けられ、かつ、コイルLの両端に対して電気的に接続されている。接続導体17は、絶縁体層16間から積層体12の外部に露出することにより外部電極として機能する。接続導体17には、z軸方向から平面視したときに、コイルLにより囲まれている領域の少なくとも一部と重なるように、導体が存在しない空白部B1〜B6が設けられている。積層体12の端面S1,S2には、導体が設けられていない。

(もっと読む)

巻き線一体型モールドコイルの製造方法

【課題】巻き線一体型モールドコイルにおいて、角丸め加工はモールドコイルの割れ欠けの防止の他、外部電極強度を向上させるため必要であるが、一般的なバレル研磨による角丸め加工では、モールド樹脂やメディアの削れカスがモールドコイルに付着しコイルの導通を阻害する。

【解決手段】

本発明はモールド成形後コイル端末処理する巻き線モールドコイルにおいて、該丸め加工にサンドブラスト法を用いたことを特徴とする。さらに、エポキシ樹脂の含浸や洗浄液中に酸化防止剤を添加することにより、耐環境特性に優れた巻き線モールドコイルの製造方法である。特に、外部電極に導電性樹脂を用いた場合に効果が高い。

(もっと読む)

ノイズフィルタ

【課題】 フィルタ部とコネクタ部を一体化し、かつコイルとコネクタの接続部を短くする、または削除するのでインピーダンス特性のバラツキ要因が排除され、特性の安定化と共に、小型化及び低コスト化も同時に実現しうるノイズフィルタの提供を目的とする。

【解決手段】 ノイズフィルタは、コイル1の空芯部にコア2とコネクタ端子4を同時に収納するボビンケース3を有し、コイル1とコネクタ端子4を直接接合する構造とする。

(もっと読む)

積層電子部品およびその製造方法

【課題】外部電極に端子電極がめっき形成されるときに、多孔質素体の表面へのめっき付着を十分に抑止でき、製品の信頼性低下を防止することが可能な積層電子部品およびその製造方法を提供する。

【解決手段】積層電子部品1は、セラミックスからなり複数の空孔を有する多孔質素体2と、多孔質素体2内に形成された複数の内部電極3とを含む積層体4を有するPTCサーミスタであり、多孔質素体2と内部電極3が積層された単位構造10を少なくとも1つ備えたものである。内部電極2には、外部電極5,5が接続されており、更にその上に端子電極7,7がめっきにより形成されている。多孔質素体2の複数の空孔には、樹脂が60%以上の充填率で充填されている。

(もっと読む)

熱的に安定な抵抗をもつインダクター

【構成】上面14、および対向する第1端面18および第2端面20を有するインダクター本体12、102、124からなるインダクター10、100、120である。対向する第1端面および第2端面の間においてインダクター本体に中空部分28を設ける。この中空部分に熱安定性抵抗要素30、84、98、122を配置し、上面に向けて折り曲げ、表面実装端子32、34、38、40、126、128を形成する。これら端子は、ケルヴィン型検出に使用できる。インダクター本体をフェライトで構成する場合、インダクター本体にスロット26を形成する。抵抗要素は、パンチ加工抵抗ストリップ84で構成することができ、部分巻き線または複数の巻き線部分94を与える。インダクターは、抵抗要素の周りに形成した分布型ギャップ磁性材料124から構成することができる。また、熱安定性抵抗要素の周りにインダクター本体12、102、124を配置し、熱安定性抵抗要素の端子をインダクター本体から延設するインダクターの製造方法が提供される。 (もっと読む)

チップ型電子部品およびその製造方法

【課題】 薄膜誘導素子などの薄膜回路を備えたチップ型電子部品において、構造が簡単で、製造工程を簡略化する。

【解決手段】 ウエハ状態のシリコン基板1上の複数のチップ型電子部品形成領域に対して、薄膜誘導素子用配線3、薄膜誘導素子8、下地金属層9、11を含む第1、第2の配線10、12、第1、第2の柱状電極15、16および第1、第2の半田ボール18、19の形成を一括して行ない、その後にダイシングストリートに沿って分断して複数個のチップ型電子部品を得る。この場合、第2の半田ボール19は、このチップ型電子部品を回路基板上に実装する際に、2つの第1の半田ボール18のみでは実装時の接続状態を補強するためのダミーである。

(もっと読む)

コイル部品およびそれに用いる磁性体

【課題】100MHz以上の帯域においても、磁気結合の低下を抑制したコイル部品およびそれに用いる磁性体を提供することを目的としている。

【解決手段】絶縁素体20は、コイル部22の内側に位置する中心部23を磁性体とし、隣接する導体21が対向する対向部24を非磁性体とし、磁性体は、主要相をスピネル型結晶構造にするとともに、FeとCuとZnとCoの組成比を、各々の酸化物換算で、Fe2O3は49〜50mol%、CuOは32〜35mol%、ZnOは15.5〜20.5mol%、CoOは0.05〜0.5mol%の範囲内とした構成である。

(もっと読む)

プリント回路基板

【課題】基板上の搭載部品を増加させず、すなわち基板を拡大することなくノイズ除去作用が得られ、部品点数も低減されるプリント回路基板を提供する。

【解決手段】プリント回路基板1上にノイズ対策多層基板3を搭載する。ノイズ対策多層基板3は、プリント回路基板1上の複数のコネクタ2a〜2dにそれぞれフレキシブルケーブルまたはフラットケーブル5a〜5dを介して接続する複数のコネクタ4a〜4dを有する。ノイズ対策多層基板3内に、コネクタ4aを介して接続されるライン上のノイズをそれぞれ除去するフィルタを内蔵する。ノイズ除去素子がノイズ対策多層基板3に集約される。

(もっと読む)

1 - 14 / 14

[ Back to top ]