Fターム[5E082FG04]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | 気体・固体誘電体 (7,068) | 気体・固体誘電体の形状、構造 (2,216) | 厚膜 (816)

Fターム[5E082FG04]に分類される特許

801 - 816 / 816

配線基板

【課題】 絶縁基板上に隣接して形成された伝送線路と薄膜コンデンサの上部電極および下部電極との間で発生する静電結合を少なくして良好な高周波特性を有する配線基板を提供すること。

【解決手段】 配線基板1は、絶縁基板2の主面に形成された凸部3の上面に形成された伝送線路4と、絶縁基板2の主面の伝送線路4に隣接する部位に、Ti,Ti合金,CrまたはCr合金から成る下部電極6および誘電体薄膜7および上部電極8が順次積層されて成る薄膜コンデンサ5とを具備しており、伝送線路4は、その下面が、下部電極6の上面よりも高く、その上面が上部電極8の下面よりも低い。伝送線路4と下部電極6または上面電極8との間の静電結合を少なくでき、伝送線路4の伝送特性を向上できる。

(もっと読む)

コンデンサ用の鉛フリー及びカドミウムフリーガラスを含有する銅成端インク

【課題】導電性インクの塗布への使用に特に適した鉛フリー及びカドミウムフリーガラス組成物。

【解決手段】本発明は、銅成端を備えるコンデンサを含み、銅成端はガラス成分を含むインクを焼成することによって製造され、ガラス成分はZnOを約65モル%以下、SrOを約51モル%以下、B2O3を約0.1から約61モル%、Al2O3を約17モル%以下、SiO2を約0.1から約63モル%、BaO+CaOを約40モル%以下、及びMgOを約20モル%以下を含んでもよい。

(もっと読む)

積層セラミック電子部品端子電極用導体ペースト

【課題】 積層セラミックコンデンサ、積層セラミックインダクタ、積層型圧電素子等の積層セラミック電子部品の端子電極を形成するための導体ペースト、特には、ニッケル等の卑金属内部電極を有する積層セラミック電子部品の、端子電極を形成するのに適した銅導体ペーストを提供する。

【解決手段】 少なくとも(A)銅を主成分とし、脂肪族アミンで表面処理された導電性粉末と、(B)ガラス粉末と、(C)有機ビヒクルとを含むことを特徴とする、積層セラミック電子部品端子電極用導体ペースト。該ペーストは、これを焼きつけて積層セラミック電子部品の端子電極とするに際し、銅系の導電性粉末の表面処理剤として脂肪族アミンを用いることにより、分散性が良好になるとともに、脱バインダ性が著しく改善され、このため緻密で接着性、導電性の優れた端子電極を形成することができる。

(もっと読む)

セラミックグリーンシート及び積層セラミック電子部品の製造方法

【課題】薄層シートとして実用に耐え得る高い強度の誘電体シートが得られる様に改良されたホットメルトコーティング用誘電体塗料組成物を使用したセラミックグリーンシートの製造方法を提供する。

【解決手段】支持体表面に誘電体塗料組成物をコーティングした後に乾燥してセラミックグリーンシートを製造するに当り、誘電体塗料組成物として、誘電体粉末、ポリオレフィン樹脂、分散剤としてのHLB4〜12の界面活性剤、沸点150〜230℃の炭化水素溶剤を含有して成り、誘電体粉末100重量部に対する各成分の割合が、ポリオレフィン樹脂6〜12重量部、界面活性剤0.5〜1.5重量部、炭化水素溶剤200〜300重量部であり、B型回転粘度計を使用し且つ130℃で測定した粘度が50〜150cpである誘電体塗料組成物を使用し、以下の式(1)に規定する温度(T)の範囲に加熱して支持体表面にホットメルトコーティングし、以下の式(1)に規定する温度(T)の範囲で少なくとも15分加熱乾燥する。

【数1】 (もっと読む)

(もっと読む)

セラミック電子部品およびその製造方法

【課題】 IR不良率(初期絶縁抵抗不良率)が低く、高温負荷寿命に優れ、高い信頼性を有する積層セラミックコンデンサなどのセラミック電子部品およびその製造方法を提供すること。

【解決手段】 誘電体層を有するセラミック電子部品であって、前記誘電体層が、(Ba,Ca)(Ti,Zr)O3 系材料を含む主成分と、Siの酸化物を含む副成分とを含有し、前記Siの酸化物の含有量が、誘電体層全体に対して、0〜0.4重量%(ただし、0は含まない)であり、好ましくは、前記誘電体層が、偏析層を有し、前記偏析層が、Siの酸化物を含み、かつ、Liの酸化物を実質的に含まないセラミック電子部品。

(もっと読む)

加圧装置及びその加圧方法

【課題】 被加圧体における歩留まりの低下を防止する。

【解決手段】 被加圧体を少なくとも加圧時に配置する配置部45と、配置された被加圧体に弾性部材を介して加圧を加える加圧プレート28と、加圧プレート28を囲み、刃本体56の先端に被加圧体の端部を切断する刃先57が形成された切断刃を有する刃ブロック32とを備えた加圧装置20に、配置部45を囲み、刃ブロック32に対向して位置し、被加圧体の端部を支持する移動ブロック48と、移動ブロック48を予め設定された高さ位置に弾性的に支持する弾性支持部とを設け、刃ブロック32及び移動ブロック48を切断刃の刃先57が被加圧体の端部を切断する位置まで接近させ、かつ被加圧体の加圧時に切断刃の刃本体56を被加圧体縁部に位置させるべく、刃ブロック32を介して、移動ブロック48を弾性支持部の弾性力に抗して移動させる。

(もっと読む)

絶縁体セラミック組成物、絶縁性セラミック焼結体および積層型セラミック電子部品

セラミック多層モジュール(1)のような積層型セラミック電子部品に備える多層セラミック基板(2)において積層される絶縁性セラミック層(3)のための絶縁体セラミック組成物であって、

フォルステライトを主成分とする第1のセラミック粉末と、CaTiO3、SrTiO3およびTiO2より選ばれる少なくとも1種を主成分とする第2のセラミック粉末と、ホウケイ酸ガラス粉末とを含み、ホウケイ酸ガラス粉末は、リチウムをLi2O換算で3〜15重量%、マグネシウムをMgO換算で30〜50重量%、ホウ素をB2O3換算で15〜30重量%、ケイ素をSiO2換算で10〜35重量%、亜鉛をZnO換算で6〜20重量%、および、アルミニウムをAl2O3換算で0〜15重量%含む。絶縁体セラミック組成物は、1000℃以下の温度で焼成可能であり、その焼結体は、比誘電率が低く、共振周波数の温度係数が小さく、Q値が高い。

(もっと読む)

内部で遮蔽されたエネルギー調節器

エネルギー調節構造体は第1電極、第2電極、及び遮蔽構造を有し、電気回路における改善されたエネルギー調節をもたらす。構造体は個別部品として、インターポーザ若しくは第1相互接続層の一部として、又は集積回路の一部として形成され得る。エネルギー調節構造体の遮蔽構造は如何なる回路素子とも電気的に接続されていない。  (もっと読む)

(もっと読む)

積層型セラミックコンデンサ

積層セラミックコンデンサを構成している積層誘電体素子本体内部での残留応力、又は積層誘電体素子本体の外表面での残留応力を所定の値以上にすることにより、誘電率が高く且つ取得静電容量の大きい信頼性の高い積層型セラミックコンデンサを得ることができる。 (もっと読む)

積層セラミック電子部品の内部電極用の導電体ペーストの製造方法

導電体材料濃度を所望のように制御しつつ、導電性材料が、高い分散性をもって、分散された導電体ペーストを製造することができる積層セラミック電子部品の内部電極用の導電体ペーストの製造方法を提供する。 導電体粉末と、バインダと、溶剤とを、粘土状に混練する混練工程と、前記混練工程によって得られた混合物に、混練工程で用いた溶剤と同一の溶剤を添加して、粘度を低下させ、前記混合物をスラリー化するスラリー化工程を含むことを特徴とする積層セラミック電子部品の内部電極用の導電体ペーストの製造方法。 (もっと読む)

誘電体セラミック組成物およびセラミック電子部品

1000℃以下の温度で焼結させることができ、焼結体の比誘電率が550以上であり、容量変化率の温度特性がJIS規格のB特性を満足し、電圧印加時においても比誘電率が実質的に変化しない、Ag−Cu−Nb−Ta−O系の誘電体セラミック組成物を提供する。 主成分がAgaCubNbcTadO3で表される組成を有し、AgaCubNbcTadO3において、0.7≦a≦0.95、0.05≦b≦0.3、0.4≦c≦0.6、および0.4≦d≦0.6の各条件を満足するとともに、0.95≦(a+b)/(c+d)≦1.02の条件を満足する、誘電体セラミック組成物。 (もっと読む)

超低インダクタンス多層セラミックコンデンサ

【課題】寄生インダクタンスの低いコンデンサを提供する。

【解決手段】低寄生インダクタンスを有する多層コンデンサは、第一の電極、第二の電極、誘電体、第一の接触部、および第二の接触部を備えている。第一の電極は実質的に長方形であり、第一の接触フィンガを有している。誘電体は第一の表面および第二の表面を有しており、第一および第二の表面は互いに対向するように配置されている。誘電体の第一の表面は第一の電極に連結されている。第二の電極は実質的に長方形であり、第一の接触フィンガを有している。第二の電極は誘電体の第二の表面に連結されている。第一の接触は、第一の電極の第一の接触フィンガに連結される。第二の接触は第二の電極の第一の接触フィンガに連結される。第二の接触は、寄生インダクタンスを減らすべく、第一の接触から最も小さい間隔だけ離れて配置される。

(もっと読む)

遮蔽エネルギー調整器

第1の電極、第2の電極、及び遮蔽電極を含む構造は、電気回路に用いられる際に改良されたエネルギー調整を与える。この構造は、別個の構成要素として、インタポーザ又は第1レベルのインタコネクトの一部として、又は、集積回路の一部として存在し得る。

(もっと読む)

(もっと読む)

プリント配線板製造用シート材、このプリント配線板製造用シート材を用いたプリント配線板の製造方法及びプリント配線板

【課題】 汎用的なシート材料を用いることにより低コストで簡便なプロセスにより、樹脂回路基板内に高精度のLCRや電波吸収部品層の内蔵化を歩留まり良く実現させることができるプリント配線板製造用シート材を提供する。

【解決手段】 支持体層2、金属層3、受動部品形成層4、金属層5の順に積層成形して成るプリント配線板の製造にあたり、支持体層2によって金属層3,5及び受動部品形成層4が支持されていると共に支持体層2の存在により金属層3がパターニングされていない状態で積層成形する。このことから成形時の受動部品形成層4の変形や割れが抑制される。この金属層3,5や受動部品形成層4によってコンデンサ、インダクタ、抵抗、電波吸収部品層等の回路部品を形成することにより、これらの回路部品をプリント配線板に内蔵すると共に受動部品形成層4の薄いものでも歩留まり良く高精度に形成することができる。

(もっと読む)

インバーテッドマイクロストリップ伝送線路

【課題】 線路間の結合を小さくして回路の面積を小型化できるインバーテッドマイクロストリップ伝送線路を提供する。

【解決手段】 誘電体基板11上に帯状のストリップ電極12を形成し、ストリップ電極12の上および両側面を覆うように誘電体層13を形成し、この誘電体層13上および側面さらに誘電体層13の形成されていない誘電体基板11上を覆うようにグランド電極14を形成し、ストリップ電極12からの電磁界をグランド電極14によって閉じ込め、線路間の結合を小さくする。

(もっと読む)

低インダクタンス埋め込みキャパシタを有するプリント配線板およびその製造方法

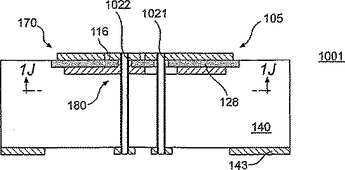

プリント配線板(PWB)は、受動回路素子(105)からなる積み重ねられた中間層パネル(1001、1002、1003、...)を有する。受動素子(105)は、電極終端がキャパシタ電極(170、180)のフットプリント内に位置付けられるキャパシタを含むことができる。したがってキャパシタ終端が、狭い間隔で離間して配置されるため、中間層内のループ・インダクタンスに対するキャパシタの寄与が減る。また電極フットプリント内にキャパシタ終端があることによって、キャパシタを形成する際に用いられるPWBボード表面積が減る。キャパシタ終端は、回路導体(1021、1022)によって接続される。  (もっと読む)

(もっと読む)

801 - 816 / 816

[ Back to top ]