Fターム[5E346DD48]の内容

多層プリント配線板の製造 (97,916) | 各層形成の方法 (10,210) | 配線パターン形成の方法 (3,161) | 画像転写方法が特定されたもの (474) | レジストに関するもの (177) | エッチングレジスト (84)

Fターム[5E346DD48]に分類される特許

1 - 20 / 84

プリント配線板及びその製造方法並びに熱硬化性樹脂組成物

【課題】所望の大きさの開口を有し且つ優れた信頼性を有するソルダーレジストを表面に備えるプリント配線板を効率的に製造する方法を提供すること。

【解決手段】本発明に係るプリント配線板の製造方法は、(I)プリント配線板上に感光性樹脂組成物で第一のパターンを形成する工程と、(II)第一のパターンの少なくとも一部を覆うように、プリント配線板上に熱硬化性樹脂組成物で第二の層を形成する工程と、(III)第二の層を熱硬化させる工程と、(IV)デスミア処理によって第二の層を研削して第一のパターンを露出させる工程と、(V)更なるデスミア処理によって第一のパターンを除去し、熱硬化性樹脂組成物の硬化物からなり且つプリント配線板の表面にまで至る開口を有するソルダーレジストを形成する工程とを備える。

(もっと読む)

配線基板、及び半導体パッケージ

【課題】電源インピーダンスを低くすることや、インピーダンスマッチングをとることが容易な無機材料を用いた配線基板、及び前記配線基板上に半導体チップを搭載した半導体パッケージを提供すること。

【解決手段】本配線基板は、無機材料からなる基板本体と、前記基板本体を厚さ方向に貫通する平板状の第1電極と、前記基板本体を厚さ方向に貫通する平板状の第2電極と、を有し、前記第1電極と前記第2電極とは所定の間隔を隔てて対向し、前記第1電極と前記第2電極との間には、前記基板本体を前記厚さ方向に貫通する信号電極が設けられ、前記第1電極と前記第2電極の何れか一方はグランド電極であり、他方は電源電極である。

(もっと読む)

半導体実装部材及び半導体実装部材の製造方法

【課題】 多配線への対応及び電源強化を図りながら歩留まりが下がらない半導体実装部材を提供する。

【解決手段】 半導体実装部材100を第2基板110と第1基板10との2つのプリント配線板で構成するため、多配線への対応及び電源強化の目的で、1枚のビルドアップ基板の層数を増やしサイズを大きくするのと比較し、歩留まりが低下しない。第1基板10と第2基板110との間に支持体188が介在するので、第1基板10と第2基板110との間にアンダーフィルを充填させる必要が無い。

(もっと読む)

プリント配線板

【課題】導体回路層と該導体回路層を覆う接着層との密着性を向上させることが可能なプリント配線板を提供する。

【解決手段】第1絶縁層11と、第1絶縁層11上に形成された第1導体回路層12と、第1導体回路層12上に形成された第2導体回路層13と、第1導体回路層12及び第2導体回路層13を覆うように、第1絶縁層11上に形成された接着層16と、接着層16上に形成された第2絶縁層17とを備え、第1絶縁層11と平行な面内での少なくとも一方向において、第1導体回路層12の幅よりも、第2導体回路層13の幅のほうが広く、第1絶縁層11の上面11aと第1導体回路層12の側面12aと第2導体回路層13の下面13aとに囲まれる凹状の空間18に、接着層16が、第1導体回路層12の側面12aに沿って、充填されている。

(もっと読む)

多層回路基板およびその製造方法

【課題】モールドを使用することなく低コストに多層回路基板を製造可能とする。

【解決手段】樹脂層11と、樹脂層11の表面に形成された段差を有する多段導電部12とを有し、多段導電部12の段差面12bが樹脂層11の最表面10aと略平行状態とされ、この段差面12bより先端側の層間接続ビア12cが金属箔101から形成され、前記段差面12bより樹脂層11の最表面10a側のパターン配線12dがめっきにより形成されてなる基板10。

(もっと読む)

リジッドフレキシブル基板およびその製造方法

【課題】リジッド部とフレキシブル部を構成する基板材料が同じでありながら、高い硬度を有するリジッド部と、屈曲性が良好で配線抵抗が低いフレキシブル部とを備えたリジッドフレキシブル基板、および、その製造方法を提供すること。

【解決手段】可撓性の絶縁性基板と、該絶縁性基板の少なくとも一方の表面に形成された導体配線層とを有するプリント基板を用いて作製され、導体配線層の密度が低いフレキシブル部と、該フレキシブル部よりも導体配線層の密度が高いリジッド部を有するリジッドフレキシブル基板であって、前記リジッド部の表面の少なくとも一部に平面電極を備え、前記平面電極が、Snを含有する第1金属と該第1金属よりも高い融点を有する第2金属との反応により生成する300℃以上の融点を有する金属間化合物を含み、前記第2金属の表面に最初に生成する金属間化合物の格子定数と前記第2金属の格子定数との差が、前記第2金属の格子定数に対して50%以上であることを特徴とする、リジッドフレキシブル基板。

(もっと読む)

多層回路基板、多層回路基板の製造方法および半導体装置

【課題】本発明は片面積層よりなる多層配線回路基板において、高温に放置しても反りが少なく、多層回路基板内に剥離、ボイドがない多層回路基板を製造することであり、半導体素子を実装する工程、半導体素子を実装した後に信頼性試験を行う工程において多層回路基板間に剥離がなく、反りが少ない多層回路基板及び半導体装置を提供することである。

【解決手段】複数組の導体回路層と絶縁層、及びソルダーレジスト層から形成され、ビア接続により導通接続したスルーホールを有するコア基板を含まない片面積層の多層回路基板であって、前記絶縁層のガラス転移温度が170℃以上であり、ガラス転移温度以下の線膨張係数が35ppm以下であり、弾性率が5GPa以上であり、前記ソルダーレジスト層のガラス転移温度が160℃以上、ガラス転移温度以下の線膨張係数が50ppm以下であることを特徴とする多層回路基板である。

(もっと読む)

サスペンション用基板、サスペンション、ヘッド付サスペンション、ハードディスクドライブおよびサスペンション用基板の製造方法

【課題】本発明は、伝送信号強度の損失を抑制しつつ、反りの発生抑制および低剛性化を図ることができるサスペンション用基板を提供することを主目的とする。

【解決手段】本発明は、ライト側配線構造およびリード側配線構造を有し、上記ライト側配線構造は、ライト側凹部を有する第一絶縁層と、上記ライト側凹部に形成されたライト側第一配線層と、上記ライト側第一配線層を覆う第二絶縁層と、上記第二絶縁層上であり、かつ、上記ライト側第一配線層に厚さ方向において重複するライト側第二配線層とを有し、上記リード側配線構造は、リード側凹部を有する上記第一絶縁層と、上記リード側凹部に形成されたリード側第一配線層と、上記リード側第一配線層を覆う上記第二絶縁層と、上記第二絶縁層上であり、かつ、上記リード側第一配線層に厚さ方向において重複するリード側第二配線層とを有することを特徴とするサスペンション用基板を提供することにより、上記課題を解決する。

(もっと読む)

電子部品及びプリント配線板

【課題】 高い容量を備える電子部品を提供する。

【解決手段】 Siコンデンサ10では、下部電極42と誘電体層44と上部電極46とから成るコンデンサ部40が、Si基板20に形成されたトレンチ30の壁面上に形成されているめ、下部電極42−誘電体層44−上部電極46の面積を広げることができ、高い容量を得ることができる。また、トレンチ30の内部に樹脂充填材52が充填されているため、トレンチ30の側壁で生じる応力を可撓性の有る樹脂充填材52で吸収することができ、凹部(トレンチ)を狭い間隔で設け容量の増大を図っても、トレンチ30の側壁へクラックが入ることが無い。

(もっと読む)

多層配線基板、及び多層配線基板の製造方法

【課題】電気的接続の高い信頼性を有するビアホール導体により層間接続された、Pbフリーのニーズに対応することができる多層配線基板を提供することを目的とする。

【解決手段】絶縁樹脂層と絶縁樹脂層の両面にそれぞれ配設された配線とこれらの配線間を電気的に接続するためのビアホール導体とを有し、ビアホール導体は金属部分と樹脂部分とを含み、金属部分は、配線間を接続する銅粒子の結合体を含む第一金属領域と、錫,錫‐銅合金,及び錫‐銅金属間化合物等を主成分とする第二金属領域と、ビスマスを主成分とする第3金属領域と、を有し、結合体を形成する銅粒子同士が互いに面接触することにより面接触部を形成し、第二金属領域の少なくとも一部分が第一金属領域に接触している多層配線基板である。

(もっと読む)

回路基板の製造方法

【課題】高密度な配線パターンを形成して、確実に導電性ペーストによる層間接続を行うことができる回路基板の製造方法を提供する。

【解決手段】基板11の一方の側の銅箔12の表面にマスキングテープ15を貼り付ける。マスキングテープ15及び銅箔12に開口部15a,12aを形成し、開口部12aに連通して、基板11にビアホール16を形成する。ビアホール16内に導電性ペースト18を充填し、マスキングテープ15を剥離して、導電性ペースト18を熱プレスする。ビアホール16の導電性ペースト18を押圧してリベット状に形成し、表面にエッチングレジスト19aを設ける。ビアホール16上のエッチングレジスト19aの大きさを、銅箔12による所望のランド部20の大きさよりも小さく形成する。エッチング時に、ビアホール16周辺の広がり部18aについて、その周縁部をエッチングにより除去するとともに、一部を残してエッチングを終了する。

(もっと読む)

積層基板の製造方法

【課題】LDI露光方式を用いて積層基板を製造する際に、積層による位置ずれの累積を抑えて、製品の歩留まりを向上させることができる積層基板の製造方法を提供する。

【解決手段】絶縁基板12を挟んで一方の側のランド部14と接続するビアホール15、及び他方の側のランド部14を形成する。フレキシブル基板等の絶縁基板12を挟んで、一方のランド部14に対する他方のランド部14の、所定の基準位置からのずれ量に対して、前記ずれ量を減少させる方向に、他方のランド部14の位置を移動させる位置補正を行って、レーザ光による回路パターンの描画を行う。この後、絶縁基板12を挟んで、一方の側のランド部14と接続するビアホール14、及び他方の側のランド部14を形成する。

(もっと読む)

多層配線基板

【課題】基板の反りを抑え、薄型化が可能なコア基板を備えない多層配線基板を提供する。

【解決手段】中央配線層20、配線層21、22、23、24を含む配線層は、ビア25を介して電気的に接続され、中央配線層20の一方の側のビア25と、他方の側のビア25とが、中央配線層20に向かう側が幅狭の台形状の断面形状となる対称向きに形成され、中央配線層20の一方の側に半導体素子搭載面が形成され、中央配線層20の一方の側の絶縁層31、33では他方の側の絶縁層32、34よりビア数が多く形成される。

【選択図】図1  (もっと読む)

(もっと読む)

ガラスセラミック焼結体およびそれを用いた配線基板、薄膜配線基板

【課題】 高強度、高ヤング率特性を有し、さらに低い誘電率と低い誘電損失を有するガラスセラミック焼結体、並びにかかるガラスセラミック焼結体を用いた配線基板および薄膜配線基板を提供する。

【解決手段】 実質的にZnOおよびTiO2を含有しない、(a)アスペクト比3以上の異方性結晶からなるセルシアン結晶相と、(b)フォルステライト結晶相、スピネル結晶相、エンスタタイト結晶相、の群から選ばれる少なくとも1種と、(c)アルミナ結晶相、ジルコニア結晶相のうち少なくとも1種の結晶相と、(d)BaOの含有量が10質量%以下である残留ガラス相とを含有してなり、かつ開気孔率が0.3%以下である。

(もっと読む)

回路基板とその製造方法、及び抵抗素子

【課題】回路基板とその製造方法、及び抵抗素子において、信頼性向上を図ること。

【解決手段】樹脂基材11と、樹脂基材11の上方に形成された抵抗素子30とを有し、抵抗素子30が、電極部13dと延在部13eとを備えた抵抗パターン13aと、抵抗パターン13aの電極部13d上に形成され、延在部13eに向かって厚さが薄くなる裾野部分31aを備えた電極31とを有する回路基板による。

(もっと読む)

配線基板及びその製造方法

【課題】低コストでPOP(パッケージ・オン・パッケージ)接続を容易に行えるようにし、その接続信頼性の向上を図ること。

【解決手段】配線基板(パッケージ)10は、複数の配線層が絶縁層を介在させて積層され、各絶縁層に形成されたビアを介して層間接続された構造を有している。この基板の一方の面側の最外層の絶縁層12の、チップ搭載エリアの周囲の領域には、当該絶縁層12の一部分を突出させて成形された当該部分の表面を覆ってバンプ状に形成されたパッドP2が配置され、チップ搭載エリア内には、その表面が当該絶縁層12から露出するパッドP1が配置されている。そして、このパッケージ10のパッドP1にチップ31がフリップチップ接続され、その周囲のバンプ状のパッドP2に他のパッケージ40が接続されている(POP接続)。

(もっと読む)

多層プリント配線板

【課題】 最外樹脂層上の導体の配置を適正化した新規な多層プリント配線板を提供すること、更に、半導体素子搭載用パッドに半田バンプを形成する際に、作業性の良い新規な多層プリント配線板を提供すること

【解決手段】 一方の面に複数個の半導体チップ接続用パッド(85)が形成され、反対面に他の基板に接続する外部接続端子(84)が形成された多層プリント配線板(40)であって、前記半導体チップ接続用パッドは、前記一方の面の中央領域に形成され、周辺領域には該半導体チップ接続用パッドを取り囲むようにスティフナー(42)が形成され、前記半導体チップ接続用パッド(85)及び前記スティフナー(42)は、同じ材料で、同じ高さで形成されており、前記スティフナーの実質的な面積は、複数個の前記半導体チップ接続用パッドの合計面積に基づいて決定されている。

(もっと読む)

配線パターン露光装置

【課題】導体で形成された配線パターンが積層されてなる多層配線板において、前記多層配線板の表層に形成されたフォトレジスト層に対し精度良く露光を行う。

【解決手段】多層配線板の微小領域に交番磁場を印加し計測対象パターン2で誘起された起電力の電圧値を検出する計測部5と、レーザ光を照射してフォトレジスト層を露光するレーザ露光部6と、レーザ露光部6を制御する制御部Contを備え、制御部Contが電圧値及び位置データより取得した多層配線板1の位置情報をもとに、露光パターンを決定し、レーザ露光部6を駆動してレーザ光を走査させつつ照射してフォトレジスト層の露光を行う配線パターン露光装置A。

(もっと読む)

多層積層回路基板

【課題】金属回路の断線が生じにくい多層積層回路基板を提供する。

【解決手段】多層積層回路基板1は、樹脂フィルム100と回路層200とを交互に積層させた積層構造を含む多層積層回路基板であって、上記樹脂フィルム100は、1つ以上のマルチ導通部110を有し、上記マルチ導通部110は、直径10μm以上3000μm以下の領域を占め、かつ2つ以上の導通ビア120を有し、該導通ビア120は、5μm以上300μm以下の内径を有することを特徴とする。

(もっと読む)

素子搭載用基板、半導体モジュール、携帯機器ならびに素子搭載用基板の製造方法

【課題】半導体素子を搭載するための素子搭載用基板、およびこの素子搭載用基板に半導体素子を搭載してなる半導体モジュールの製造時間を短縮する。

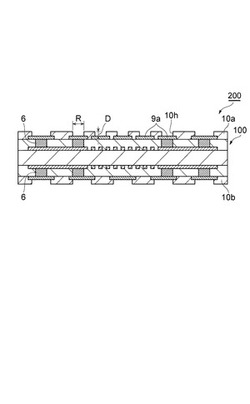

【解決手段】素子搭載用基板100は、非晶質のSi含有組成物からなる基材10、基材10の一方の主表面に設けられた第1接着層12、および基材10の他方の主表面に設けられた第2接着層14を含む基板構成単位15と、第1接着層12の基材10と反対側の主表面に設けられた第1配線層16と、第2接着層14の基材10と反対側の主表面に設けられた第2配線層18と、基材10、第1接着層12、および第2接着層14を貫通するビアホール19に設けられ、第1配線層16と第2配線層18とを電気的に接続するビア導体20と、を備える。

(もっと読む)

1 - 20 / 84

[ Back to top ]