Fターム[5F003AP07]の内容

バイポーラトランジスタ (11,930) | 目的 (494) | 雑音特性改善 (29)

Fターム[5F003AP07]に分類される特許

1 - 20 / 29

半導体装置及びその製造方法

【課題】バーティカル型のバイポーラトランジスタにおいて、エミッタ領域からベース領域にかけて存在する界面準位を安定に低減することを可能とした半導体装置とその製造方法を提供する。

【解決手段】バーティカル型のバイポーラトランジスタ10は、シリコン基板1に形成されたP型のベース領域13と、シリコン基板1に形成されてベース領域13に接するエミッタ領域15と、シリコン基板1の表面であってベース領域13とエミッタ領域15との境界部21上に形成されたシリコン酸化膜17と、シリコン酸化膜17上に形成されたポリシリコンパターン19と、を有する。シリコン酸化膜17とシリコン基板1との界面に塩素が1×1017cm−3以上の濃度で存在する。

(もっと読む)

半導体装置及びその製造方法

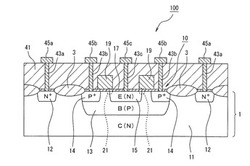

【課題】BiCMOSプロセスにより製造される半導体装置において、V−NPNトランジスタの製造工程を合理化する。また、そのトランジスタのhFEを大きな値に調整する。

【解決手段】N+型エミッタ領域14Eの下のP型ベース領域7の底部に接触してN型ベース幅制御層9が形成されている。N型ベース幅制御層9が形成されることで、N+型エミッタ領域14Eの下のP型ベース領域7が局所的に浅くなっている。また、P型ベース領域7は、P型ウエル領域6の形成工程を用いて形成し、N型ベース幅制御層9は、N型ウエル領域8の形成工程を用いて形成することにより、工程合理化を図ることができる。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】電流利得や電流利得遮断周波数などの他の素子性能を劣化させることなく、ヘテロ接合バイポーラトランジスタのオン電圧が効果的に低減できるようにする。

【解決手段】基板101の上に、サブコレクタ層102、コレクタ層103、ベース層104、第1エミッタ層105、第2エミッタ層106、および、キャップ層107が順次積層されており、第2エミッタ層106は、第1エミッタ層105に対してウェットエッチング法により選択的に除去される半導体材料によって形成され、かつ、第2エミッタ層106を構成する半導体が不純物添加によって縮退している。加えて、このHBTの第1エミッタ層105は、ベース層104の側に配置されて不純物が添加された第1半導体層151と、第2エミッタ層106の側に第1半導体層151に接して配置されて不純物が無添加の第2半導体層152とから構成されている。

(もっと読む)

不純物濃度プロファイルの測定方法、その方法に用いられるウェーハ、および、その方法を用いる半導体装置の製造方法

【課題】半導体層の不純物濃度およびプロファイルを正確に制御することを可能とする不純物濃度プロファイルの測定方法、その方法に用いられるウェーハ、および、それを用いた半導体装置の製造方法を提供する。

【解決手段】基板10と、前記基板10の主面上に設けられた半導体層12,17であって、前記主面上において互いに面積の異なる複数の第1領域17a,17bに形成された第1の部分と、前記主面上で前記第1領域17a,17bを取り囲む第2領域17cに形成され前記第1の部分とは異なる構造を有する第2の部分と、を有する半導体層12,17と、を有するウェーハを用いる。そして、前記半導体層のうちの複数の前記第1の部分の表面から深さ方向の不純物濃度プロファイルを測定し、前記第1の部分の面積に依存する前記不純物濃度プロファイルの変化を求める。

(もっと読む)

半導体装置の製造方法

【課題】本発明の実施形態は、ベース層の幅を狭く形成しエミッタ層の不純物濃度を高くした低雑音特性を有する半導体装置の製造方法を提供することを目的とする。

【解決手段】一実施形態に係る半導体装置の製造方法は、第1導電型の第1半導体層の上に第2導電型の第2半導体層を成長する半導体装置の製造方法であって、前記第1半導体層の表面を常圧よりも低い圧力の還元性雰囲気に曝して熱処理する工程(S02〜S04)と、前記第1半導体層の表面上に、前記第2半導体層を常圧の雰囲気でエピタキシャル成長する工程(S05〜S07)と、を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供することを目的とする。

【解決手段】第1、第2素子形成領域20、30に形成された半導体素子のうち、第1素子形成領域20に形成された半導体素子を外部機器と接続し、第1素子形成領域20と第2素子形成領域30との間に、第1導電型層60と、当該第1導電型層60に挟まれる第2導電型層61とを配置し、第1、第2導電型層60、61の間に、オフ時に半導体層12の表面から埋込絶縁膜11に達し、第1、第2素子形成領域20、30との間を仕切る空乏層63、64を構成する。

(もっと読む)

ESD保護素子

【課題】ESD耐量を向上させたESD保護素子を提供する。

【解決手段】本発明によるESD保護素子は、バイポーラトランジスタを用いたESD保護素子である。バイポーラトランジスタは、第1端子(Pad)に接続されるコレクタ拡散層7とエミッタ端子とを備えるバイポーラトランジスタと、第2端子(GND)からエミッタ拡散層4を介してコレクタ拡散層7に至る複数の電流経路上のそれぞれに設けられた電流制御抵抗11とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の特性を向上できると共に、製造コストを低減できる。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1上に順次積層されたコレクタ層2A、ベース層3A及びエミッタ層4Aと、コレクタ層2Aの側面上に設けられ、コレクタ層に対して歪み応力を与える第1ストレスソース膜15Aと、ベース層3Aの側面上に設けられ、ベース層3Aに対して歪み応力を与える第2ストレスソース膜17と、を具備し、第1ストレスソース膜15A上端及び前記ベース層上端は、半導体基板表面から同じ高さに位置し、第2ストレスソース膜17は、ベース層3Aの側面と第1ストレスソース膜15Aの側面との間に設けられる。

(もっと読む)

n型ベースを有するバイポーラトランジスタ及びその製造方法

【解決手段】ベースコンタクト接続部(12)、エミッタ部(4、5)及びコレクタ部がn層(3)上に配置され、当該n層は、更なるnpnバイポーラトランジスタために用いることができる。当該コレクタ部はエミッタ部に対して側方に配置され、当該エミッタ部及びコレクタ部の少なくとも一方は、当該n層の表面領域上でショットキーコンタクト(14)を備える。 (もっと読む)

半導体装置、並びにバイポーラトランジスタ及びその製造方法

【課題】本願発明は、単結晶エミッタと単結晶エミッタ引き出し層における結晶性の向上を実現する半導体装置とその製造方法を提供する。

【解決手段】本願発明の半導体装置は、ベース上に設けた高濃度p型単結晶SiGe層の表面が露出した開口部を有する絶縁膜の開口部において、底部の方を底部以外よりも広い開口幅とすることにより側壁に溝部を形成し、エミッタとなる高濃度n型単結晶Si層のファセット面の少なくとも一部を溝部の内側に設けている。これによって、エミッタとなる高濃度n型単結晶Si層のファセット面よりも成長方向の表面と主に接続させたエミッタ引き出し層となる高濃度n型単結晶Si層を形成している。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】バイポーラトランジスタおよびその製造方法に関し、エミッタ・ベース接合部における正孔に対する価電子帯端のエネルギー障壁を大きくするとともに、欠陥の少ないエミッタ・ベース接合部を形成してベース電流の再結合電流成分を抑えることで、電流増幅率を大きくすることができる。

【解決手段】Si元素からなるコレクタ層と、Si,Ge,Cの元素から成るベース層と、Si,Cの元素から成るSiCx(xはCの元素の組成比)を含むエミッタ層を備え、前記エミッタ層と前記ベース層との界面で、前記エミッタ層のSiCxはx=0であり、前記エミッタ層と前記ベース層との界面から前記エミッタ層に向かう方向に、前記エミッタ層のSiCxのxの値が増加することを特徴とする。

(もっと読む)

貼り合わせ基板の製造方法およびそれによって製造される貼り合わせ基板

【課題】安価に製造することができ、そこに形成される各種半導体素子の特性を阻害することなく高集積化できる貼り合わせ基板の製造方法および貼り合わせ基板を提供する。

【解決手段】SOI層1aとなる第1基板11aの一方の第1面1S側に、埋め込み絶縁分離トレンチTを形成する、埋め込み絶縁分離トレンチ形成工程と、第1面1S側に、埋め込み拡散層1b,1cとなる不純物層1ib,1icを形成する、不純物層形成工程と、第1基板11aにおける第1面1S側を支持基板2となる第2基板11bに対向するようにして積層し、第1基板11aと第2基板11bを互いに貼り合わせる、基板貼り合わせ工程と、貼り合わされた第1基板11aのもう一方の第2面2S側を研磨して、埋め込み絶縁分離トレンチTを基板表面に露出し、SOI層1aとする基板研磨工程とを有する貼り合わせ基板11の製造方法とする。

(もっと読む)

電力変換装置およびワイドギャップバイポーラ半導体素子の駆動方法

【課題】ワイドギャップバイポーラ半導体素子を高信頼性かつ低損失で駆動でき、可制御電流を大きくできる電力変換装置を提供する。

【解決手段】この電力変換装置では、SiC−GTOサイリスタ1の稼動に先立ち、温度上昇用n型MOSFET11のゲート13に信号を印可してオンさせ、電源14 → アノード端子2 → ゲート端子4 → 抵抗12 → 温度上昇用n型MOSFET11 → 電源14の経路で温度上昇用電流(加熱電流)として約40Aの電流を流す。上記温度上昇用電流により、SiC−GTOサイリスタ1の温度を上昇させる。これにより、サイリスタ1の稼動により積層欠陥が増大したとしても、オン電圧の増大や最小ゲート点弧電流の増大、ターンオン時間の増大およびオフ時の電流の不均衡の増大などの劣化現象を抑制できる。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタにおける高利得化および低雑音化を同時に実現できる技術を提供する。

【解決手段】ベースパッド31およびコレクタパッド32の下部にエミッタ(基準(接地)電位)と電気的に接続された配線24が設けられた基板シールド構造とすることにより、ベースパッド31およびコレクタパッド32と配線24との間では容量が設けられた構造として電力消費をなくし、基板1からの熱雑音は、配線24を介して基準(接地)電位へと逃がし、ベースパッド31およびコレクタパッド32へは届かないようにする。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】ベース抵抗が小さく、最大発振周波数などの高周波特性が優れ、低雑音なバイポーラトランジスタおよびその製造方法を提供する。

【解決手段】Siコレクタ層3a上に、SiGeスペーサ層4a、傾斜SiGeベース層4b、Siキャップ層5が形成され、Siキャップ層5上にエミッタ引き出し電極7が形成され、エミッタ引き出し電極7およびそのサイドウォール直下を除いたSiGeスペーサ層4a、傾斜SiGeベース層4b、Siキャップ層5にボロン注入でベース引き出し電極11が形成され、リンをSiキャップ層5中に拡散してエミッタ拡散層5aが形成され、ボロンをSiコレクタ層3a中に拡散して外部ベース拡散層1cが形成され、エミッタ拡散層5aの直下の真性ベース領域Bint に対して、ベース引き出し電極11と外部ベース拡散層1cで構成される外部ベース注入領域Bexを自己整合的に形成し、ベースリンク領域を削除し、ベース抵抗を低減できる。

(もっと読む)

バイポーラトランジスタを有する半導体装置

【課題】熱暴走対策としてエミッタバラスト方式を採用するRF信号増幅用のパワーバイポーラトランジスタ(HBT)を採用したRF電力増幅器全体の電力利得と電力効率とを改善すること。

【解決手段】ひとつのパワー素子を構成する複数のユニット・トランジスタには、ぞれぞれエミッタバラスト抵抗が接続されている。その結果、複数のユニット・トランジスタの複数のベースには、1個の結合容量CによりRF入力信号を共通に供給できる。RF入力信号が供給される1個の結合容量Cの一方の電極プレート100の配線幅Wを、複数のベースへの信号注入配線領域204_1、204_2…204_Nの配線幅wより大きくする。複数のコレクタ増幅出力信号の間での位相差が小さくなる。

(もっと読む)

高周波半導体装置

【課題】 良好な歪特性を得るためには電流容量の増大が必要である。従来では高周波半導体装置において櫛状パターンのエミッタ領域の数を増加させることにより電流容量を増大させていた。そのためエミッタ領域およびベース領域の増大に伴い電力利得および雑音指数特性が悪くなる問題があった。

【解決手段】 エミッタ領域を複数の島状に形成し、エミッタ領域の周囲にコンタクトする格子状のベース領域を設ける。エミッタ領域の短辺の長さを、エミッタ総周囲長が飽和値となり、且つエミッタ総面積をできるだけ小さくなるように設定する。これにより、ベース領域の面積が櫛状パターンと同じ場合と比較してエミッタ領域の面積増加をわずかに抑え、エミッタ領域の総周辺長を増加させることができる。従って良好な高周波特性を保ちつつ電流容量を増大させることができ、結果として良好な歪特性を得ることができる。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】 サブコレクタ層のドーピング濃度および厚みを殆ど変えることなく、サブコレクタ層のシート抵抗を下げ、コレクタ抵抗を低減し、オン抵抗が小さく且つ雑音の少ないヘテロ接合バイポーラトランジスタを提供することを目的とする。

【解決手段】 サブコレクタ層をヘテロ接合を利用した量子井戸構造とすることにより、サブコレクタ層中に移動度の高い2次元電子ガスを発生させ、コレクタ電流としてこの2次元電子ガスを用いることにより、サブコレクタ層のシート抵抗を低減させオン抵抗を低減することができる。また、コレクタ電流として、2次元電子ガスを用いることで熱雑音の発生が抑えられ、雑音特性に優れたヘテロ接合バイポーラトランジスタを提供することができる。

(もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】 バイポーラトランジスタの製造方法において、高調波歪みを増加させることなく、ベース・コレクタ耐圧を増加させる。

【解決手段】 バイポーラトランジスタの製造方法は、エミッタ領域の下部のコレクタ領域にSIC層を有するバイポーラトランジスタの製造方法であって、中央部における不純物濃度よりも4つのコーナー部における不純物濃度が低いSIC層を形成する工程を含む。

(もっと読む)

ベースアクセス抵抗を改善したNPNバイポーラトランジスタ用の方法及び装置

複数の短エミッタからなる構造は、共通のDTI領域及びベースポリの単一巨大片を共有する。これにより、ベース電流が、2方向のみとは対照的に、4方向(例えば2次元)に流れることができる。これにより、より優れたNPNトランジスタRF性能及び高周波ノイズ性能に不可欠なトランジスタのベース抵抗の顕著な低減がなされる。  (もっと読む)

(もっと読む)

1 - 20 / 29

[ Back to top ]