Fターム[5F003BE02]の内容

バイポーラトランジスタ (11,930) | エミッタ (1,226) | 付加領域(PN接合、絶縁物、溝、キラー) (75)

Fターム[5F003BE02]に分類される特許

1 - 20 / 75

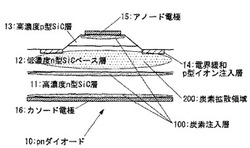

SiCバイポーラ型半導体素子

【課題】キャリア捕獲中心の少ないSiC半導体素子を提供する。

【解決手段】n型またはp型のSiC基板11と、n型またはp型の少なくとも1つのSiCエピタキシャル層12、あるいはn型またはp型の少なくとも1つのイオン注入層14と、を有し、pn接合界面付近および伝導度変調層(ベース層)内を除いた、SiC基板表面付近、SiC基板とSiCエピタキシャル層との界面付近、およびSiCエピタキシャル層の表面付近のうち少なくとも1つの領域100に、炭素注入層、珪素注入層、水素注入層、またはヘリウム注入層を有し、かつ、炭素原子、珪素原子、水素原子、またはヘリウム原子をイオン注入することで導入した格子間炭素原子をアニーリングにより伝導度変調層内へ拡散させるとともに格子間炭素原子と点欠陥とを結合させることで、電気的に活性な点欠陥が低減された領域を伝導度変調層内に有するSiCバイポーラ型半導体素子。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】電流利得や電流利得遮断周波数などの他の素子性能を劣化させることなく、ヘテロ接合バイポーラトランジスタのオン電圧が効果的に低減できるようにする。

【解決手段】基板101の上に、サブコレクタ層102、コレクタ層103、ベース層104、第1エミッタ層105、第2エミッタ層106、および、キャップ層107が順次積層されており、第2エミッタ層106は、第1エミッタ層105に対してウェットエッチング法により選択的に除去される半導体材料によって形成され、かつ、第2エミッタ層106を構成する半導体が不純物添加によって縮退している。加えて、このHBTの第1エミッタ層105は、ベース層104の側に配置されて不純物が添加された第1半導体層151と、第2エミッタ層106の側に第1半導体層151に接して配置されて不純物が無添加の第2半導体層152とから構成されている。

(もっと読む)

半導体装置の製造方法

【課題】異なる直流電流増幅率(hfe)を有する複数のバイポーラトランジスタを混載した半導体装置を、簡易且つ工程数が少なく得られる半導体装置の製造方法を提供すこと。

【解決手段】第2バイポーラトランジスタ20のエミッタ領域25又はその周囲上であって、当該エミッタ領域25におけるコンタクト領域25Aの周辺上にダミー層52を形成することで、その後、層間絶縁層53の厚みを厚層化することができるため、第2バイポーラトランジスタ20のエミッタ領域25では第1バイポーラトランジスタ10のエミッタ領域15に比べコンタクト深さを浅くしてコンタクトホール54が形成される。これにより、第1バイポーラトランジスタ10と第2バイポーラトランジスタ20との直流電流増幅率(hfe)を変更できる。ダミー層52の形成は第2バイポーラトランジスタ20のベース領域26、コレクタ領域27であってもよい。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製法

【課題】高い電流増幅率を有し、高周波特性および素子寿命に優れたヘテロ接合バイポーラトランジスタおよびその製法を提供すること。

【解決手段】半絶縁性基板1上に、n型半導体より成る真性エミッタ層16と、p型ドーパントを高濃度でドーピングされ、真性エミッタ層16よりも狭いバンドギャップを有する半導体より成るベース層9と、ベース層9と同じ半導体より成るコレクタ層10とを、この順序で積層して成るへテロ接合バイポーラトランジスタにおいて、真性エミッタ層16の周囲に、高抵抗領域15が設けられ、高抵抗領域15と真性エミッタ層16との間に、真性エミッタ層16の半導体と同じ半導体から成るガードリング領域17が設けられ、真性エミッタ層16とベース層9との接合面が、ガードリング領域17の上面よりも下に位置することを特徴とするヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

バイポーラ・トランジスタ構造およびその製造方法

【課題】エミツタ・ベース間の接合界面特性の最適化により、性能が改善されたバイポーラ・トランジスタ構造そのおよび製造方法を提供する。

【解決手段】バイポーラ・トランジスタは、(1)半導体基板内に少なくとも部分的に位置決めされたコレクタ領域15と、(2)コレクタ領域に接触するベース領域16と、(3)ベース領域に接触するエミッタ領域16Aとを含む。エミッタ領域とベース領域の界面は、酸素不純物と、フッ素不純物および炭素不純物から成るグループから選ばれた少なくとも1つの不純物とを含む損傷領域16Aをエミツタ開口のベースを含む層16に形成することにより、バイポーラ・トランジスタの性能を改善する。それらの不純物は、ベース領域を構成するベース材料のプラズマ・エッチング処理または代わりに無水アンモニアおよびフッ化水素処理が後に続く熱処理によって界面に導入することができる。

(もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】バイポーラトランジスタにおいて、耐圧改善のためにコレクタ濃度を低くした際のトランジスタとしての性能低下を抑制する。

【解決手段】バイポーラトランジスタ100は、コレクタ層3上に、エピタキシャル成長されたヘテロ接合の真性ベース層50を有する。真性ベース層50は、分離層4に囲まれたコレクタ層3上に配置され、コレクタ層3の表面部に、N型不純物層30が形成されている。N型不純物層30の不純物濃度は、N型不純物層30の下方におけるコレクタ層3の不純物濃度よりも高い。N型不純物層30と真性ベース層50との間に、N型不純物層30及び真性ベース層50よりも不純物濃度が低いエピタキシャル成長層が形成されている。

(もっと読む)

接合の作製方法

【課題】バイポーラトランジスタのエミッタ−ベース界面において、ドーパント濃度プロファイルを制御する方法を提供する。

【解決手段】第1濃度を有する第1ドーパントを含む第1半導体材料を形成する工程と、その上に、第2濃度を有し、これにより接合を形成する、第2ドーパントを含む第2半導体材料を形成する工程と、第2半導体材料を形成する前に、原子層エピタキシまたは気相ドーピングにより、第1半導体材料の上に、第2ドーパントを形成するのに適した、単分子層の少なくとも一部分の前駆体を堆積し、これにより接合における第2ドーパントの第2濃度を増加させる工程と、を含む(またはこれらの工程からなる)。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の特性を向上できると共に、製造コストを低減できる。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1上に順次積層されたコレクタ層2A、ベース層3A及びエミッタ層4Aと、コレクタ層2Aの側面上に設けられ、コレクタ層に対して歪み応力を与える第1ストレスソース膜15Aと、ベース層3Aの側面上に設けられ、ベース層3Aに対して歪み応力を与える第2ストレスソース膜17と、を具備し、第1ストレスソース膜15A上端及び前記ベース層上端は、半導体基板表面から同じ高さに位置し、第2ストレスソース膜17は、ベース層3Aの側面と第1ストレスソース膜15Aの側面との間に設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、半導体装置及びその製造方法等に関し、バイポーラトランジスタの面積を縮小してトランジスタの高集積化が可能な半導体装置及びその製造方法等提供する。

【解決手段】本発明に係る半導体装置及びその製造方法は、第1導電型半導体にベース領域6を形成後、第1のシリコン窒化膜8及びシリコン酸化膜9を形成する。シリコン酸化膜に溝を形成し、第2のシリコン窒化膜10を形成する。第1及び第2のシリコン窒化膜をエッチバックすることでカバー膜10aを形成する。溝の底面上及びカバー膜の内側にポリシリコンエミッタを形成し、第3のシリコン窒化膜13を形成する。第3のシリコン窒化膜及びカバー膜をマスクとして自己整合的にシリコン酸化膜をエッチングすることで、カバー膜の周囲に位置し且つ前記ベース領域上に位置する開口部を形成し、ベース領域を露出させ、導電膜17aを形成する工程とを具備することを特徴とする。

(もっと読む)

縦型バイポーラトランジスタ及びその製造方法

【課題】 サリサイドオフセット領域の形成により、ベース側の空乏層が十分に広がり、リーク電流や接合耐圧低下の問題を防ぐサリサイド処理を行った縦型バイポーラトランジスタを提供する。

【解決手段】 縦型バイポーラトランジスタは、半導体基板1に形成された第一導電型(N型)のコレクタ領域2と、コレクタ領域2内に形成された第二導電型(P型)のベース領域5と、ベース領域5内に形成された第一導電型のエミッタ領域6と、ベース領域5を囲むようにコレクタ領域2の表面部に形成されたフィールド酸化膜4と、ベース領域5上に形成されたサリサイド層14とを具備する。ベース領域5の表面は、サリサイド層14が形成されたサリサイド領域と、フィールド酸化膜4の端部とサリサイド領域の端部との間にサリサイド層が形成されていないサリサイドオフセット領域15とが設けられている。

(もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】バイポーラトランジスタの高周波特性の向上を図る。

【解決手段】p型シリコン基板10上に形成されたn型導電型の第1コレクタ層14と、第1コレクタ層14上に形成された、第1コレクタ層14より幅の狭い、n型導電型の第2コレクタ層21と、第1コレクタ層14上に、第2コレクタ層21側面に接して形成された絶縁膜層20と、第2コレクタ層21上に形成された、p型導電型のベース層22と、ベース層22側面に接してに形成された、p型導電型のベース引き出し層25と、ベース層22上に形成された、n型導電型のエミッタ領域32とを備える。第1コレクタ層14とベース層22の間、又は第1コレクタ層14とベース引き出し層25の間に、絶縁膜層20が形成されていることにより、ベース・コレクタ間の接合容量を低減させる。

(もっと読む)

n型ベースを有するバイポーラトランジスタ及びその製造方法

【解決手段】ベースコンタクト接続部(12)、エミッタ部(4、5)及びコレクタ部がn層(3)上に配置され、当該n層は、更なるnpnバイポーラトランジスタために用いることができる。当該コレクタ部はエミッタ部に対して側方に配置され、当該エミッタ部及びコレクタ部の少なくとも一方は、当該n層の表面領域上でショットキーコンタクト(14)を備える。 (もっと読む)

バイポーラトランジスタの製造方法及びバイポーラトランジスタ

【課題】バイポーラトランジスタの高周波特性を向上させる。

【解決手段】ヘテロバイポーラトランジスタ70は、ベースとエミッタ、ベースとコレクタがヘテロ接合を有し、双条ベース構造を有する。N型エピタキシャル層3上の内部ベース層(P型SiGe層)5と接する外部ベース層10、及び内部ベース層(P型SiGe層)5上には、絶縁膜7及びN型多結晶シリコン膜8が積層形成される。積層形成された絶縁膜7及びN型多結晶シリコン膜8の中央部にはエミッタ開口部19が設けられる。エミッタ開口部19にはN型エピタキシャル層11が設けられる。N型エピタキシャル層11及びN型多結晶シリコン膜8上には、エミッタ開口部19を覆うようにT型形状を有するN型多結晶シリコン膜12が設けられる。左右のN型多結晶シリコン膜8及びエミッタ開口領域は同時に形成され、左右のN型多結晶シリコン膜8の幅は同一に設定される。

(もっと読む)

ポリエミッタ型バイポーラトランジスタ、BCD素子、ポリエミッタ型バイポーラトランジスタの製造方法及びBCD素子の製造方法

【課題】複合高電圧素子工程を用いたポリエミッタ型バイポーラトランジスタ及びその製造方法、BCD(複合高圧)素子及びその製造方法を提供する。

【解決手段】実施の形態に係るポリエミッタ型バイポーラトランジスタは、半導体基板100の上側の一部に形成された埋込層110と、上記半導体基板の上に形成されたエピ層120と、上記エピ層に形成され、上記埋込層と連結されるコレクタ領域130と、上記エピ層の上側の一部に形成されたベース領域140と、上記ベース領域の基板の表面に形成され、ポリシリコン材質からなるポリエミッタ領域170と、を含む。実施の形態に係るBCD素子は、ポリシリコン材質からなるポリエミッタ領域を含むポリエミッタ型バイポーラトランジスタを含み、上記バイポーラトランジスタと同一な単一ウエハ上に形成されたCMOSとDMOSのうちの1つ以上のMOSを含む。

(もっと読む)

トンネル素子およびその製造方法。

【課題】大きなトンネル電流が流れ、かつ接合抵抗の制御性のよいトンネル素子およびその製造方法を提供すること。

【解決手段】本発明は、GaAsを含む半導体膜10と、半導体膜10上に設けられた酸化ガリウム膜20と、酸化ガリウム膜20上に設けられた導電性膜30と、を具備し、酸化ガリウム膜20は、半導体膜10および導電性膜30の一方から他方にトンネル電流が流れるトンネル絶縁膜であるトンネル素子およびその製造方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、エミッタ拡散層等を形成する際のマスクずれにより、デバイスサイズが縮小され難く、高耐圧化が達成され難いという問題があった。

【解決手段】本発明の半導体装置では、エミッタ領域としてのP型の拡散層18の周囲には、LOCOS酸化膜14、15、N型の拡散層22、23が形成される。N型の拡散層22、23の周囲には、コレクタ領域としてのP型の拡散層19、20が、N型の拡散層22、23と離間して形成される。この構造により、P型の拡散層18〜20、N型の拡散層22、23が位置精度良く形成され、ベース領域幅Wb1が狭められ、高耐圧の横型PNPトランジスタが形成される。

(もっと読む)

半導体装置

【課題】SiGe混晶層を有する半導体装置において、高い高周波特性と安定した低いベースコンタクト抵抗とを得られるようにする。

【解決手段】半導体装置は、N型のコレクタ層1aと、コレクタ層1aの上に形成され、P型SiGe層3bを含む真性ベース層となるSiGeエピ膜3と、SiGeエピ膜3の周囲に形成され、P型の多結晶シリコン層及びP型の多結晶シリコンゲルマニウム層を含むベース引き出し電極4と、SiGeエピ膜3の上部に形成されたN型のエミッタ層8とを有している。真性ベース層の上部には、Si−Cap層3cが形成されており、エミッタ層8は、Si−Cap層3cの上部に形成された上部エミッタ領域8bと、該上部エミッタ領域8bの下側に該上部エミッタ領域8bと接して形成された下部エミッタ領域8aとにより構成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】非選択エピタキシャル法により半導体層を形成しても、エミッタとベースとを確実に接続して高い信頼性を確保することができる半導体装置及びその製造方法を提供する。

【解決手段】非選択エピタキシャル成長法により、ベース開口部8の内壁を覆うようにシリコン酸化膜7の全面にSiGe膜9を成長させる。このときの成膜条件としては、ベース開口部8内において、底部9aが単結晶からなり、側壁部9b等のその他の部位が多結晶となると共に、側壁部9bの膜厚が底部9aの膜厚の1.5倍以下になる成膜条件を選択する。このような非選択エピタキシャル成長では、原料ガスとして、モノシラン、水素、ジボラン及びゲルマンを用いる。このとき、モノシラン及び水素の各流量は、夫々20sccm、20slmとする。また、成長温度を650℃、ジボランの流量を75sccmに設定し、ゲルマンの流量を35sccmに設定する。

(もっと読む)

半導体装置およびその製造方法

【課題】同一基板上に形成された縦型PNPトランジスタとNPNトランジスタの両方の特性向上が図られた半導体装置を提供する。

【解決手段】半導体装置はPNPトランジスタ50を備えている。PNPトランジスタ50は、第1のP型コレクタ領域3bと、第1のP型コレクタ領域3bの底面を覆い、第1のP型コレクタ領域3bの不純物濃度のピークよりも深い位置に不純物濃度のピークを有する第1のN型埋め込み領域2と、第1のP型コレクタ領域3b上に形成された第2のP型コレクタ領域5bとを備えている。第1のP型コレクタ領域3bの側面もN型領域に囲まれている。このため、PNPトランジスタ50におけるパンチスルーの発生が抑えられるとともに、コレクタ領域内のキャリア通過経路を短くしてコレクタ抵抗の低減を図ることができる。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの特性が劣化するのを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置100の製造方法は、シリコン基板11の領域A上にプレーナ型のバイポーラトランジスタ1を形成する工程と、プレーナ型バイポーラトランジスタ1が形成される領域を覆うようにシリコン窒化膜からなるカバー膜32aを形成する工程と、その後、プレーナ型のバイポーラトランジスタ1が形成される領域Aがカバー膜32aに覆われた状態で、バイポーラトランジスタ1が形成される領域にイオン注入する工程とを備える。

(もっと読む)

1 - 20 / 75

[ Back to top ]