Fターム[5F005AA03]の内容

Fターム[5F005AA03]に分類される特許

21 - 40 / 53

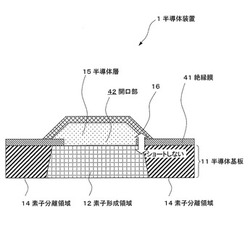

半導体装置およびその製造方法

【課題】エピタキシャル成長層上に形成したシリサイド層やエピタキシャル成長層と半導体基板とがショートを起こすのを防止することを可能にする。

【解決手段】半導体基板11に形成された素子分離領域14によって分離された該半導体基板11の素子形成領域12と、前記半導体基板11上に形成された絶縁膜41と、前記素子形成領域12の選択エピタキシャル成長させる領域上を含むように前記絶縁膜41に形成された開口部42と、前記開口部42内の半導体基板11の素子形成領域12より選択エピタキシャル成長により形成された半導体層15とを有することを特徴とする。

(もっと読む)

半導体装置

【課題】可制御電流が大きく、低損失のパワー半導体装置に適したアセンブリ構造を提供すること。

【解決手段】金属基板125と、絶縁板126と、金属膜7とを備える。金属基板125上に、ワイドギャップ半導体層からなるバイポーラスイッチング素子20を備える。金属膜7上に、n型ワイドギャップ半導体層を含むダイオード素子13を備える。バイポーラスイッチング素子20の低電位側の主電極32は、金属基板125に直接に半田付けされている。一方、バイポーラスイッチング素子20の高電位側の主電極29は、金属膜7に配線34、7aを介して電気的に接続されている。ダイオード素子13の低電位側の主電極32は、金属膜7に直接に半田付けされている。一方、ダイオード素子13の高電位側の主電極6は、金属基板125に配線8を介して電気的に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】PNPN接合で形成されるサイリスタRAMのn型領域をリン(P)がドープされたエピタキシャル成長膜で形成することを可能にする。

【解決手段】p型の第1領域(第1p型領域p1)とn型の第2領域(第1n型領域n1)とp型の第3領域(第2p型領域p2)とn型の第4領域(第2n型領域n2)とが順に接合されたサイリスタを有し、第2p型領域p2にゲート電極23を有する半導体装置1において、第1n型領域n1および第2n型領域n2の一方もしくは両方は第2p型領域p2上にエピ成長によるn型の半導体層で形成され、n型の半導体層は、n型の第1不純物の表面偏析を抑制するn型の第2不純物をドーピングしながら形成した第1半導体層上に前記第1不純物をドーピングしながらかつ第1半導体層中の第2不純物を表面偏析させつつ第1半導体層をさらに成長させて第2半導体層を形成したものからなる。

(もっと読む)

半導体装置の製造方法

【課題】可制御電流が大きく、低損失のパワー半導体装置を作製すること。

【解決手段】順方向特性にビルトイン電圧を有するワイドギャップバイポーラ半導体素子を形成するように、互いに異なる導電型を有する少なくとも2層のワイドギャップ半導体層1、2、3を積層する。積層欠陥を有するワイドギャップ半導体層1、2、3に、所定の照射エネルギーのγ線、電子線または荷電粒子線を所定量照射する。

(もっと読む)

半導体装置及びその製造方法、動作方法、この半導体装置を用いた電力変換装置

【課題】可制御電流が大きく、かつ低損失のパワー半導体装置を得ること。

【解決手段】ワイドギャップ半導体を用いた、順方向特性にビルドイン電圧を有するワイドギャップバイポーラ半導体素子13を備える。ワイドギャップバイポーラ半導体素子13を収納し、ワイドギャップバイポーラ半導体素子13を外部の装置に接続するための電気接続手段7、8、9、11を有する半導体パッケージ10、14を備える。半導体パッケージ10、14内の前記ワイドギャップバイポーラ半導体素子13を50℃以上、750℃以下の温度範囲に加熱するための発熱手段15を備える。

(もっと読む)

半導体装置の製造方法

【課題】サイリスタ構成の半導体装置において、アノード側の第1p型領域p1とn型の第1n型領域n1との界面を、急峻な濃度プロファイルに形成することを可能とする。

【解決手段】第1伝導型の第1領域(第1p型領域p1)と、前記第1伝導型とは逆伝導の第2伝導型の第2領域(第1n型領域n1)と、第1伝導型の第3領域(第2p型領域p2)と、第2伝導型の第4領域(第2n型領域n2)とが順に接合されたサイリスタを有する半導体装置1の製造方法において、前記第1n型領域n1をn型の不純物をドーピングしながらエピタキシャル成長により形成する工程と、前記第1n型領域n1の表層を除去する表面処理を行う工程と、前記表面処理をした第1n型領域n1上に、前記第1p型領域p1をp型の不純物をドーピングしながらエピタキシャル成長により形成する工程とを備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】急峻な不純物プロファイルを呈する第1n型半導体層と第1p型半導体層とを備えたサイリスタを有する半導体装置の製造方法を提供する。

【解決手段】第1p型半導体層p1と、第1n型半導体層n1と、第2p型半導体層p2と、第2n型半導体層n2とを順に接合してなるサイリスタを有する半導体装置の製造方法であって、半導体基板11の表面層に、p型不純物を含む第2p型半導体層p2を形成する工程と、エピタキシャル成長により、第2p型半導体層p2が設けられた半導体基板11上に、n型不純物を含む第1n型半導体層n1を形成する工程と、エピタキシャル成長により、第1n型半導体層n1上に、ノンドープ半導体層mを形成する工程と、エピタキシャル成長により、ノンドープ半導体層m上に、p型不純物を含む第1p型半導体層p1を形成する工程とを有する半導体装置の製造方法である。

(もっと読む)

サイリスタ

【課題】 本発明の目的は良好なdV/dt−VCL特性を得る。

【解決手段】 第1導電型のエミッタ層2と、前記第1導電型と反対の第2導電型のベース層3と、前記第1導電型のバルク層5と、前記第2導電型の対面ベース層6とが順に平行的に配置され、前記ベース層および前記バルク層間に、該バルク層より高濃度の第1導電型の埋め込み層4が配置されたサイリスタ1において、前記埋め込み層は、前記ベース層と接する面を第1接合面および前記バルク層と接する面を第2接合面とするとき、該第2接合面の端が前記第1接合面に向かって傾斜を有して接し、かつ前記第1接合面の端が前記第2接合面の端に向かって所定の傾斜を有することを特徴とする。

(もっと読む)

半導体装置及びその駆動方法

【課題】ターンオフ時間を短くできるサイリスタを有する半導体装置を提供する。

【解決手段】基板に第1導電型の第1半導体領域20が形成され、第1半導体領域の表層部に第2導電型の第2半導体領域22とアノードとなる第2導電型の第3半導体領域23とアノードゲートとなる第1導電型の第4半導体領域24が形成され、また、第2半導体領域の表層部にカソードとなる第1導電型の第5半導体領域26とカソードゲートとなる第2導電型の第6半導体領域25が形成され、第1半導体領域と第2半導体領域の境界から第2半導体領域と第5半導体領域の境界までの領域における第2半導体領域の上層にゲート絶縁膜30及びゲート電極31が形成され、第3半導体領域、第4半導体領域、第6半導体領域及び第5半導体領域に入出力用の導電層が形成されており、第3半導体領域、第1半導体領域、第2半導体領域及び第5半導体領域からサイリスタが構成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】セル面積を縮小化するとともに、サリサイドプロセスによるサイリスタを構成する領域間の短絡を防ぐことを可能とする。

【解決手段】第1伝導型の第1領域21と、第2伝導型の第2領域22と、第1伝導型の第3領域23と、第2伝導型の第4領域24とが順に接合されたもので、第3領域23が半導体領域(半導体基板11)に形成されたサイリスタ20、および第3領域23上に形成されたゲート(ゲート電極32)を有する半導体装置1であって、第2領域22は第3領域23上に形成された絶縁膜40の第3領域23に達する開口部47内部に形成され、第1領域21は開口部47内の第2領域22上から絶縁膜40上の一部にかけて形成され、第1領域21上、ゲート電極32上、第4領域24上に金属シリサイド膜25、26,27が形成されていることを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】移動度を高めることで、オンからオフへのスイッチング速度を高速化することを可能とする。

【解決手段】第1伝導型の第1領域(第1p型領域p1)と、前記第1伝導型とは逆伝導の第2伝導型の第2領域(第1n型領域n1)と、第1伝導型の第3領域(第2p型領域p2)と、第2伝導型の第4領域(第2n型領域n2)とが順に接合されたもので、該第3領域(第2p型領域p2)にゲート(ゲート電極14等)が形成されたサイリスタ2を有する半導体装置1であって、前記サイリスタ2の第1領域乃至第4領域は、シリコンゲルマニウム領域もしくはゲルマニウム領域に形成されていることを特徴とするものである。

(もっと読む)

半導体装置およびその駆動方法

【課題】バルク半導体基板を用い、選択セルと非選択セルとを区別し、選択セルのみをオフさせて、オンからオフへのSRAMメモリセル用サイリスタのスイッチング速度を高速化させることを可能とする。

【解決手段】バルク半導体基板10に、ゲート電極13が形成されたサイリスタ3と、このサイリスタ3に接続された電界効果トランジスタ4とからなる記憶素子2を複数有する半導体装置1であって、電界効果トランジスタ4のカソード側にビット線BLが接続され、選択された記憶素子2(2a)のオフ動作時に、選択された記憶素子2aのサイリスタ3の第1領域p1側に第1電圧が印加され、その記憶素子2aの電界効果トランジスタ4のカソード側に第1電圧よりも高い第2電圧が印加され、その記憶素子2aと同じビット線BLに接続する非選択の記憶素子2bの電界効果トランジスタ4に形成されたワード線WLに第1電圧よりも低い電圧が印加される特徴を有する。

(もっと読む)

発光素子アレイ、発光装置および画像形成装置

【課題】 少ない駆動用ICで時分割駆動することができる発光素子アレイおよびそれを用いた小型な発光装置ならびにその発光装置を備える画像形成装置を提供する。

【解決手段】 発光ダイオードDとスイッチ用サイリスタSSを並列接続したn(nは2以上の整数)個スイッチデバイスSと、前記スイッチ用サイリスタSSのゲート電極gに個別に接続されるn本の信号伝送路GHと、前記n本の信号伝送路GHのうちのいずれか1つとゲート電極hが接続される複数の発光用サイリスタTとを含んで発光素子アレイチップ1を構成する。スイッチデバイスSのアノードa,cに共通のセレクト信号(ハイレベル)が入力されている発光素子アレイチップ1を発光させることができるので、発光信号(ハイレベル)およびゲート信号(ローレベル)を複数の発光素子アレイチップ1間で共用する時分割駆動が実現できる。

(もっと読む)

電流抑制層付き静電誘導サイリスタ、電流抑制層付き静電誘導サイリスタの保護回路及びパルス発生回路

【課題】負荷短絡時に過電流を抑制し、ターンオフ時間を短縮する電流抑制層付き静電誘導サイリスタを提供する。

【解決手段】高抵抗半導体層1と、高抵抗半導体層1の第1表面に配置されたカソード領域7と、高抵抗半導体層1の第2表面に配置されたアノード領域6と、高抵抗半導体層1中のカソード領域7近傍に埋め込まれて形成されたゲート領域2と、ゲート領域2に隣接して配置された電流抑制層3と、ゲート領域2及び電流抑制層3と、7カソード領域との間に配置されたエピタキシャル成長層8と、カソード領域7にオーミック接触するカソード電極5と、6アノード領域にオーミック接触するアノード電極4とを備える電流抑制層付き静電誘導サイリスタ。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】サイリスタを構成する一部の領域を積層構造とすることで、素子面積の縮小化を図るとともにパンチスルー耐性の向上を図ることを可能とする。

【解決手段】第1伝導型の第1領域(第1p型領域p1)と、前記第1伝導型とは逆伝導の第2伝導型の第2領域(第1n型領域n1)と、第1伝導型の第3領域(第2p型領域p2)と、第2伝導型の第4領域(第2n型領域n2)とが順に接合されたサイリスタを有するとともに、前記第3領域にゲート電極23を有する半導体装置1において、前記第2領域(第1n型領域n1)は半導体基体(半導体基板21)に形成され、前記第2領域上に前記第1領域(第1p型領域p1)が形成されているものである。

(もっと読む)

半導体装置およびその製造方法

【課題】サイリスタの一部を半導体基板上に形成することで、従来のCMOSサイリスタプロセスを大幅に変更することなく、素子面積を縮小化することを可能とする。

【解決手段】半導体基板11に形成されたものでMIS型ゲート30を有するサイリスタ20を備えた半導体装置1であって、サイリスタ20は、第1導電型の第1領域21と、第1導電型領域21とは逆導電型の第2導電型の第2領域22と、第1導電型の第3領域23と、第2導電型の第4領域24とを直列に接続したものからなり、第1領域21、第2領域22および第3領域23は半導体基板11に形成され、第3領域23は半導体基板11面より上方に立ち上げて形成され、第4領域24は上方に立ち上げて形成された第3領域23上に形成されているものである。

(もっと読む)

半導体装置、半導体装置の駆動方法、および半導体装置の製造方法

【課題】スイッチング速度、とくにオン状態からオフ状態への高速でのスイッチングが可能なサイリスタ構成の半導体装置、さらにはこのような半導体装置の駆動方法および製造方法を提供する。

【解決手段】第1のp型領域p1、第1のn型領域n1、第2のp型領域p2、および第2のn型領域n2がこの順に接して設けられた半導体層101、第1のp型領域p1に接続されたアノード電極Aと、第2のn型領域n2に接続されたカソード電極Kと、第1のn型領域n1と第2のp型領域p2とに、それぞれ独立して制御可能に接続されたゲート電極Gn1,Gp2とを備えたことを特徴とする半導体装置。

(もっと読む)

電界効果トランジスタおよびサイリスタ

【課題】耐圧の低下を可及的に防止することを可能にする。

【解決手段】SiCからなるドレイン領域2と、ドレイン領域上に設けられたn型のSiCからなるドリフト層4と、ドリフト層の表面に設けられたn型のSiCからなるソース領域18と、ソース領域の側部のドリフト層の表面に設けられたSiCからなるチャネル領域12aと、チャネル領域上に設けられた絶縁ゲート22と、ソース領域の底部とドリフト領域との間に設けられ2種類のp型不純物を含むp型のベース領域15と、を備えている。

(もっと読む)

双方向阻止能力を有する高電圧炭化珪素デバイス及びその作製方法

高電圧炭化珪素(SiC)デバイス、例えばサイリスタ、が提供される。第1の伝導型を有する第1のSiC層が、第2の伝導型を有する電圧阻止SiC基板の第1の表面に設けられる。SiCの第1の領域が第1のSiC層の上に設けられ、第2の伝導型を有する。SiCの第2の領域が、第1のSiC層の中に設けられ、第1の伝導型を有し、SiCの第1の領域に近接している。第1の伝導型を有する第2のSiC層が、電圧阻止SiC基板の第2の表面に設けられる。SiCの第3の領域が、第2のSiC層の上に設けられ、第2の伝導型を有する。SiCの第4の領域が、第2のSiC層の中に設けられ、第1の伝導型を有し、SiCの第3の領域に近接している。第1および第2のコンタクトが、SiCの第1および第3の領域の上にそれぞれ設けられる。関連する高電圧SiCデバイスの作製方法も提供される。  (もっと読む)

(もっと読む)

炭化珪素デバイスおよびその製作方法

たとえばサイリスタのような高電圧炭化珪素(SiC)デバイスが提供される。第1の導電型を有する第1のSiC層が第2の導電型を有する電圧遮断用SiC基板の第1の表面上に備えられる。SiCの第1の領域が第1のSiC層上に備えられ、この領域は第2の導電型を有する。SiCの第2の領域が第1のSiC層内に備えられる。SiCの第2の領域は第1の導電型を有し、SiCの第1の領域に隣接している。第1の導電型を有する第2のSiC層が電圧遮断用SiC基板の、第1の表面とは反対側の第2の表面上に備えられる。第1、第2、および第3の電極がそれぞれSiCの第1の領域、SiCの第2の領域、および第2のSiC層上に備えられる。高電圧SiCデバイスの作製に関する方法も提供される。  (もっと読む)

(もっと読む)

21 - 40 / 53

[ Back to top ]