Fターム[5F005AA03]の内容

Fターム[5F005AA03]に分類される特許

41 - 53 / 53

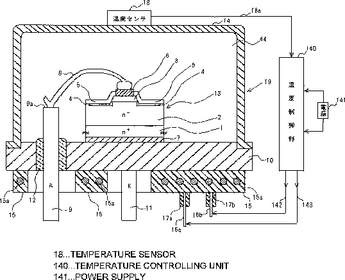

半導体装置及びその製造方法、この半導体装置を用いた電力変換装置

可制御電流が大きく、かつ低損失のパワー半導体装置を得るために、ワイドギャップ半導体を用いるバイポーラ半導体素子の温度を、ヒーターなどの加熱手段を用いて上昇させる。その温度は、ワイドギャップバイポーラ半導体素子の、温度の上昇に応じて低下するビルトイン電圧の低下量に対応する前記ワイドギャップバイポーラ半導体素子の定常損失の減少量が、前記温度の上昇に応じて増加するオン抵抗の増加量に対応する前記定常損失の増加量よりも大きくなる温度を超える温度にする。  (もっと読む)

(もっと読む)

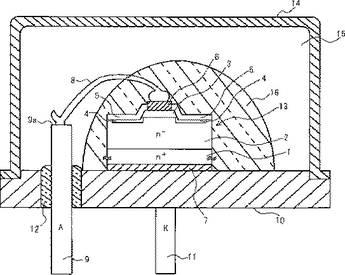

電力用半導体装置

【課題】 高温リーク電流が少なく、電位が固定されてプロセス外乱に強い高耐圧終端構造を有し、設計が容易な電力用半導体装置を提供する。

【解決手段】 第2導電型ベース領域2(Pアノード)の周囲を所定の距離をおいて囲み第1導電型ベース領域1の第1主面に形成された第1導電型ストッパ領域6と、第2導電型ベース領域2と第1導電型ストッパ領域6との間に有り、第1導電型ベース領域1の第1主面に同心円状に形成された第2導電型リング領域8とを備え、第2導電型リング領域8は、第2導電型ベース領域2と第1導電型ストッパ領域6とを電気的に接続する第2導電型コンタクト領域12と電気的に接続されている。従来電位を浮かしていたガードリング領域をベース領域からストッパ領域までを接続するコンタクト領域の存在により電位を固定しプロセス外乱に強い終端構造とする。コンタクト領域は、ポリシリコン層でも良い。

(もっと読む)

半導体装置とその製造方法

【課題】 トレンチを画定する側壁の一部にのみイオン注入領域が形成されている半導体装置を製造する。

【解決手段】 半導体層の表面に、側壁にイオン注入領域を形成するトレンチ部をエッチングする位置に幅広なトレンチエッチング用開口を有し、側壁にイオン注入領域を形成しないトレンチ部をエッチングする位置に幅狭なトレンチエッチング用開口を有するとともに、側壁にイオン注入領域を形成しないトレンチ部であって第1方向に伸びる第1トレンチ部とそれに交差する第2方向に伸びる第2トレンチ部が交差する位置を覆う関係にパターンニングされたマスク膜を形成する工程と、マスク膜の開口から異方性エッチングして半導体層に初期トレンチを形成する工程と、マスク膜の厚みによって、幅狭な初期トレンチ部では側壁が遮蔽され、幅広な初期トレンチ部では側壁が露出する角度からイオンを注入する工程を備えている製造方法。

(もっと読む)

高耐熱半導体装置

150℃以上の高温で使用するSiCなどのワイドギャップ半導体装置において、ワイドギャップ半導体素子の絶縁性を改善し、高耐電圧のワイドギャップ半導体装置を得るために、ワイドギャップ半導体素子の外面を合成高分子化合物で被覆する前記合成高分子化合物は、シロキサン(Si−O−Si結合体)による橋かけ構造を有する1種以上の有機珪素ポリマーAと、シロキサンによる線状連結構造を有する1種以上の有機珪素ポリマーBとをシロキサン結合により連結させた有機珪素ポリマーC同士を、付加反応により生成される共有結合で連結させて三次元の立体構造に形成している。  (もっと読む)

(もっと読む)

高耐熱合成高分子化合物及びこれで被覆した高耐電圧半導体装置

【課題】150℃以上の高温で使用するSiCなどのワイドギャップ半導体装置において、ワイドギャップ半導体素子の絶縁性を改善し、高耐電圧のワイドギャップ半導体装置を得る。

【解決手段】ワイドギャップ半導体素子の外面を、合成高分子化合物で被覆する。この合成高分子化合物は、シロキサン(Si−O−Si結合体)による橋かけ構造を有する1種以上の有機珪素ポリマーAとシロキサンによる線状連結構造を有する1種以上の有機珪素ポリマーBとをシロキサン結合により連結させた有機珪素ポリマーC同士を、付加反応により生成される共有結合で連結させて三次元の立体構造に形成している。この合成高分子化合物に高い熱伝導性を有する絶縁性セラミックスの微粒子を混合し、熱伝導率を高くしている。

(もっと読む)

基板上に作製された半導体電子デバイス

【課題】IV族元素半導体、III−V族化合物半導体、II−V族化合物半導体、IV族化合物半導体、有機半導体、金属結晶もしくはそれらの誘導体又はガラスから成る基板上に作製された高耐圧電子デバイスおよび耐環境電子デバイスを提供する。

【解決手段】本発明においては、ダイオードやトランジスタ等の電子デバイス中で電子又は正孔が走行する領域に、既存の半導体デバイスに用いられている材料から成る基板上に必要に応じて酸化モリブデンから成るバッファ層を介して形成された高純度の酸化モリブデンが用いられる。これにより、高耐圧特性及び高耐環境特性を有する安価な電子デバイスが実現できる。

(もっと読む)

ESD保護回路及びその製造方法

【課題】ラッチアップによる問題点を解決できるN−EDSCR素子を用いたESD保護回路及びその製造方法を提供すること。

【解決手段】半導体基板(110)と、半導体基板に形成された導電型ウェル(111)と、導電型ウェルと一部が重なるように形成された導電型ドリフト(117)と、導電型ウェル及び導電型ドリフト内に形成された第1導電型拡散層(113、114)と、導電型ウェル内で第1導電型拡散層から分離されて形成された第2導電型拡散層(115)、導電型ドリフト内で第1導電型拡散層に隣接して形成された第2導電型拡散層(116)と、第2導電型接続層(115)を覆うように形成された導電型ソース(122)と、導電型ソース及び導電型ドリフトの間の導電型ウェル上に形成された導電型電極(118)とを備える。

(もっと読む)

ゲートターンオフサイリスタ

メサ型のワイドギャップ半導体ゲートターンオフサイリスタでは、ゲートの耐電圧が低く、またリーク電流が大きい。高温時にはp型不純物のイオン化率が室温に比べ大幅に増大するため、ホールの注入量が増えるとともに少数キャリアのライフタイムも伸びるため、最大可制御電流が室温に比べ大幅に低下する。その点を解決するために、一方の面にカソード電極を有するn型SiCのカソードエミッタ層の上にp型ベース層を設け、p型ベース層の上に薄いn型ベース層を設ける。n型ベース層の中央部にメサ型のp型アノードエミッタ層を設け、n型ゲートコンタクト領域をp型アノードエミッタ層とn型ベース層の接合部から十分離して設けるとともに、n型低抵抗ゲート領域をn型ベース層内にアノードエミッタ層を取り囲むように設ける。  (もっと読む)

(もっと読む)

パワー半導体素子

【課題】通電電流を検出用コイルや検出用抵抗を用いずに検出する、小型、軽量、高速かつ低損失のパワー半導体素子回路を構成するのに適したパワー半導体素子を提供すること。

【解決手段】本発明のパワー半導体素子は、実質的に同じバンドギャップを有するワイドギャップ半導体材料からなるp型層34とn型層33,35とが少なくとも三層交互に、複数層積層されたバイポーラ型のパワー半導体素子である。複数層33,34,35のうち中間に挟まれた層34に電気的に接続され、この素子を通して流れる通電電流を制御する制御端子16Aを備える。複数層33,34,35のうち少なくとも一層、例えば層34に、通電電流に応じて光を発生する再結合センターが含まれ、この再結合センターで発生した光が外部へ放射されるようになっている。

(もっと読む)

窒化ガリウム結晶、ホモエピタキシャル窒化ガリウムを基材とするデバイス、及びその製造方法

約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板上に配設された1以上のエピタキシャル半導体層を含むデバイス。かかる電子デバイスは、発光ダイオード(LED)及びレーザーダイオード(LD)用途のような照明用途、並びにGaNを基材とするトランジスター、整流器、サイリスター及びカスコードスイッチなどのデバイスの形態を有し得る。また、約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板を形成し、該基板上に1以上の半導体層をホモエピタキシャルに形成する方法及び電子デバイスも提供される。  (もっと読む)

(もっと読む)

双方向サイリスタ

【課題】 転流時臨界電圧上昇率を大きくすることができる双方向サイリスタを提供する。

【解決手段】 半導体基板2は、上方から見た状態で、長方形に形成されている。半導体基板2の上面の表面領域には第3の半導体領域9と第4の半導体領域10とが形成されている。半導体基板2の下面の表面領域には、第6の半導体領域12が形成されている。第4の半導体領域と第6の半導体領域とは、半導体基板2の上方から見た状態で、重畳する重畳領域13を有している。また、第3の半導体領域9と第6の半導体領域12とは、半導体基板2の上方から見た状態で、半導体基板2の長手方向に並列に形成されている。

(もっと読む)

SiC半導体装置およびSiC半導体装置の製造方法

【課題】 n型SiCに対して良好なオーミック接触を得ることができるSiC半導体装置およびSiC半導体装置の製造方法を提供することを目的とする。

【解決手段】 第1の主面と該第1の主面に背向する第2の主面とを有するn+型SiC基板11と、第2の主面上に形成されたエピタキシャル層13と、エピタキシャル層13上に形成されると共に、エピタキシャル層13とオーミック接触した電極14とを有することを特徴とする。

(もっと読む)

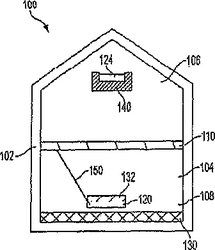

半導体装置及びその製造方法

【課題】 水分の浸入や汚染物質の侵入を防止し、長期間の使用に対する電気的信頼性を向上することができ、更に外部応力に対する半導体素子の損傷を防止し、半導体素子の電気的特性の変化を防止することができる半導体装置を提供する。

【解決手段】 樹脂封止型半導体装置において、支持基板1上にベベル端面を有する半導体素子4、例えばダイオードが取り付けられ、この半導体素子4上に中間接続導体6が取り付けられている。中間接続導体6の幅寸法(直径寸法)L3は半導体素子4の第2の主電極44の幅寸法(直径寸法)L2以上に設定されている。中間接続導体6の周縁部分を第2の主電極44の周縁部分よりも突出させたことによって、半導体素子4のベベル端面45上には、中間接続導体6の表面上の一部に渡る広範囲で保護樹脂10を形成することができる。

(もっと読む)

41 - 53 / 53

[ Back to top ]