Fターム[5F032CA23]の内容

Fターム[5F032CA23]の下位に属するFターム

高電圧用(高耐圧用) (419)

低電圧用(低耐圧用) (184)

Fターム[5F032CA23]に分類される特許

1 - 20 / 141

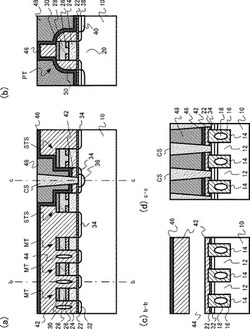

不揮発性半導体記憶装置の製造方法

【課題】選択ゲートトランジスタのゲート電極間の間隔の縮小を実現する不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板に、複数の第1の素子領域と、素子分離領域と、第2の素子領域を形成する。第1の素子領域上に、メモリセルゲート電極、2本の選択ゲート電極を形成し、第2の素子領域に周辺ゲート電極を形成する。第1の絶縁膜を形成し、周辺ゲート電極の側壁部上が開口される第1のレジストパターンを形成し、第1のエッチング処理を行い、側壁絶縁膜を形成する。第2のレジストパターンを形成し、第2のエッチング処理を行い、選択ゲート電極側壁部の第1の絶縁膜を除去する。第2の絶縁膜を堆積し、第3の絶縁膜を堆積する。2本の選択ゲート電極間上が開口される第3のレジストパターンを形成し、第3のエッチングおよび第4のエッチング処理を行い、コンタクトホールを形成する。

(もっと読む)

固体撮像装置、及び固体撮像装置の製造方法。

【課題】 本発明は、リセットトランジスタまたは増幅トランジスタと光電変換部とを分離するための素子分離領域で発生する暗電流によるノイズを低減するとともに、画素の微細化に有利な固体撮像装置を提供することを目的とする。

【解決手段】 第1画素領域には光電変換部、FD、及び転送トランジスタが画素を単位として行列状に配される。第2画素領域には増幅トランジスタ、及びリセットトランジスタが配される。第1画素領域には第1素子分離部が配され、第2画素領域には第2素子分離部が配される。第1素子分離部において絶縁膜が半導体基板内部に突出する量が、第2素子分離部において絶縁膜が半導体基板内部に突出する量に比べて小さい。配線が配された第1主面側とは反対の第2主面側から、光電変換部に光が入射する。

(もっと読む)

固体撮像装置及びその製造方法

【課題】素子を分離するための素子分離部による不具合の発生確率を低減する。

【解決手段】フォトダイオード310が内部に形成された半導体基板500と、素子分離部420とを備える。素子分離部420は、該素子分離部420の少なくとも一部が、半導体基板500に形成された溝410の内部に充填されるように形成される。素子分離部420は、溝410の内部の下方に形成されたシリコン酸化膜421と、溝410の内部の上方に形成されたシリコン酸化膜422とから構成される。シリコン酸化膜421の密度は、シリコン酸化膜422の密度より小さい。

(もっと読む)

固体撮像装置及びその製造方法

【課題】半導体基板中の複数の素子層間を有効に絶縁分離する。

【解決手段】裏面照射型の固体撮像装置において、受光部側と回路側との素子分離層を所定のマスクパターンを介した酸素イオン注入と、その後の熱処理によって半導体基板中に酸化膜を形成することにより実現する。例えばSOI基板のような支持基板部(絶縁体層)の上にシリコン層を設けた半導体基板に対し、シリコン基板(表面)側から光電変換素子層、素子分離層としての酸素イオン注入層、画素トランジスタ等の回路層を順次形成し、その後、シリコン層上に配線層を形成する。そして、裏面側の絶縁体層を除去することにより、シリコン層の受光部を露出させ、薄型のシリコン基板よりなる固体撮像装置を形成できる。

(もっと読む)

フラッシュメモリの製造方法

【課題】フラッシュメモリの製造工程において、エッチングによるSTI膜の膜減りを抑制することができる製造方法と、それを可能にするスプリットゲートタイプのMONOS型フラシュメモリ構造を提供する。

【解決手段】ワードゲートとコントロールゲートを含むスプリットゲートタイプのMONOS型フラシュメモリの製造方法であって、STIによって分離された半導体基板の不純物拡散層上に、酸化膜を挟んだワードゲートを形成する工程と、該STIとワードゲートが形成された半導体基板の表面全体に酸化膜、窒化膜、酸化膜の順に成膜されるONO層を形成する工程と、該ONO層の上にコントロールゲート用導電膜(10)を形成する工程と、該コントロールゲート用導電膜の表面全体にマスク用絶縁膜(26)を形成する工程と、を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体支持基板界面の品質を向上する。

【解決手段】半導体支持基板12、絶縁層14及びシリコン層16の三層構造を有するSOI基板10と、シリコン層16及び絶縁層14を貫通する穴部20と、穴部20の底部に形成された熱酸化膜22と、半導体支持基板12の熱酸化膜22下で、熱酸化膜22と接触する拡散層28と、を備える

(もっと読む)

半導体装置及びその製造方法

【課題】不純物の拡散によるナローチャネル効果の発生を抑制することを可能にする半導体装置を提供する。

【解決手段】半導体基体1と、半導体基体1に少なくとも一部が埋め込まれた、素子分離のための絶縁層2と、半導体基体1内に形成された不純物領域を含んで成る能動素子と、絶縁層2と半導体基体1との間に形成された、負の固定電荷を有する膜11とを含んで半導体装置を構成する。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】耐放射線性を有する絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】一部がチャネル領域をなすp型の半導体層11と、半導体層11の上部に活性領域21Bを定義する素子分離絶縁膜21と、チャネル領域にキャリア注入口を介してキャリアを注入するn型の第1主電極領域12と、チャネル領域から、キャリアを排出するキャリア排出口を有するn型の第2主電極領域13と、活性領域21Bの上に設けられたゲート絶縁膜22と、ゲート絶縁膜22の上に設けられ、第1主電極領域12と第2主電極領域13との間を流れるキャリアの流路に直交する主制御部、主制御部に交わる2本のガード部241,242を有してπ字型をなすゲート電極24と、第2主電極領域13のゲート幅方向の両端側に設けられたp型のリーク阻止領域61,62とを備える。

(もっと読む)

固体撮像装置およびその製造方法

【課題】本発明は、受光センサー部内のP型領域のホウ素がN型領域中へ拡散することを抑制して飽和電荷量の低下を抑えることを可能にする。

【解決手段】半導体基板11に形成されたN型領域13と、前記N型領域13上に形成された第1炭化シリコン層21と、前記炭化シリコン層21上に形成されたシリコン層22からなるP型領域14とで構成されたフォトダイオード15を有する。

(もっと読む)

固体撮像装置とその製造方法、及び電子機器

【課題】本発明は、感度ムラや、シェーディングが抑制された固体撮像装置を提供する。また、その固体撮像装置を用いた電子機器を提供する。

【解決手段】基板19と、基板19に形成された画素2と、隣接する画素間を分離する多段素子分離層31とを有して構成されている。画素2は、入射光に応じた信号電荷を生成、蓄積する受光部12と、基板19上に形成された画素電極14とを有して構成されている。多段素子分離層31は、複数段の不純物拡散層を有して構成されている。そして、受光部12を挟んで画素電極14に対向する領域の基板表面から深さ方向に形成された多段素子分離領域31は、基板19の光入射面から0.5μm〜1μmよりも深い領域において、受光部12から所定の距離W1だけ離して形成された下段素子分離層24,25を有している。

(もっと読む)

固体撮像装置とその製造方法、並びに半導体装置とその製造方法

【課題】SOI基板を用いずに半導体基板の薄膜化を可能にし、コスト低減を図った、固体撮像素子とその製造方法、並びに半導体装置とその製造方法を提供する。

【解決手段】半導体基板21に、光電変換素子と複数のMOSトランジスタとからなる画素が配列された撮像領域と、周辺回路と、半導体基板21の表面から厚み方向に半導体基板21より硬度が大きく且つ厚み方向の底面に、より硬度の大きい材料膜66を形成した柱状の終端検出部63とを有し、半導体基板が裏面からの化学機械研磨により前記終端検出部63が露出する位置まで薄膜化され、半導体基板21の表面にMOSトランジスタTr1が形成され、半導体基板21の裏面から入射光を取り込むようにして成る。

(もっと読む)

固体撮像装置とその製造方法、並びに半導体装置とその製造方法

【課題】SOI基板を用いずに半導体基板の薄膜化を可能にし、コスト低減を図った、固体撮像素子とその製造方法、並びに半導体装置とその製造方法を提供する。

【解決手段】半導体基板21に、光電変換素子PDと複数のMOSトランジスタTr1とからなる画素が配列された撮像領域と、周辺回路と、撮像領域を挟む両外側に形成され、半導体基板の表面から厚み方向に半導体基板より硬度が大きい柱状の終端検出部63とを有し、半導体基板が裏面からの化学機械研磨により終端検出部63が露出する位置まで薄膜化され、半導体基板の表面にMOSトランジスタが形成され、半導体基板の裏面から入射光を取り込むようにして成る。

(もっと読む)

光電変換装置、撮像システム、及び光電変換装置の製造方法

【課題】画素の寸法を微細化した場合でも、画素において、光電変換部の受光面積を確保しながら、寄生MOSトランジスタが動作することを防止する。

【解決手段】光電変換装置は、光電変換部と前記光電変換部により蓄積された信号を読み出すためのトランジスタとをそれぞれ含む複数の画素が配される撮像領域を有した半導体基板を備え、前記撮像領域には、隣接する前記画素の間で複数の前記光電変換部を電気的に分離する第1の素子分離部と、隣接する前記画素の間で複数の前記トランジスタを電気的に分離する第2の素子分離部とが配され、前記第1の素子分離部は、前記第2の素子分離部より平面方向の幅が狭くかつ深さが浅い部分を有する。

(もっと読む)

半導体装置

【課題】素子分離領域での段差の形成を抑制して高い信頼性を短い工程で得ることができる半導体装置を提供する。

【解決手段】素子分離絶縁膜313の中央部から第1の素子活性領域側に段差が形成されている。素子分離絶縁膜313の前記第1の素子活性領域側の端部にくびれ部が形成されている。前記段差の前記中央部側の端部と前記くびれ部との平面視での距離をx、素子分離絶縁膜313の頂部の半導体基板312表面からの高さをy、前記くびれ部と前記段差の前記中央部側の端部とを結ぶ線分の半導体基板312表面からの傾きをαとしたとき、xの値が数式「y/sinα」の値よりも大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性が高く、かつ微細化可能な大電力用の半導体装置およびその製造方法を提供する。

【解決手段】基板10と、基板10上に配置された窒化物系化合物半導体層12、窒化物系化合物半導体層12に配置され、アルミニウム窒化ガリウム層(AlxGa1-xN)(0.1≦x≦1)14からなる活性領域と、活性領域を互いに素子分離する素子分離領域24と、素子分離領域24によって囲まれた活性領域上に配置されたゲート電極20、ソース電極18およびドレイン電極26と、ゲート電極20下の一部をエッチングした溝部28a,28bとを備える半導体装置およびその製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】転位による結晶欠陥不良を防止できるようにする。

【解決手段】半導体基板2に素子分離溝3を形成し、当該素子分離溝3の内面に沿って上部が部分的に開口するO3−TEOS膜4aを形成し、当該O3−TEOS膜4a上にポリシラザン膜4bを形成する。

(もっと読む)

半導体装置の製造方法

【課題】固定電荷等の影響がなく電気的特性の優れた良質なSOD単層膜を備えた、微細LSIプロセス用の素子分離領域を備えた半導体装置を提供する。

【解決手段】半導体基板内のトレンチの内壁上に酸化膜およびライナー膜を形成する膜形成工程と、トレンチ内にSOD膜を埋設して熱処理を行う工程と、SOD膜と接するライナー膜の一部を除去してSOD膜の一部を露出させる除去工程と、SOD膜に対して熱処理を行う熱処理工程と、トレンチ内に絶縁膜を埋設させることにより素子分離領域を形成する埋設工程と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】化学機械研磨におけるストッパー膜の削れが小さく、半導体装置の製造における歩留まりを向上させる。

【解決手段】本発明の半導体装置の製造方法は、シリコン基板11を覆うようにアモルファスシリコン膜14を形成する工程と、アモルファスシリコン膜14およびシリコン基板11の一部を除去して、シリコン基板11の表面に素子分離溝15を形成する工程と、素子分離溝15を埋め込むようにアモルファスシリコン膜14上に絶縁膜16を形成する工程と、アモルファスシリコン膜14をストッパとして絶縁膜16を化学機械研磨し、絶縁膜16の上面を平坦化する工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】周辺回路部のLV系トランジスタでの結晶欠陥の発生を抑制しつつ、HV系トランジスタでの反転リークなどの増加を抑制できるようにするNAND型フラッシュメモリの半導体装置と製造方法を提供する。

【解決手段】LV系トランジスタ領域103のSTI304の上面を、EB加工により、セル領域104のSTI404の上面と同時にエッチングする。こうして、HV系トランジスタ領域102のSTI204の上面の高さはそのままに、LV系トランジスタ領域103のSTI304の上面のみを、第1の電極膜12の上面の高さよりも下げる。上面の高さを下げた分だけ、LV系トランジスタ領域103のSTI304での素子分離用絶縁膜の膜厚を削減して、塗布膜の収縮応力を緩和させる。

(もっと読む)

半導体装置

【課題】パッケージ工程における応力を緩和し、パッケージ工程前後での特性変化を抑制する半導体装置を提供する。

【解決手段】半導体装置100を構成する素子のうち特に精度が要求されパッケージからの応力を受けたくない素子領域3を応力緩和のための緩衝領域8で囲むことにより、パッケージ工程で発生する引っ張り応力あるいは圧縮応力の影響を抑制し、パッケージ工程前後での特性の変化を低減する。

(もっと読む)

1 - 20 / 141

[ Back to top ]