Fターム[5F032DA14]の内容

Fターム[5F032DA14]に分類される特許

1 - 17 / 17

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

半導体装置

【課題】 素子特性の劣化を抑制する。

【解決手段】 実施形態による半導体装置は、トランジスタ領域を有する半導体装置であって、トランジスタ領域は、基板上に形成された半導体領域と、半導体領域に隣接する素子分離領域と、ラテラルエピタキシャル層を備え、半導体領域上及び半導体領域と素子分離領域との間で横方向に成長するエピタキシャル層と、を具備する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】工程増を最小限とした簡便な手法で、素子形成領域における化合物半導体と同時に、しかもその結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上の素子分離領域に初期層3を選択的に形成し、初期層3上を含むSi基板1上の全面に化合物半導体の積層構造4を形成して、積層構造4は、素子分離領域では初期層3と共に素子分離構造4Bとなり、素子形成領域ではソース電極5、ドレイン電極6及びゲート電極7が形成される素子形成層4Aとなる。

(もっと読む)

固体撮像装置、及びその製造方法

【課題】光照射面側の素子分離を強化して、混色を低減させ、感度向上、素子分離部の暗電流低減できる固体撮像装置、及びその製造方法を提供すること。

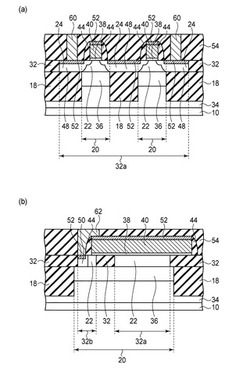

【解決手段】n型の半導体基板30表面内に形成された前記n型の拡散層32を含み、前記半導体基板の裏面側から表面側に向かって照射された光により前記半導体基板内で生成された電子を蓄積する電荷蓄積部PDと、前記電荷蓄積部を挟み、前記半導体基板表面からこの半導体基板内に達するように形成されたp型の第1、第2拡散層(36)と、前記電荷蓄積部を電気的に分離し、前記半導体基板の前記裏面側が開口されるよう形成された第1、第2トレンチ55に埋め込まれたp型のa−アモルファスシリコン化合物(p型a−SiC)と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】バルク領域に形成される素子の不良を低減できるようにした半導体装置の製造方法を提供する。

【解決手段】バルク領域のSi基板1上にアモルファス構造又は多結晶構造のSi層9を形成すると共に、SOI領域をSi層9下から露出させる工程と、Si層9を形成した後で、SOI領域及びバルク領域のSi基板1上にSiGe層11とSi層13とを順次、エピタキシャル成長法で形成する工程と、Si層13とSiGe層11とを部分的にエッチングして、SOI領域のSiGe層11側面を露出させる溝を形成する工程と、この溝を介してSiGe層11をフッ硝酸溶液でウェットエッチングすることによって、SOI領域のSi基板1とSi層13との間に空洞部を形成する工程と、空洞部内にSiO2膜を形成する工程と、を含む。

(もっと読む)

SOIウェーハの製造方法ならびにSOIウェーハ

【課題】部分SOIウェーハ、埋め込み酸化膜段差パターン付SOIウェーハ、埋め込み酸化膜段差パターン付2重SOIウェーハ、及びその製造方法を提供する。

【解決手段】SOIウェーハ上に保護膜を形成する工程と、引き続き保護膜の一部分をエッチングによって除去して開口部を設ける工程と、引き続きウェーハを熱処理炉内に導入して埋め込み酸化膜厚を減ずる熱処理工程を含む部分SOIウェーハおよび埋め込み酸膜化段差パターン付SOIウェーハの製造方法であり、前記埋め込み酸化膜厚を減ずる熱処理雰囲気には塩素を含有する気体ならびに酸素が含まれ、さらに前記熱処理雰囲気は、当該熱処理温度においてウェーハ表面に表面酸化膜が成長する範囲の酸素分圧を有することを特徴とする部分SOIウェーハおよび埋め込み酸化膜段差パターン付SOIウェーハの製造方法。

(もっと読む)

デュアル・シャロー・トレンチ分離及び低いベース抵抗を有するバイポーラ・トランジスタ

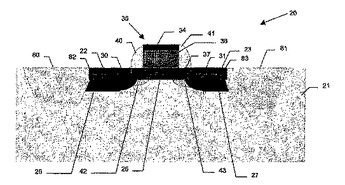

【課題】 トランジスタの性能を改善するために、ベース・コレクタ容量(Ccb)及びベース抵抗(Rb)の寄生成分が著しく低減されたバイポーラ・トランジスタを提供すること。

【解決手段】 ベース・コレクタ容量Ccb及びベース抵抗Rbの寄生成分を減少するための、デュアル・シャロー・トレンチ分離を有する改善されたバイポーラ・トランジスタが提供される。この構造体は、少なくとも1対の隣接する第1のシャロー・トレンチ分離(STI)領域が内部に配置された半導体基板を含む。隣接する第1のSTI領域の対は、基板内に活性領域を定める。この構造体は、半導体基板の活性領域内に配置されたコレクタ、活性領域内の半導体基板の表面の上に配置されたベース層、及びベース層上に配置された隆起型外因性ベースをも含む。本発明によると、隆起型外因性ベースは、ベース層の部分への開口部を有する。エミッタは、この開口部内に配置され、パターン形成された隆起型外因性ベースの部分上に延びており、かつ、隆起型外因性ベースから離間配置され、これから分離される。さらに、第1のSTI領域に加えて、第1のシャロー・トレンチ分離領域の各対からコレクタに向けて内方に延びる第2のシャロー・トレンチ分離(STI)領域が、半導体基板内に存在する。第2のSTI領域は、傾斜した内部側壁面を有する。幾つかの実施形態において、ベースは完全に単結晶である。

(もっと読む)

表面層と基板とを接続するゾーンを備える部分的SOI構造を製造する方法

本発明は、表面層(20’)と、少なくとも1つの埋込み層(36、46)と、支持体(30)とを備える半導体構造を製造する方法に関し、この方法は、第1の支持体上に、第1の材料でパターン(23)を形成するステップと、前記パターン間及び前記パターン上に半導体層を形成するステップと、前記半導体層と第2の支持体(30)とを組み合わせるステップとを備える。 (もっと読む)

半導体基板の製造方法及び半導体装置の製造方法、半導体装置

【課題】トランジスタの特性に悪影響を及ぼすことを抑えることができる半導体基板の製造方法及び半導体装置の製造方法、半導体装置を提供する。

【解決手段】半導体基板41の製造方法は、まず、SOI素子形成領域13に第1支持体穴21及び第2支持体穴22を形成するとともに、SOI素子形成領域13と素子分離層12との境界に沿った全周に境界溝14を形成する。次に、シリコン基板11上の全体に支持体形成層27を形成する。そのあと、支持体26とともに、素子分離層12上の多結晶エピタキシャル膜18の端部18aが露出しないように、支持体形成層27の一部を残してエッチングする。これにより、端部18aが側壁膜27aで覆われたままの状態を維持することができ、第1シリコンゲルマニウム層15aをエッチングで除去する際に、端部18aとエッチング液とが接触することが抑えられる。

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法、半導体装置

【課題】半導体基板の大きさ(面積)を小さく製造することができる半導体基板の製造方法及び半導体装置の製造方法、半導体装置を提供する。

【解決手段】半導体基板41の製造方法は、まず、第1素子分離層12とSOI素子形成領域13との境界上に第1支持体穴21及び第2支持体穴22を形成する。次に、支持体穴21,22の中及びシリコン層16上を覆うように支持体形成層27を形成したあと、支持体26を形成する。第1支持体穴21及び第2支持体穴22を境界上に形成することにより、SOI素子形成領域13の中に占める支持体穴21,22の面積を小さくすることが可能となる。

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】SOI構造を有するSBSI法によるMOSFETに、寄生チャンネル抑制イオン注入を効率的に行うことのできる半導体基板の製造方法および半導体装置の製造方法を提供すること。

【解決手段】レジスト18と露出面を備えた素子領域8との距離drが、埋め込み絶縁層17の底面からレジスト18の表面までの高さHrと埋め込み絶縁層17の厚さHsとイオン注入の角度θとで決められる。したがって、イオン注入されるイオンが、レジスト18に邪魔されることなく、シリコン層13と埋め込み絶縁層17の端部の一部が露出した露出面に到達し、寄生チャンネル抑制イオン注入を効率的に行うことができる。

(もっと読む)

半導体装置の製造方法

【課題】 選択エピタキシャル成長を用いることなく、半導体基板上の一部の領域にSOI構造を安価に形成する。

【解決手段】 エピタキシャル成長を行うことにより、半導体基板1上のSOI構造形成領域R2に第1単結晶半導体層3aおよび第2単結晶半導体層4aを順次形成するとともに、SOI構造形成領域R2の周囲および非露光領域R1に形成された素子分離酸化膜2上に第1アモルファス半導体層3bおよび第2アモルファス半導体層4bを順次形成した後、レジストパターンR1をマスクとして第2単結晶半導体層4a、第2アモルファス半導体層4b、第1単結晶半導体層3aおよび第1アモルファス半導体層3bをエッチングすることにより、SOI構造形成領域R2の半導体基板1の一部を露出させる開口部7を形成するとともに、素子分離酸化膜2上の第1アモルファス半導体層3bおよび第2アモルファス半導体層4bを除去する。

(もっと読む)

超格子を間に有するシャロー・トレンチ・アイソレーション(STI)領域を含む半導体デバイス、及びその製造方法

半導体デバイスは、半導体基板と、基板内の複数のシャロー・トレンチ・アイソレーション(STI)領域とを含んでいる。より具体的には、STI領域の少なくとも一部はディボットを含んでいる。半導体デバイスは更に、隣接し合うSTI領域間それぞれの超格子と、ディボット内それぞれの非単結晶の梁部とを含んでいる。

(もっと読む)

(もっと読む)

半導体デバイスの製造方法および該製造方法により得られた半導体デバイス

本発明は、半導体素子10の製造方法に関し、半導体デバイス10は、基板11と、少なくとも一つの半導体素子1が形成された半導体本体12とを具え、基板11には半導体層2が形成され、シリコンとゲルマニウムとの混晶を具えてなる半導体層2はシリコン−ゲルマニウム層2と称され、基板11に近接する下面と、基板11から遠く離れた上面とを有し、シリコン−ゲルマニウム層2はその一表面で酸化処理を受ける一方、シリコン−ゲルマニウム層2の他の表面は阻止層3により酸化処理から保護される。本発明によれば、阻止層3がシリコン−ゲルマニウム層2の上面に形成され、キャビティ5が半導体本体の中でシリコン−ゲルマニウム層2の下方に形成され、そしてシリコン−ゲルマニウム層2の下面がキャビティ5を介して酸化処理を受ける。この方法によれば、酸化処理後のシリコン−ゲルマニウム層2の表面は、粗面化および/またはパイルアップに悩まされることのないデバイス10を得ることができる。これは例えば、シリコン−ゲルマニウム層2の上または内部に、格別なMOSFETを優れた特性および多産で製造することを可能にする。  (もっと読む)

(もっと読む)

バイポーラートランジスターの作製方法

本発明は、標準的な浅いトレンチ分離作製方法を適用してバイポーラートランジスターを作製するための方法を提供するものであり、第一トレンチ(5,50)の中に縦型バイポーラートランジスター(29)又は横型バイポーラートランジスター(49)と、第二トレンチ(7,70)の中に浅いトレンチ分離領域(27,270)を同時に形成する。更に本作製方法は、第一トレンチ(5,50)の中に縦型バイポーラートランジスター(27)、第三トレンチの中に横型バイポーラートランジスター(49)、及び第二トレンチ(7,70)の中に浅いトレンチ分離領域(27,270)を同時に形成することもある。  (もっと読む)

(もっと読む)

半導体基板及びその製造方法

【課題】小さい寄生容量及び高いキャリヤ移動度を有する半導体基板を提供する。

【解決手段】Si基板10と、Si基板10上に形成された所定幅のSiO2層12と、両側にそれぞれ第1の端部40a及び第2の端部40bを有し、第1の端部40a及び第2の端部40bから側方向のエピタキシャル成長によって形成され、SiO2層12を覆うSiGe層40と、SiO2層12に対応してSiGe層40上にエピタキシャル成長によって形成され、Siの格子変形が誘導されたストレインSi層50と、を備える半導体基板である。

(もっと読む)

特徴の異なる結晶性半導体領域を有する基板の形成技術

第1結晶性半導体領域104a内に誘電領域111を形成することによって、単一基板上に異なるタイプの結晶性半導体領域が与えられる。その後、この誘電領域111上には、第2結晶領域152aがウェハ接合技術によって位置決めされる。好ましい実施形態では、誘電領域とともに、第1結晶領域にアイソレーション構造が形成されてもよい。特に、結晶方向の異なる結晶性半導体領域が形成されてもよく、高度なフレキシビリティと、現在利用されているCMOSプロセスとの互換性が維持される。  (もっと読む)

(もっと読む)

1 - 17 / 17

[ Back to top ]