Fターム[5F033GG02]の内容

半導体集積回路装置の内部配線 (234,551) | 基板材料(シリコンを除く) (2,930) | 化合物半導体 (913) | III−V族 (485)

Fターム[5F033GG02]に分類される特許

481 - 485 / 485

半導体製造プロセスの過程で導電面を不動態化するための方法

半導体ウェハの製造プロセスが開示されている。メタル配線の表面に発生するデンドライトや電気分解反応を抑止するため、半導体ウェハに対して溶液が適用される。その溶液は、CMP処理の際又はCMP洗浄後処理の際に適用される。その溶液は、界面活性剤及び防食剤を含む。一実施形態では、その溶液中に含まれる界面活性剤の濃度が約1重量パーセント未満に設定され、防食剤の濃度が約1重量パーセント未満に設定される。また、その溶液は、溶媒及び共溶媒を含むこともできる。別の実施形態では、その溶液が、界面活性剤及び防食剤を含まず、溶媒及び共溶媒を含む。一実施形態では、CMP処理及びCMP洗浄後処理を、約1μm未満の波長を持つ光の存在下で実施できる。  (もっと読む)

(もっと読む)

多層微細配線構造およびその作製方法

【課題】 高速情報処理用デジタル集積回路チップ内およびそのチップを搭載するためのパッケージ、モジュール、ボードなどの実装系内における多層配線の作製方法に関する新しい多層微細配線構造およびその作製方法を提案する。

【解決手段】 高解像感光性ポリイミドを絶縁層として、銅、銀、金、アルミニウム、パラジウム、ニオブなどの金属を配線層として用いて、ストリップライン、マイクロストリップライン、同軸ラインなどの伝送線路構造を有する多層微細配線構造を実現するため、広い周波数帯域について、インピーダンスが一定に制御され、デジタル高速信号伝送に適する線路を実現することができる。高解像特性を有する感光性ポリイミドを絶縁層として用いることにより、絶縁層へのビア穴加工がリソグラフィ工程のみで達成され、また、金属配線層をリフトオフ法によりパターン形成することにより、従来の多層配線技術に比べて、高密度の配線構造が実現でき、大幅に工程が簡略化される。

(もっと読む)

半導体装置とその製造方法およびモノリシックマイクロ波集積回路

【課題】 強度低下や寸法増大を抑えながら、バイアホールの接地インダクタンスを低減できる半導体装置とその製造方法およびMMICを提供する。

【解決手段】 このマイクロ波帯用増幅器GaAsMMICは、その接地電極8が、3個のバイアホール11からなるバイアホール群12を有し、この3個のバイアホール11は、その内側に充填されたメッキ金属10aが近接されて形成され、その相互作用によって高周波的な電磁界結合が発生して、接地インダクタンスが低減された。

(もっと読む)

多層配線基板及び半導体装置

【課題】エミッタ配線からバイアホール、サーマルビアを介して多層配線基板下面につながる放熱経路の熱抵抗を低減し、半導体装置全体の熱抵抗を低減すること。

【解決手段】厚さ方向に貫通孔4を有する多層配線基板3において、多層配線基板3に実装される半導体基板1がその厚さ方向に貫通孔5を有し、かつ、多層配線基板3及び半導体基板1の厚さ方向と直交する平面内において、半導体基板の貫通孔5の占める領域全体が多層配線基板内貫通孔4の占める領域に含まれている多層配線基板。

(もっと読む)

フリップチップ用高性能シリコンコンタクト

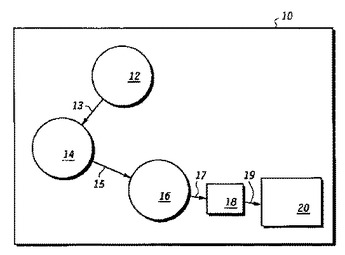

本発明においては、前面(14)と背面(16)とを備える半導体基板(12)であって、基板を(12)通って前面(14)と背面(16)との間を延びる孔(18、20、22)を備える半導体基板(12)を用意する。孔(18、20、22)は、部分的に、内壁部分によって規定され、外側導電性シースを形成する。導電性材料(54)を、内壁部分の少なくとも一部に隣接して形成する。その後に誘電体材料層(56)を、孔内部に、導電性材料上であってそのラジアル方向内側に形成する。次に第2の導電性材料(60)を、孔内部に、誘電体材料層(56)上であってそのラジアル方向内側に形成する。後者の導電性材料は、内側導電性コアキシャル線要素を構成する。 (もっと読む)

481 - 485 / 485

[ Back to top ]