Fターム[5F033QQ77]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 熱処理 (5,181) | 熱酸化 (553) | 選択酸化 (17)

Fターム[5F033QQ77]に分類される特許

1 - 17 / 17

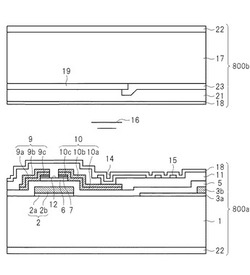

表示装置及びその製造方法

【課題】ソース・ドレイン電極に、剥離やストレスマイグレーションによるボイドが発生するのを抑制する。

【解決手段】複数の薄膜トランジスタが配列された基板を有する表示装置であって、薄膜トランジスタは、半導体層6と、半導体層6上に形成されるコンタクト層7と、コンタクト層7上に形成されるソース電極10及びドレイン電極9とを有し、ソース電極10およびドレイン電極9は、コンタクト層7の上側に形成される第1の導電層9a,10aと、第1の導電層9a,10aの上側に形成される第2の導電層9b,10bとを有し、第2導電層9b,10bは、第1添加元素と、銅とを含有する銅合金層であり、前記第1添加元素は、ジルコニウム、チタン、銀、インジウム、金、錫、クロム、ケイ素から選ばれた少なくとも1種類の元素である、ことを特徴とする表示装置。

(もっと読む)

半導体装置の製造方法

【課題】層間絶縁層のコンタクトホールに埋め込まれたコンタクトプラグを介して上層側の金属配線層と下層側の金属配線層とを電気的に接続する際の接続抵抗を低減する。

【解決手段】第2の層間絶縁層の上に少なくともコンタクトホールを形成する位置に開口部を有するレジスト層を形成する工程S1−4と、レジスト層を用いて第2の層間絶縁層をパターニングすることによって、第2の層間絶縁層を貫通するコンタクトホールを形成する工程S1−5と、コンタクトホールの内部に付着したポリマーを含む残渣をスチーム酸化によって除去する工程S1−7とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】3Dピラートランジスタにおいて、ゲートコンタクトとシリコン基板との間のショートを抑制した半導体装置及びその製造方法を得るという課題があった。

【解決手段】半導体からなる基板1と、一面1aから突出され、前記半導体からなる第1の突出部2と、一面1aに設けられた溝部1cに充填された第1の絶縁体3と、第1の突出部2に隣接して一面3aから突出され、第1の絶縁体3からなる第2の突出部4と、第1の突出部2の側面を覆うゲート絶縁膜5と、ゲート絶縁膜5を覆うゲート電極6と、第1の突出部2に設けられた上部拡散層13と、下部拡散層14と、第2の突出部4の側面を覆うとともにゲート電極6に接続された連結電極60と、第1の突出部2及び第2の突出部4を覆う層間絶縁膜と、前記層間絶縁膜を貫通して連結電極60に接するゲートコンタクト10と、を有する半導体装置及びその製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

MOS型半導体装置

【目的】耐放射線特性の改善と高耐圧化が図れるMOS型半導体装置を提供する。

【解決手段】LOCOS膜18上に窒化膜18を形成し、窒化膜14上にPBSG膜10を形成する。窒化膜14の屈折率を2.0〜2.1とし、膜厚を0.1μm〜0.5μmとすることで半絶縁性薄膜にする。γ線でLOCOS膜18内に発生した電子―正孔対のうち移動度が小さい正孔31を窒化膜14を通してソース電極12に逃がし、LOCOS膜18にできる正の固定電荷33の蓄積量を抑制する。このように3層構造とすることで耐放射線特性の改善と高耐圧化が図れる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造工程での乾燥処理におけるパターンの倒壊を抑制可能とする、半導体装置の製造方法を提供すること。

【解決手段】シリコン系材料を用いて構成されるシリコン系部材層を形成し、前記シリコン系部材層の上に、金属材料を用いて構成される金属部材層を形成し、前記金属部材層をパターニングし、パターニングされた前記金属部材層の表面に側壁膜を形成し、前記シリコン系部材層をパターニングすることにより、前記シリコン系部材層と、前記側壁膜で表面を覆われた前記金属部材層と、を備える構造体を形成し、薬液を用いて前記構造体の表面を洗浄し、前記構造体の表面から前記薬液を除去し、前記構造体の表面に撥水性保護膜を形成し、前記撥水性保護膜が形成された前記構造体の表面をリンスし、前記構造体の表面を乾燥させる、工程を含む。

(もっと読む)

半導体装置

【課題】飽和動作時のゲート電圧が高電圧であっても素子が破壊しにくい高耐圧MOSトランジスタを提供する。

【解決手段】Nチャネル型の高耐圧MOSトランジスタの低濃度不純物領域上のLOCOSプロセスなどで形成される酸化膜と、ドレイン領域となる高濃度不純物領域との境界部の上をドレイン領域と接続している金属配線で覆うことで、境界部の低濃度不純物領域と高濃度不純物領域の接続部の電界集中を、金属配線から半導体基板に向かう電界で緩和させることができ、NMOSトランジスタの飽和動作の高ゲート電圧時の衝突電離を抑制し、素子破壊の抑制と高耐圧化を図ることが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】金属配線部から、金属が層間絶縁膜に拡散することを抑制するためのシリコン窒化膜等から窒素や水素が拡散することによる影響を軽減した信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2上に形成された半導体素子部100と、半導体素子部100の上部に形成された銅配線225と、半導体素子部100と銅配線225とを電気的に接続するプラグ電極216と、このプラグ電極216が酸化しないようにするシリコン酸化膜223と、半導体素子部100の上部に形成されたアモルファスシリコン膜217と、アモルファスシリコン膜217の上部に形成されたCu拡散防止膜218と、を有した半導体装置1とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置のリセスLOCOS構造の面積縮小及びリーク電流の抑制を図る。

【解決手段】LOCOS膜を形成する領域のシリコン基板50表面を異方性エッチングにより掘り下げて凹部を形成する。異方性エッチングにより形成された凹部に等方性エッチングを施し、凹部58bの側面と底面とに挟まれるコーナー60bを丸める。その後に、凹部58bのシリコン基板50を選択酸化して凹部58bを埋めるLOCOS膜を形成する。凹部58bのコーナー60bを丸めることで、当該コーナー60bの外側のシリコン基板50におけるLOCOS膜によるストレスの集中が緩和され、シリコン基板50の欠陥の発生が抑制される。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】 半導体素子の表面に金属電極を形成する場合、バリア膜を形成することで、半導体素子の表面にめっき法を用いて厚い金属電極を形成することができる。しかし、バリア膜は導電性があるため、金属電極間に存在するバリア膜は絶縁する必要がある。

【解決方法】 層間絶縁膜12が形成された半導体素子14の表面に導電性のあるバリア膜10を形成する。バリア膜10の表面に金属電極5を形成した後に、半導体素子14を熱酸化する。金属電極4が形成されていない領域のバリア膜10cは酸化され絶縁性を示す。これにより金属電極同士は絶縁される。また金属電極5が形成されている領域のバリア膜10a,10bは金属電極5がマスクの役割を果し、酸化されず導電性を保つ。これにより金属電極5と半導体素子14との導通は確保される。

その後、金属電極5表面の酸化膜22を除去することで、金属電極5の導通も確保される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】導電性バンプと金属パッドとの接触界面における好適な機械強度を有する半導体装置を、より簡素なプロセスにて製造することのできる半導体装置の製造方法及びその製法にて製造された半導体装置を提供する。

【解決手段】半導体装置を製造するにあたり、金属パッド形成工程として、半導体基板10の表面RSのうちの金属パッド30の周縁部が形成される部分にLOCOS酸化膜12を形成する第1層間膜形成工程と、LOCOS酸化膜12の表面を含む半導体基板10の表面RSに所定の膜厚にて金属膜を形成する金属膜形成工程と、金属膜の平面視形状を所定の形状に整形する整形工程とを実行する。こうした金属パッド形成工程を通じて、LOCOS酸化膜12の表面及び半導体基板10の表面RSの側面断面視形状を、金属パッド30の側面断面視形状に転写する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体基板の深層にまで至る深い孔を有する半導体装置であれ、通常の半導体プロセスを通じて製造することのできる半導体装置の製造方法及びこの製法によって製造された半導体装置を提供する。

【解決手段】当該半導体装置の製造方法は、半導体基板10に半導体素子を作製する素子作製工程と、当該半導体装置の構成要素として、所望の位置で開口するLOCOS酸化膜12を半導体基板12の表面RSに形成する層間膜形成工程とを備える。孔形成工程では、層間膜形成工程にて形成されたLOCOS酸化膜12をエッチングマスクとして利用して、半導体基板10の表面RSから該半導体基板10の深層に至る孔11aを形成する孔形成工程を備える。

(もっと読む)

半導体装置の製造方法、半導体記憶装置の製造方法

【課題】シリサイド層を有する半導体装置の製造プロセスを簡易化すること。

【解決手段】本発明に係る半導体装置の製造方法は、(A)基板1上にポリメタルゲート電極3を形成する工程と、(B)全面に層間絶縁膜7を堆積する工程と、(C)ポリメタルゲート電極3及び基板1表面のそれぞれに届く第1及び第2コンタクトホールC3,C2を同時に形成する工程と、(D)第1コンタクトホールC3の底部において、露出している第1金属膜3bの表面をシリサイド化することにより第1シリサイド10を形成する工程と、(E)全面に第2金属膜20を堆積する工程と、(F)第2コンタクトホールC2の底部において、第2金属膜20と基板1表面との間のシリサイド反応により第2シリサイド22を形成する工程と、(G)未反応の第2金属膜20を除去する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】段差部に近接した領域に導電体パターン(例えばゲート電極)が形成される場合に、導電体パターンの寸法精度を高くすることができる半導体装置の製造方法を提供する。

【解決手段】本半導体装置の製造方法は、素子分離膜2上、絶縁膜12上、及びゲート絶縁膜3b〜3d上に導電膜4を形成する工程と、絶縁膜12とゲート絶縁膜3bの間に位置する導電膜4に開口部4eを形成する工程と、導電膜4上及び開口部4e内にフォトレジスト膜51を形成し、その後露光及び現像することにより、ゲート絶縁膜3bから3dそれぞれの上方に位置するレジストパターン51b〜51d、及び絶縁膜12の上方に位置するレジストパターン51aを形成する工程と、レジストパターン51a〜51dをマスクとして導電膜4をエッチングすることにより、ゲート電極4b〜4d及び上部導電膜4aを形成する工程とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】 コンタクトパッドを形成する半導体装置の製造方法において、隣接する半導体素子間のショートを防止する。

【解決手段】 シリコン基板11上に、それぞれが金属層15を含むゲート電極17とゲート電極17を覆うゲート側壁絶縁膜20とを有する複数のゲート電極構造体を形成する工程と、ゲート電極構造体を覆って全面にポリシリコン膜を堆積する工程と、ポリシリコン膜をパターニングし、隣接する2つのゲート電極構造体の間でシリコン基板11に接続するコンタクトパッド22を形成する工程(図3(g))と、ゲート側壁絶縁膜のくぼみ21に残留するポリシリコン24を酸化させて酸化シリコン25に形成する工程(図3(h))とをこの順に有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】工程数を増やさなくても寸法精度が高くなり、かつトランジスタを小型化できる半導体装置を提供する。

【解決手段】半導体基板1と、半導体基板1に形成されたLOCOS酸化膜2と、LOCOS酸化膜2上に形成された絶縁膜8と、絶縁膜8及びLOCOS酸化膜2に形成された接続孔8bと、接続孔8bの下に位置する半導体基板1に形成された不純物領域7bと、絶縁膜8上に形成され、接続孔8bを介して不純物領域7bに接続する配線9bとを具備する。不純物領域7bをソース又はドレインとすると、LOCOS酸化膜2の相互間に形成されたゲート電極4の周辺部を、LOCOS酸化膜2上に位置させることができるため、チャネル領域10cの寸法の誤差を、LOCOS酸化膜2の寸法誤差のみに起因させることができる。従って、チャネル領域10cの寸法精度を高くすることができる。

(もっと読む)

半導体装置の製造方法

【課題】LOCOS法により形成された酸化シリコン膜上のポリシリコン膜に接続されるコンタクトホールを作製する際に、コンタクトホールがポリシリコン膜を突き抜けないようにする。

【解決手段】熱酸化法を用いて基板71上に酸化シリコン膜74を形成するとき、各窒化シリコン膜11は幅の狭い帯状であるため、その幅方向両端側から基板71の表面へ酸素が供給されて膜74が形成され、膜74の膜厚Daは膜厚Dbに比べて薄くなる。ポリシリコン膜76上のBPSG膜77の膜厚Hcは、不純物領域75上のBPSG膜77の膜厚Haに比べて薄くなるが、膜厚Daを十分に薄くすれば、各膜厚Hc,Haの差を小さくできる。そのため、膜厚Daを十分に薄くすれば、各コンタクトホール78,79を同時に形成するとき、ホール78が領域75と確実に接続されるようにエッチング条件を設定しても、ホール79の底面79aが膜76を突き抜けるのを防止できる。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置が小型化・高密度化された場合であっても、ボンディング時の不良発生を抑制した高信頼性の半導体装置及びその製造方法を提供する。

【解決手段】 本発明の半導体装置1は、シリコン基板2上に酸化シリコンからなる下地絶縁膜3と複数のLOCOS酸化膜6が形成されている。さらに、その上にはポリシリコンからなる応力緩和部材7が選択的に形成されている。この応力緩和部材7は、LOCOS酸化膜7とシリコン基板2の段差を利用して凹凸状に形成されている。さらに、応力緩和部材7と下地絶縁膜3の上には、BPSGからなる層間絶縁膜8とアルミニウムからなる電極パッド9が形成され、その上にはPSG膜10及びポリイミド膜11からなる保護膜12が積層形成されている。

(もっと読む)

1 - 17 / 17

[ Back to top ]