Fターム[5F033SS21]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | 塗布 (1,869)

Fターム[5F033SS21]の下位に属するFターム

塗布後に焼成するもの (977)

Fターム[5F033SS21]に分類される特許

881 - 892 / 892

精密ポリシリコン・レジスタ・プロセス

【課題】 製造されるポリシリコン・レジスタのシート抵抗の許容誤差をより正確に制御する精密ポリシリコン・レジスタを製造するためのプロセスを提供する。

【解決手段】 プロセスは、一般に、部分的に形成されたポリシリコン・レジスタを有するウェハに対して、エミッタ/FET活性化高速熱アニール(RTA)を行うステップと、それに続いて、保護誘電体層をポリシリコン上に堆積させるステップと、ドーパントを該保護誘電体層を通して該ポリシリコンに注入して、ポリシリコン・レジスタの抵抗を定めるステップと、シリサイドを形成するステップとを含む。

(もっと読む)

シリル化剤を用いる低誘電率誘電材料の損傷の修復

エッチング剤又はアッシング処理を受けた有機ケイ酸塩ガラス誘電体膜の表面に疎水性を回復するための方法。これらの膜は、これらの膜の低く安定な誘電特性を確保するために集積回路の製造で絶縁材料として使用されている。該方法は、これらの膜に応力誘起ボイドが形成されるのを防止する。有機ケイ酸塩ガラス誘電体膜は、ビア及びトレンチを形成するためにエッチング剤又はアッシング試薬による処理を受けてパターン化されるが、その処理が以前に存在していた炭素含有部分の少なくとも一部を除去するようなものであるため、前記有機ケイ酸塩ガラス誘電体膜の疎水性が削減される。ビア及びトレンチはその後金属で充填され、アニール処理を受ける。膜がエッチング剤又はアッシング試薬に当てられた後、アニール処理にかけられる前に、膜を強化剤組成物と接触させ、炭素含有部分の一部を回復し、有機ケイ酸塩ガラス誘電体膜の疎水性を増大させる。 (もっと読む)

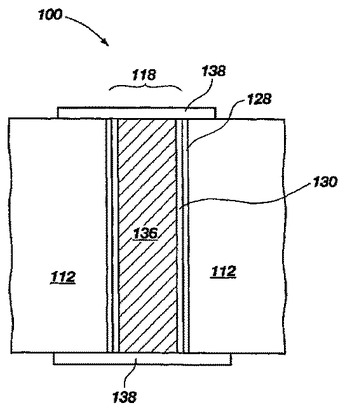

導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

半導体構成部品に導電性ビアを形成するための方法が開示される。この方法は、第1の表面及び反対側の第2の表面を有する基板112を設けるステップを含む。この基板に、第1の表面と反対側の第2の表面の間に延びる少なくとも1つの穴118が形成される。基板のこの少なくとも1つの穴を画定している側壁にシード層128が形成され、導電層130でコーティングされ、この少なくとも1つの穴の内部の残りの空間に、導電性材料又は非導電性充てん材料136が導入される。基板を貫通した導電性ビアを、ブラインド・ホールを使用して形成する方法も開示される。本発明の導電性ビアを含む基板を有する半導体構成部品及び電子システムも開示される。  (もっと読む)

(もっと読む)

表示装置及びその作製方法

【課題】 配線抵抗による電圧降下の影響や画素への信号の書き込み不良や階調不良などを防止し、より高画質のEL表示装置や液晶表示装置を代表とする表示装置を提供することを課題とする。

【解決手段】 本発明はEL表示装置や液晶表示装置を代表とする表示装置に用いられる電極や配線として、Cuを有する配線を設ける。また、該配線のCuを主成分とする導電膜は、マスクを用いたスパッタ法により形成する。このような構成により、電圧降下や信号のなまりを低減することができる。

(もっと読む)

配線構造、表示装置および能動素子基板

【課題】 パターニングフリーの能動素子基板の提供。

【解決手段】 能動素子基板は、基板上に形成された能動素子1と、能動素子1上に形成された導電膜2とを有する。導電膜2は、能動素子1から出力された電気信号を有限範囲内に伝達する。

(もっと読む)

配線構造

【課題】 高い周波数が印加され、数cm〜数10cmの長さを有する配線の抵抗を低減し、伝送される信号波形のなまりを低減する。

【解決手段】 高周波が印加される配線111は、層間絶縁膜107を介して、配線111の線方向にそって複数設けられたコンタクトホールにより配線106と電気的に並列接続している配線構造を採用する。その配線構造を周辺回路一体型アクティブマトリクス型液晶表示装置の周辺回路に用いることで、高周波信号が印加される配線において信号波形のなまりを低減できる。

(もっと読む)

多層微細配線構造およびその作製方法

【課題】 高速情報処理用デジタル集積回路チップ内およびそのチップを搭載するためのパッケージ、モジュール、ボードなどの実装系内における多層配線の作製方法に関する新しい多層微細配線構造およびその作製方法を提案する。

【解決手段】 高解像感光性ポリイミドを絶縁層として、銅、銀、金、アルミニウム、パラジウム、ニオブなどの金属を配線層として用いて、ストリップライン、マイクロストリップライン、同軸ラインなどの伝送線路構造を有する多層微細配線構造を実現するため、広い周波数帯域について、インピーダンスが一定に制御され、デジタル高速信号伝送に適する線路を実現することができる。高解像特性を有する感光性ポリイミドを絶縁層として用いることにより、絶縁層へのビア穴加工がリソグラフィ工程のみで達成され、また、金属配線層をリフトオフ法によりパターン形成することにより、従来の多層配線技術に比べて、高密度の配線構造が実現でき、大幅に工程が簡略化される。

(もっと読む)

デュアルダマシンによる半導体装置の製造方法

【課題】 放熱性が良好で、製造コストが低く、微細加工に好適なデュアルダマシンによる半導体装置の製造方法を提供する。

【解決手段】 基板1上に無機層間膜5、有機層間膜6、シリコン酸化膜からなる下部マスク7、シリコン窒化膜からなる上部マスク8を形成し、上部マスク8上にシリコン酸化窒化膜からなり膜厚が20乃至100nmであるカバーマスク10を形成する。そして、反射防止膜11及びレジスト膜12を形成する。次に、レジスト膜12をマスクとして、反射防止膜11、カバーマスク10、下部マスク7をエッチングする。そして、カバーマスク10をマスクとして、有機層間膜6及び無機層間膜5をエッチングしてビアホールを形成する。次に、上部マスク8をマスクとして有機層間膜6をエッチングして配線溝を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】 微細トランジスタと高耐圧トランジスタの線幅バラツキを低減する。

【解決手段】 P型の半導体基板1上の段差部を境にしてP型ウエル2及びN型ウエル3が形成されたものにおいて、段差低部に形成される前記P型ウエル2上に第1線幅を有する第1のトランジスタ(微細トランジスタ)が形成され、段差高部に形成される前記N型ウエル3上に第1のトランジスタよりも線幅の太い第2線幅を有する第2のトランジスタ(高耐圧トランジスタ)が形成されていることを特徴とする。

(もっと読む)

半導体チップ、配線基板およびそれらの製造方法ならびに半導体装置

【課題】複数の半導体チップを配線基板に積層しても、半導体チップを積層した半導体装置の厚みおよび基板面積の増大および半導体チップ間の配線長の増加を招かない半導体チップ、その製造方法および半導体装置等を提供する。

【解決手段】半導体基板13と、半導体基板13の第1の面14に形成された第1の外部電極21と、半導体基板13の第2の面17に形成された第2の外部電極22と、半導体基板13に形成された貫通孔16とを有し、貫通孔16は第2の面17となす内角が鈍角をなして形成された斜面15に設けられ、第1の外部電極21と第2の外部電極22とは、貫通孔16の内壁および斜面15を経由して形成された導電パターン19により電気的に接続されている。

(もっと読む)

導電線間に空隙を有する導電線構造体の製造方法

【課題】半導体回路の隣接導体線間容量性クロストークを減少させる。

【解決手段】フィラー材料を蒸発させて形成された空隙を有する金属被覆体の製造方法で、フィラー材料30は透過性の誘電層40により覆われる。フィラー材料はPPG、PB、PEG、非結晶フッ化炭素及びPCLからなる群から選択され、スピン・オン法又はCVD法により形成される。フィラー材料を、間隔をあけた導電線20及び半導体構造体10上に形成し、エッチバック処理し、導電線の上面を露出させる。次に、フィラー材料上に透過性の誘電層40を形成する。透過性の誘電層は分解したガス相フィラー材料が拡散するのを許容する性質がある。フィラー材料を蒸発させ、気相フィラー材料に変化させる。気相のフィラー材料は透過性の誘電層を通じて拡散して、間隔をあけた導電線の間に空隙を形成する。透過性の誘電層上に絶縁層が形成される。

(もっと読む)

絶縁層及び接続孔の形成方法、配線構造及びその形成方法

【課題】 絶縁層及びヴィア形成において、形成された絶縁層の表面が非常に平滑となり、薄膜素子等を信頼性及び歩留り良く、高い自由度を以って形成でき、さらには微小なヴィア形成が可能である絶縁層及びヴィア(接続孔)の形成方法、及びそれを用いた多層配線基板並びにモジュール基板等の配線構造及びその形成方法を提供する。

【解決手段】 台座20を介してマスク基板21を配置し、この基板21とコア基板1との間に感光性エポキシ樹脂などの感光性絶縁材料3Aを介在させ、これをパターン露光して現像してヴィアホール7を形成する。この現像により、微小なヴィアホール7を形成できると同時に、マスク基板21のコア基板対向面21aによって絶縁材料(従って、絶縁層3)を平坦かつ滑らかな表面に、しかも常に設定された厚みに形成することができる。

(もっと読む)

881 - 892 / 892

[ Back to top ]