Fターム[5F033VV12]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | 検査、試験 (365)

Fターム[5F033VV12]に分類される特許

361 - 365 / 365

導体におけるジュール加熱と電流密度間の関係を確立するための方法及びシステム

例示的な一実施形態に従って、導体におけるジュール加熱とこの導体における電流密度間の関係を確立するための方法がウェーハレベル測定(500)を実行することによって実装される。この実施形態に従って、導体(118,)における抵抗の温度係数を得るためにウェーハレベル測定が実行される(ステップ502)。本方法は、又、導体の熱抵抗を判断することを含む(ステップ510)。この熱抵抗は、その後導体におけるジュール加熱と導体における電流密度間の関係を確立するために利用される(ステップ512)。そのようにして得られた関係は、その後、信頼性のある半導体デバイス設計において補助するために設計ルール、平均故障時間、及び他の情報を判断するために利用される(ステップ514)。もう1つの実施形態に従って、ウェーハレベル測定システム(100)が導体におけるジュール加熱と導体における電流密度間の関係を確立するために利用される。  (もっと読む)

(もっと読む)

半導体装置の製造方法,半導体装置、エッチング条件の設定方法、導電膜除去条件の設定方法、及びレチクル

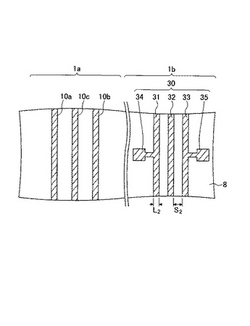

【課題】 導電膜が正常にパターニングされて配線が形成されていることを、少ない労力で確認することができるようにする。

【解決手段】 層間絶縁膜8上に導電膜を形成する工程と、前記導電膜をパターニングすることにより、チップ領域1aに配線10a〜10cを形成すると共に、スクライブライン1b上に、複数のダミー配線31〜33を互いに平行に形成する工程と、複数のダミー配線31〜33相互間の抵抗値を測定する工程とを具備する。最外側に位置するダミー配線31,33それぞれに接続するパッド34,35を形成し、このパッド34,35に抵抗計の端子を接触させてもよい。

(もっと読む)

エッチング条件の設定方法、半導体装置の製造方法、及び半導体装置

【課題】 少ない労力でビアホール等を形成するときのエッチング条件が適切か否かを確認できるようにする。

【解決手段】 基準部、該基準部より低地である低地部、及び前記基準部より高地である高地部を有する半導体基板1上に、導電膜2及び層間絶縁膜3を形成し、層間絶縁膜3の表面を平坦化する。層間絶縁膜3をエッチングすることにより、低地部の上方に位置する第1及び第2の接続孔3a、前記基準部の上方に位置する第3の接続孔3b、及び高地部の上方に位置する第4の接続孔3cを同時に形成する。第1〜第4の接続孔3a〜3cそれぞれに、第1〜第4の導電体4a〜4cを埋め込む。層間絶縁膜3上に、第1の導電体3a、第3の導電体4b及び第4の導電体4cを互いに接続する上部電極5bを形成し、上部電極5bと、第1の導電体3aとの間の抵抗を測定する。

(もっと読む)

半導体装置

本発明は、ボンディングパッドで発生する応力に対する強度を向上させることが可能な半導体装置を提供することを目的とする。本発明に係る半導体装置においては、半導体チップ上にボンディングパッド(1)が複数個設けられる。それぞれのボンディングパッド(1)においては、最上層の配線層を用いて形成された第1メタル(11)の下に、ライン状の第2メタル(12)が複数個設けられる。そして、上記目的を達成するために、ボンディングパッド(1)は、第2メタル(12)の長手方向に並べて配設される。つまり、第2メタル(12)の長手方向(L1)と、ボンディングパッド(1)の配列方向(L2)とが同じ方向になるように、ボンディングパッド(1)を並べて配設する。 (もっと読む)

薄膜トランジスタ表示板、これを含む平板ディスプレイ表示装置及びその製造方法

本発明は、薄膜トランジスタ表示板とこれを含む液晶表示装置及びその製造方法に関し、薄膜トランジスタ表示板は液晶表示装置や有機EL(electro luminescence)表示装置などで、各画素を独立的に駆動するための回路基板において、画素電極またはゲート線及びデータ線の拡張部を外部回路と接続させるコンタクト補助部材を、IZO及びITOの2重層で形成することに対する発明であって、IZOで形成された下部層とITOで形成された上部層を有するように形成する。前記のように画素電極またはコンタクト補助部材を二重層で形成することによって、エッチング過程で下部配線が損傷されることを防止し、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を良好に確保することができる。また、コンタクト補助部材のみをIZOとITO二重層で形成することによって、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を確保することができ、ITOの使用を減らすことによって製造単価を下げることができる。  (もっと読む)

(もっと読む)

361 - 365 / 365

[ Back to top ]