Fターム[5F038AR17]の内容

Fターム[5F038AR17]に分類される特許

1 - 20 / 55

半導体装置

【課題】抵抗値が制御されることができる抵抗素子を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、絶縁膜14bと、半導体素子と、抵抗素子4tとを有する。絶縁膜14bは半導体基板101の少なくとも一部を被覆している。半導体素子は、半導体基板101の一部からなるチャネル領域と、電極とを有する。抵抗素子4tは、電極を流れる電流に対する抵抗となるように電極と電気的に接続され、かつ絶縁膜14bを介して半導体基板101上に設けられている。抵抗素子4tは半導体領域を含む。半導体基板101と抵抗素子4tとの間の電位差により半導体領域に空乏層が生じる。

(もっと読む)

半導体装置およびその製造方法

【課題】チップ面積の増加を抑えつつ、金属等からなるゲート電極を有するMISトランジスタと、抵抗体とを同一基板上に不具合なく形成する。

【解決手段】半導体装置は、半導体基板1上にそれぞれ設けられたMISトランジスタと抵抗素子とを備える。MISトランジスタは、活性領域1aと、活性領域1a上に設けられたゲート絶縁膜18と、ゲート絶縁膜18上に設けられたゲート電極19とを有する。抵抗素子40は、素子分離領域2上に設けられた抵抗体10を有しており、ゲート電極19の少なくとも一部は、抵抗体10よりも小さな抵抗率を有しており、活性領域1a上においてはゲート電極19の上面を覆っておらず、抵抗体10の上面を覆っている層間絶縁膜16がさらに設けられる。

(もっと読む)

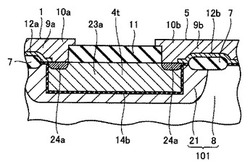

半導体装置及びその製造方法

【課題】 シリコンビームを使用しかつダブルゲートを有する半導体装置のおけるプロセスばらつきによる抵抗値ばらつきを防止する。

【解決手段】 端部に凹部を有する基板1と、基板1の凹部に一部が埋め込まれた一対のゲート電極4と、基板1の表面であって一対のゲート電極4の間に形成された拡散層7を有し、ゲート電極4と拡散層7の間の電位を変化させることにより、拡散層7の抵抗値を変化させる。

(もっと読む)

半導体装置

【課題】半導体装置において、高電圧の配線層とその下方を横切るように配置された抵抗層との間の絶縁膜の耐圧を確保し、この配線層と抵抗層との間で破壊が起きるのを抑制することを目的とする。

【解決手段】第1半導体領域10に接続され第2半導体領域11上を通過するように第3配線層22が配置されている。第3配線層22と第2半導体領域11との間に配置される絶縁膜14内には、一端が第3配線層22に接続されると共に、他端が第1半導体領域11よりも電位の低い制御端子12に接続され、且つ第3配線層22とSOI層2との間において第3配線層22を少なくとも1回以上横切る構成で抵抗層25が配置されている。この抵抗層25は、第3配線層22を横切る部位の上面が他の部位よりも下方位置となるように段差状に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の小型化を実現する。

【解決手段】 第1の絶縁膜上に、島状の半導体層及び前記半導体層を囲む第2の絶縁膜を形成し、前記半導体層の上面と平面的に重なるようにして導電膜からなる抵抗素子(例えばポリシリコン抵抗素子)を配置する。

(もっと読む)

マルチゲート半導体デバイス

【課題】バランス抵抗器の接続されたゲート間伝導領域を有するマルチゲート半導体デバイスにおいて、スイッチ素子として使用した際の低挿入損失と素子サイズを抑えつつ、オフ時の非線形性を改善する。

【解決手段】バランス抵抗器405のゲート間伝導領域への接続点をゲートの2つの両端より内側に設ける。好ましくはメアンダ状ゲートの屈曲領域4061に設ける。

(もっと読む)

半導体装置

【課題】 占有面積の増加を少なく、十分なESD保護機能を持たせたESD保護用のN型のMOSトランジスタを有する半導体装置を提供する。

【解決手段】 ESD保護用のN型MOSトランジスタのドレイン領域は、トレンチ分離領域の側面および下面に設置されたドレイン領域と同一の導電型の不純物拡散領域によって形成されたドレイン延設領域を介して、ドレイン領域と同一の導電型の不純物拡散領域によって形成されたドレインコンタクト領域と電気的に接続している半導体装置とした。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】信頼性および集積性に優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板(シリコン基板1)と、シリコン基板1に設けられた第1のトレンチ3と、第1のトレンチ3に埋め込まれた受動素子層10と、第1のトレンチ3と受動素子層10との間に設けられた第1の絶縁膜(シリコン窒化膜4)と、を備え、上面視において、第1のトレンチ3形成の周縁部分と第1の絶縁膜(シリコン窒化膜4)の周縁部分とが略一致している。

(もっと読む)

抵抗素子を有する半導体装置及びその製造方法

【課題】基準電圧を調整する回路を構成する抵抗素子を有するフラッシュ記憶素子である半導体装置及びその製造方法を提供する。

【解決手段】フラッシュ記憶素子である半導体装置の製造方法は、半導体基板上にトレンチを定義する鋳型パターンMLDPを形成し、鋳型パターンMLDP上にトレンチを横切る抵抗パターンRPを形成し、抵抗パターンRP上に互いに離隔された第1及び第2導電パターン210、220を形成し、第1及び第2導電パターン210、220に各々接続する第1及び第2配線UL1,UL2を形成する段階を有し、第1及び第2導電パターンUL1,UL2は鋳型パターンMLDPの上部に各々形成される。

(もっと読む)

半導体装置

【課題】環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮可能な半導体装置を提供する。

【解決手段】半導体装置10は、ユニポーラ型の還流ダイオード100と、還流ダイオード100に対し並列接続され、基板領域21とキャパシタ210と抵抗220とを含む半導体スナバ200とを備えている。抵抗220の少なくとも一部が、半導体スナバ200の基板領域21の一主面上に直接的にもしくは間接的に形成された、導電性材料からなる膜状の導電層17を含み、かつ、抵抗220に電流が流れる際に、導電層17に流れる電流の経路の少なくとも一部が、膜厚方向以外の方向へ流れる。

(もっと読む)

抵抗素子、および、その製造方法

【課題】抵抗素子の特性のバラツキが発生することを抑制し、製造歩留まり、および、信頼性を向上する。

【解決手段】抵抗体膜TMを基板上に形成後、その抵抗体膜TM上にて抵抗素子311の実効抵抗部JTに対応する領域の面を被覆し、他の領域の面が露出するように、ハードマスク層M1を形成する。そして、そのハードマスク層M1を被覆するように導電体膜DMを抵抗体膜TM上に形成後、その導電体膜DM上にて一対の電極層313を設ける領域の面を被覆し、他の領域の面が露出するように、フォトレジストマスク層PM2を形成する。そして、ハードマスク層M1およびフォトレジストマスク層PM2をマスクとして用いて、抵抗体膜TMおよび導電体膜DMについてパターン加工を実施する。

(もっと読む)

半導体装置およびその製造方法

【課題】拡散抵抗領域の長手方向の端部と該拡散抵抗領域の長手方向にある絶縁分離用トレンチ内の(ドープド)ポリシリコン膜との電気的接続に要する表面面積を少なくすることのできる半導体装置およびその製造方法を提供すること。

【解決手段】前記拡散抵抗領域7はトレンチ3aより相互に絶縁分離され、前記トレンチ3aの側壁にゲート絶縁膜4aを介して設けられているポリシリコン5aが、前記拡散抵抗領域3のいずれか一方の端部のp+コンタクト領域7bのみに接続され、短絡されている半導体装置とする。

(もっと読む)

半導体装置

【課題】薄膜SOI領域を有する基板において、基板に第1半導体素子10と異なる第2半導体素子30、40を形成した際に、この第2半導体素子30、40の特性を従来の半導体装置より向上させることができる半導体装置を提供する。

【解決手段】基板のうち第1半導体素子10が形成される第1半導体素子形成領域1とは異なる部分を第2半導体素子形成領域2とし、第2半導体素子形成領域2に、基板の表裏を貫通する第1貫通トレンチ31を形成し、第1貫通トレンチ31の側壁に絶縁膜32を形成すると共に第1貫通トレンチ31の内部に第1埋込材料33を埋め込む。そして、第1埋込材料33を有する第2半導体素子30、40を形成して半導体装置を構成する。

(もっと読む)

半導体装置およびその製造方法

【解決手段】 本発明による半導体装置は、メタル抵抗素子の下面に形成された下面酸化防止絶縁膜と、上面に形成された上面酸化防止絶縁膜と、下面酸化防止絶縁膜及び上面酸化防止絶縁膜とは別工程で、ウェハ全面に堆積した後に異方性エッチングを施しメタル抵抗素子の側面近傍にのみ形成された側面酸化防止絶縁膜とを有する。

【効果】 本発明によれば、メタル抵抗素子が酸化されて抵抗値が上昇するのを防止することができると同時に、加工プロセスを複雑にすることなく金属配線層間の寄生容量の増大を防止することができる。

(もっと読む)

半導体装置およびその製造方法

【目的】低コストで薄い絶縁膜を形成でき、コンタクトホールの開口部を小さくしてチップサイズを縮小化できる半導体装置およびその製造方法を提供する。

【解決手段】隣接する小トレンチ分離抵抗群22で挟まれた箇所にトレンチ4を形成しない半導体領域26を形成することで、トレンチ4を埋め込む層間絶縁膜(第2絶縁膜9)の厚さを薄くできる。層間絶縁膜を薄くすることで、コンタクトホール10の開口部を小さくできてチップサイズを小型化できる。また、コンタクトホール10を形成するためのエッチング時間が短縮できて製造コストを低減できる。

(もっと読む)

半導体装置

【課題】 保護対象回路を静電気放電から保護するために保護対象回路に接続されている保護素子を備えている半導体装置において、保護素子の厚みを増やすことなく保護素子の素子面積を低減でき、かつESD信号の印加部とゲート電極の間の抵抗値を容易に調整することができる保護素子を備えている半導体装置を提供する。

【解決手段】 半導体装置100は、保護対象回路12とパッド10と保護素子90を備えている。保護素子90には、第1ドレイン電極14とソース電極2と第2ドレイン電極6とゲート電極4と素子分離トレンチ18が形成されている。ドレイン電極14、6と素子分離トレンチ18の間はアルミ配線8で接続されている。パッド10から第1ドレイン電極14にESD信号が印加されると、第1ドレイン電極14から素子分離トレンチ18を経由して第2ドレイン電極6にESD電流が流れる。

(もっと読む)

半導体装置およびその製造方法

【課題】抵抗素子として機能する配線を有し、かつ面積の小さな半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板SBと、半導体基板SB上に設けられた第2の配線層L2とを備えている。第2の配線層L2は、通常の配線WRと、高抵抗配線REと、通常の配線WRおよび高抵抗配線REを埋め込む絶縁膜8とを含んでいる。通常の配線WRは、第1の銅部10Wと、第1の銅部10Wの底面側および側面側を覆う第1のバリアメタル膜9Wとを有している。高抵抗配線REは、空洞部CVと、空洞部CVの底面側および側面側を覆う第2のバリアメタル膜19Rとを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】 抵抗体を備えた半導体装置の小型化、集積化を図ること。

【解決手段】 半導体基板の表面に、半導体基板とは逆の導電型であるエピタキシャル層を形成し、抵抗となる部分以外にトレンチを形成し、前記トレンチに絶縁膜を埋め込むことで互いに分離された抵抗体を3次元的に形成する。

(もっと読む)

抵抗素子を有する半導体装置及びその形成方法

【課題】本発明は、製造工程の間に相対的に安定に維持され、予測可能な抵抗値を有する抵抗素子を含む半導体装置とその形成方法を提供する。

【解決手段】この半導体装置は、第1領域と第2領域を備える基板と、第1領域の基板上の、第1ゲート絶縁膜及び該第1ゲート絶縁膜上の第1ゲート電極膜を備えた少なくとも一つの第1ゲート構造物と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】抵抗値の設定精度を向上させる。

【解決手段】抵抗体チップ1Aは、抵抗体2Aと、その両端に電気的に接続された引き出し用電極パッド3A,3Bとを有している。抵抗体2Aは、抵抗値を設定する抵抗本体であり、半導体基板5上の絶縁膜に形成された抵抗形成溝4a内に埋め込まれている。引き出し用電極パッド3A,3Bは、半導体基板5上の絶縁膜に形成されたパッド溝4b内に埋め込まれている。上記抵抗体2Aを半導体プロセス(リソグラフィ、エッチングおよび化学的機械的研磨等)を用いて形成することで、抵抗体2Aの幅および膜厚の加工寸法誤差を低減できる。このため、抵抗体チップ1Aの抵抗値の設定精度を向上させることができる。また、抵抗体チップ1Aの微細化を図ることができるので、高集積化もできる。さらに、半導体装置の製造工程で用いられている製法を用いるので、抵抗体チップ1Aの信頼性をも向上させることができる。

(もっと読む)

1 - 20 / 55

[ Back to top ]