Fターム[5F038AZ01]の内容

Fターム[5F038AZ01]に分類される特許

1 - 20 / 112

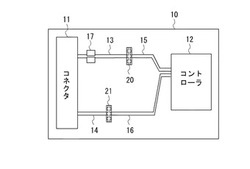

リドライバIC、半導体装置、及びその製造方法

【課題】低損失で差動信号を伝送することができるリドライバIC、半導体装置、及びその製造方法を提供する。

【解決手段】本実施の形態に係る半導体装置は、差動信号が伝送される差動配線が形成された配線基板10と、配線基板10に搭載され、外部機器に対して差動信号を送受信するコネクタ11と、配線基板10に搭載され、コネクタ11から受信した差動信号を中継する受信系のリドライバIC21と、受信系のリドライバIC21と離間した位置において配線基板10に搭載され、コネクタ11に送信する差動信号を中継する送信系のリドライバIC20と、を備えるものである。

(もっと読む)

プローブカード、半導体装置、半導体装置の試験方法、及び、半導体装置の製造方法

【課題】差動伝送方式を採用した半導体装置の試験で行われるTDRタイミング測定の校正精度の低減を抑制すること。

【解決手段】複数のプローブ針を有し、プローブ針を半導体装置の電極パッドと接続させて所定の試験を行うためのプローブカードであって、互いに異なる電極パッドP1及びP2に接続するよう配置され、対となっている差動信号入力用の第1及び第2のプローブ針1a及び2aと、互いに異なる電極パッドP1及びP2に接続するよう配置された第3及び第4のプローブ針1b乃至2b´と、第3及び第4のプローブ針1b乃至2b´各々と接続して、第3及び第4のプローブ針1b乃至2b´を導通させる配線3及び抵抗部材RTと、を有し、第3及び第4のプローブ針1b乃至2b´、配線3及び抵抗部材RTは電気的にフローティングな状態となっている。

(もっと読む)

半導体装置

【課題】伝送線路を接続するビア層の周囲のグラウンドを強化することができると共に、ビア部の特性インピーダンスを調整することが可能な半導体装置を提供する。

【解決手段】絶縁層14を介して積層された第1の半導体基体11及び第2の半導体基体21と、第1の半導体基体11に形成され、信号線12とグラウンド13とを含む第1の伝送線路と、第2の半導体基体21に形成され、信号線22とグラウンド23とを含む第2の伝送線路と、第1の伝送線路の信号線12及び第2の伝送線路の信号線22に接続された信号線用のビア層と、第1の伝送線路のグラウンド13及び第2の伝送線路のグラウンドに接続された、グラウンド用の第1のビア層と、第2の伝送線路のグラウンド23に接続され、かつ、信号線用のビア層に対向して形成された帯状のビア層を含む、グラウンド用の第2のビア層16を有する半導体装置を構成する。

(もっと読む)

半導体装置

【課題】規格により規定された速度による信号の転送を実現し、半導体装置やそれを内蔵した電子機器の誤動作を防止する。

【解決手段】第1の半導体素子101の導体配線層106に、パッケージ基板100の信号端子103と第2の半導体素子102の信号端子117とを接続する信号線導体113aと、パッケージ基板100の電源端子104と第2の半導体素子102の電源端子118とを接続する電源導体114とを、信号線導体113aが導体配線層106において、信号線導体113aとの間に水平方向に一定の間隔をあけて隣接する電源導体114に挟まれるように形成する。

(もっと読む)

電力増幅器

【課題】複数のトランジスタを均一に動作させ、低消費電力及び良好な歪特性を実現する。

【解決手段】高周波信号を増幅する電力増幅器100であって、上部電極120a及び下部電極120bを有し、高周波信号が入力される整合容量120と、整合容量120の下部電極120bから出力される高周波信号を増幅する複数のトランジスタ110が所定の方向に並んで配置されているトランジスタ列とを備え、トランジスタ列に隣り合う領域において、トランジスタ列の両端から略等しい距離には、接地されたビアホール170が形成され、下部電極120bは、ビアホール170を挟んで高周波信号が均等に分配されるように配置されたマイクロストリップ線路であり、複数のトランジスタ110のベース端子に接続される。

(もっと読む)

コプレーナ線路のエアブリッジ構造

【課題】コプレーナ線路の信号線路とエアブリッジとの交差容量の影響を抑制しつつ、複数のエアブリッジを容易に使用できるようにする。

【解決手段】エアブリッジ構造100のうち、下層配線層8に、接地線路2A,2Bのうち信号線路1を挟んで互いに対向する位置を切り欠いて形成した空孔領域12A,12Bをそれぞれ設けるとともに、上層配線層7に、空孔領域12Aの上部位置に下層配線層8の接地線路2Aと電気的に接続された上層接地電極13Aと、空孔領域12Bの上部位置に下層配線層8の接地線路2Bと電気的に接続された上層接地電極13Bとを設け、エアブリッジ3で、上層接地電極13A,13Bを介して接地線路2A,2B間を電気的に接続する。

(もっと読む)

半導体装置

【課題】超高周波帯におけるシリコン基板による損失を低減すると共に、貫通配線のインダクタンス成分の影響を小さくした半導体装置を実現できるようにする。

【解決手段】半導体装置は、回路素子105が形成された半導体基板100と、半導体基板100の主面の上に形成された第1の誘電体層121と、第1の誘電体層121の上に形成された第2の誘電体層131と、第1の誘電体層121を貫通し、回路素子105と接続された第1の貫通配線122と、第2の誘電体層131を貫通し、第1の貫通配線122と接続された第2の貫通配線132とを備えている。第2の貫通配線132は、第1の貫通配線132よりもインダクタンスが小さい。

(もっと読む)

伝送線路および伝送装置

【課題】コモンモードノイズを減衰することができ、通常のシリコン半導体製造プロセスにおいて実現でき、シリコン半導体回路と一体化するよう同一のチップ内に実装可能なコモンモードノイズフィルタとして機能する伝送線路および伝送装置を実現する。

【解決手段】第1の仮想平面VP1の面内方向に沿って既定の間隔で並行に設けられた2本の信号線101,102と、第1の仮想平面VP1と並行な第2の仮想平面VP2の面内方向に沿って2本の信号線101,102を第2の仮想平面VP2に投影したときの投影像の延長方向と直交する方向に互いに所定の間隔で平行に配置された各所定長の複数の導体である各フローティングシールド片110−1〜110−nを含むシールド体110と、を備え、2本の信号線およびシールド体はシリコン半導体製造プロセスにより形成されていることを特徴とする伝送線路および伝送装置。

(もっと読む)

高周波スイッチ

【課題】出力特性が優れた高周波スイッチを提供する。

【解決手段】本発明の実施形態の高周波スイッチは、入力端子ANT1と複数のスイッチング素子と複数の高周波信号線と複数の出力端子RF1〜RF8とからなる高周波スイッチ回路部を有する高周波スイッチICチップ10を備える。前記入力端子ANT1と前記複数の出力端子の各出力端子RF1〜RF8は、それぞれ等しい長さの高周波信号線H1〜H8で接続される。前記複数の出力端子RF1〜RF8は、前記高周波スイッチICチップの外周の表面上に配置される。前記入力端子ANT1は、前記高周波スイッチ回路部の中心に配置される。

(もっと読む)

伝送線のためのシールド構造体

シールド構造体は、集積回路上の第1金属化層に形成された櫛状構造体が複数の歯を備え櫛状構造体の歯は他方の櫛状構造体に向かって延びる第1、第2櫛状構造体と、第1櫛状構造体から上方に延びる複数の第1導電性ビアと、第2櫛状構造体から上方に延びる複数の第2導電性ビアと、第1金属化層の上方の第2金属化層に配置された第1、第2平面構造体と、第1平面構造体から複数の第1導電性ビアに向かって下方に延びる複数の第3導電性ビアと、第2平面構造体から複数の第2導電性ビアに向かって下方に延びる複数の第4導電性ビアとを備え、第1、第2櫛状構造体、第1、第2平面構造体及び第1〜第4導電性ビアは全て同電位であり接地されることが好ましい。ある実施形態では1つ以上の信号線が第1、第2平面構造体間の第2金属化層に配置され、他の実施形態では1つ以上の信号線が第1、第2平面構造体間の第3金属化層に配置される。 (もっと読む)

半導体集積回路装置

【課題】消費電力を抑制することができる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置100は、差動信号を送信する差動信号送信素子11、差動信号を伝送する一対の第1の差動伝送線路12A、12B、差動信号送信素子11と一対の第1の差動伝送線路12A、12Bとの間に接続された一対の結合コンデンサ14A、14B、一対の第1の差動伝送線路12A、12Bの終端間に接続された終端抵抗13を備えた第1の半導体集積回路素子1と、一対の第1の差動伝送線路12A、12Bと容量性結合及び誘導性結合するように一対の第1の差動伝送線路12A、12Bに予め定めた距離を離して対向配置された一対の第2の差動伝送線路22A、22B、一対の第2の差動伝送線路22A、22Bの終端に接続され且つ差動信号を受信する差動信号受信素子21を備え、第1の半導体集積回路素子1に積層された第2の半導体集積回路素子2と、を備える。

(もっと読む)

半導体装置及びその信号伝送方法

【課題】隣接信号の間に発生するクロストークノイズ(Crosstalk Noise)による信号の品質低下を防止するための半導体装置及びその信号伝送方法を提供する。

【解決手段】複数の同種信号を伝送するための複数の伝送ラインを具備する半導体装置100において、第1信号IN1を伝送する伝送区間全体の間に第1信号IN1の位相を同一に維持して伝送するための第1伝送ライン150と、第1伝送ライン150に隣接して配置されて第2信号IN2を伝送する伝送区間全体のうちで一部区間の間に第2信号IN2の位相を反転させて伝送するための第2伝送ライン160a、160bが具備される。

(もっと読む)

可変スパイラルインダクタおよび半導体集積回路装置

【課題】インダクタンス値を変えることができ、インダクタ素子が占める基板上でのスペースを小さくしつつ、インダクタ素子を簡便な構成により実現可能とした可変スパイラルインダクタを提供する。

【解決手段】接地導体7を設けた半絶縁性の基板2と、この基板2に形成され、平面スパイラル状のパターンを有し、一端から入力された高周波信号を他端へ通過させるスパイラル導体5と、このスパイラル導体5に対し基板面に直交する方向で間隔を介して設けられたマイクロストリップライン導体6と、このマイクロストリップライン導体6の電位を接地電位又は開放電位にするための駆動バイアスを印加される電極4と、を備え、この電極4へ印加される駆動バイアスのオンオフ駆動により、マイクロストリップライン導体6の状態を高周波信号に対して等価的に接地状態又は短絡状態にし、高周波信号に対して値の異なるインダクタンスを生成する。

(もっと読む)

スパイラルインダクタおよびスパイラルインダクタの製造方法

【課題】誘電損を回避でき、挿入損失を小さくすることが可能なスパイラルインダクタを提供する

【解決手段】接地導体を設けた半絶縁性の基板2と、この基板2上に形成された誘電体膜3と、それぞれこの誘電体膜3上に形成された複数の支持体4と、これらの支持体4によって支持され、基板2上でスパイラル形状の導体パターンを有し、一方の端部7aから入力された信号を他方の端部7bへ通過させるマイクロストリップライン導体5と、を備え、このマイクロストリップライン導体5は、それぞれ導体パターンの形状に沿って設けられた複数の支持体4によってパターン裏面を支持される架橋構造を有する。

(もっと読む)

半導体装置

【課題】半導体装置の伝送線路の信号伝達効率を高くする

【解決手段】本発明は、多層配線400内に形成され、信号線342下にあり、トランジスタ領域上に形成された第1導体パターン312を有する、半導体装置に関する。第1導体パターン312はグラウンドまたは電源に接続し、トランジスタ領域と重なる。また、信号線342は第1導体パターン312と重なっている。第1導体パターン312は複数のトランジスタ形成領域と重なっていてもよい。第1導体パターン312の下にトランジスタ形成領域を複数有していていもよい。

(もっと読む)

電気回路

【課題】物理長の異なる複数の伝送線路において、電気長を等しくする。

【解決手段】半導体基板1上の薄膜絶縁体上に形成された物理長の異なる複数の伝送線路A、Bのうち、物理長の長いほうの伝送線路において、伝送線路を構成する信号線メタルと半導体基板1との間に低誘電率絶縁膜3を挟むことによって信号伝搬速度を速くした領域を設け、この低誘電率絶縁膜3を挟んだ領域の長さを伝送線路Aの物理長に応じて調整することによって、すべての伝送線路の電気長を等しくする。

(もっと読む)

半導体装置および通信装置

【課題】簡便な構成で半導体基板上にその伝播特性が可変な右手系材料、左手系材料による伝送線路を構成可能な半導体装置を提供する。

【解決手段】シリコン基板等の半導体基板11上に、メタマテリアル構造体の所謂左手系の伝送線路12を形成する。この伝送線路12は、キャパシタ部13、インダクタ部14およびMSM接合部15を含み、ハイパスフィルタを構成する。そして、MSM接合部15に外部から電圧V1を印加し、当該電圧V1の電圧値をコントロールすることによって伝播特性を可変とする。

(もっと読む)

半導体装置および携帯機器

【課題】差動信号の伝送特性に優れ、かつ、簡易な構成の半導体装置を提供する。

【解決手段】半導体装置100、一対の差動伝送線路26を含む配線層12と、電位が固定された導電層であって、電気的に連続した導体によって形成された連続領域を有する導電層16と、半導体基板24と、半導体基板24と導電層16との間に設けられ、電気的に浮いている導体を有する阻止層20と、配線層12と導電層16と阻止層20と半導体基板24との間に設けられた絶縁層と、を備える。一対の差動伝送線路26は、積層方向から見て導電層16の導体と交差し、阻止層20は、導電層16の導体と交差する複数の間隙が形成されている。

(もっと読む)

広帯域ESD保護を与える方法とそれにより得られる回路

【課題】伝送ラインや分布増幅器などの分配電子回路を開示する。

【解決手段】本発明は、インプットターミナル(2)と、アウトプットターミナル(3)と、電力供給ライン(4、5)と、インプットターミナル(2)とアウトプットターミナル(3)との間に設けられ一つのセクションから別のセクションへ電気信号を伝送するように配置された一連セクション(61、62、63、64、65)とを含み、個々のセクション(61、62、63、64、65)は、電子放電静電(ESD)イベントの発生の際に対応するESD電流を電力供給ライン(4、5)に運ぶように構成されたESD保護(9)を含み、個々のセクション(61、62、63、64、65)のESD保護要素(9)は、ESDイベントの発生の際に、最初のセクション(61)の前に後続のセクション(62、63、64、65)が起動されるように選択されている分配電子回路である。

(もっと読む)

相互誘導回路

【課題】専有面積の小さいトランス素子を提供すること。

【解決手段】トランス素子1は、半導体基板上において上下方向に平行な第1及び第2の配線層を使って形成され、第1のインダクタンス2及び第2のインダクタンス3を備える。第1及び第2のインダクタンス2及び3は、鉛直上方向及び鉛直下方向の一方から第1の配線層及び第2の配線層の一方に投影した時に、投影された外形線が予め定められた基準面を基準として対称な形状を有し、かつ投影された外形線が第1の配線層及び第2の配線層の一方上で交差し合う部分については、第1の配線層及び第2の配線層を使って交差しないよう構成される。

(もっと読む)

1 - 20 / 112

[ Back to top ]