Fターム[5F038AZ10]の内容

Fターム[5F038AZ10]に分類される特許

1 - 20 / 33

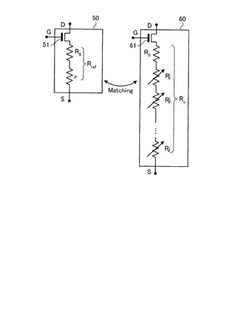

アナログ/デジタル変換器

【課題】変換精度が高いアナログ/デジタル変換器を提供する。

【解決手段】アナログ/デジタル変換器は、電圧生成部と複数の比較器とを備える。電圧生成部は、基準電圧を、複数の抵抗器で分圧して複数の比較用電圧を生成する。各比較器は、複数の比較用電圧のうちの何れかの比較用電圧とアナログの入力電圧との比較結果に応じたデジタル信号を出力する。各比較器は、2つの入力の電位差を検出する差動対回路を含む。差動対回路は、第1回路部50と第2回路部60とを有する。第1回路部は、第1入力トランジスタ51と、第1入力トランジスタと直列に接続される抵抗器Rrefとを含む。第2回路部は、第1入力トランジスタと差動対を形成する第2入力トランジスタ61と、第2入力トランジスタと直列に接続される可変抵抗器Rvとを含む。可変抵抗器は、直列に接続されるとともに、制御信号に応じて各々の抵抗値が可変に設定される複数の可変抵抗素子を含む。

(もっと読む)

半導体装置

【課題】FETの駆動力性能や遮断性能などを向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に形成され、オフ状態とオン状態とで閾値電圧を可変させるFETからなる半導体素子と、を備える。前記半導体素子は、前記半導体基板のチャネル形成箇所の上方に形成される絶縁膜と、前記絶縁膜の上方に配置されるゲート電極と、前記絶縁膜と前記ゲート電極との間に介挿され、前記チャネルとの間よりも、前記ゲート電極との間で、より多くの電子の授受を行なうチャージトラップ膜と、を有する。

(もっと読む)

半導体集積回路及び半導体集積回路の動作制御方法

【課題】温度が高くなりすぎたりあるいは低くなりすぎたりする発振状態となって、半導体集積回路が誤動作、動作停止等することを防止する。

【解決手段】実施形態によれば、半導体集積回路1は、回路部の温度又は動作速度に基づいて、温度が安定するように、回路部の制御パラメータを調整して、フィードバック制御を実行する制御部と、温度の時系列データである第1の履歴データと、制御パラメータの時系列データである第2の履歴データとを含む履歴データを格納する履歴レジスタ17と、履歴データからフィードバック制御の有効性を判定する有効性判定部24とを有する。

(もっと読む)

半導体装置

【課題】演算処理や電力消費を増大させることなく、温度特性が安定する半導体装置を提供することを課題とする。

【解決手段】高周波信号を処理する半導体装置1であって、高周波信号を処理する複数の素子2〜8が形成された半導体基板を備え、半導体基板には、複数の素子2〜8のうち温度に応じて特性が変化する特定の素子2,3,5〜8に隣接して該特定の素子2,3,5〜8を加熱する発熱素子9A〜Fが形成されている。

(もっと読む)

信号処理回路、及び信号処理回路の駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。そして、上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

集積素子

【課題】高速フォトダイオードの特性を劣化させることなく高速フォトダイオードと容量とを1チップ上に集積させる。

【解決手段】基板上に形成された高速フォトダイオード素子と、高速フォトダイオード素子と異なる層に形成されたMIM(Metal Insulation Metal)容量と、高速フォトダイオードの絶縁膜およびMIM容量の下地となる絶縁膜として機能する有機系塗布膜とを備えた集積素子。有機系塗布膜は、ポリイミド膜とすることができる。

(もっと読む)

集積回路の動作中に集積回路中で電気エネルギーを生成する方法、その方法に対応する集積回路及びその製法方法

【課題】集積回路の動作中に集積回路の少なくとも一部の電流の結果生じる集積回路の少なくとも1つの領域内の少なくとも1つの温度勾配の生成、及び前記温度勾配により電気エネルギーを生成する手段を備えた集積回路の提供。

【解決手段】少なくとも1つの熱電気材料MTHを含み集積回路の動作中に集積回路の少なくとも一部PSTA、PSTBにおける電流の流れにより生じる少なくとも1つの温度勾配にさらされるように構成された少なくとも1つの領域RG、及び前記領域に接続されて熱電気材料MTHにより生成された電気エネルギーを伝えるための電気的伝導出力手段を備えた集積回路。

(もっと読む)

単電子素子インピーダンス測定装置および単電子素子インピーダンス測定方法

【課題】測定のための回路部品を減じるとともに入力する周波数の帯域を広くして、単電子トランジスタのインピーダンスを高感度に求めることができる単電子素子インピーダンス測定装置を提供する。

【解決手段】単電子素子インピーダンス測定装置が、単電子の帯電エネルギーが動作温度における熱エネルギーと同程度またはそれ以上となるような微小伝導領域である微小島と当該微小島にトンネル障壁を介して接合する電極である入力電極とを有する単電子トランジスタと、微小島と静電的に結合されているポイント接合と、ポイント接合に接合する一方の電極および入力電極に広帯域周波数の位相可変高周波電圧信号が入力信号として独立して入力され、当該入力信号によって誘起される微小島と入力電極との間の時間的な電荷移動に伴う単電子トランジスタのインピーダンス変分を、ポイント接合に接合する他方の電極からの信号により位相検波する電荷検出計とを有する。

(もっと読む)

リチウム二次電池

【課題】半導体基板と正極活物質との放電時の電子抵抗が小さくエネルギー密度の高い正極を有するリチウム二次電池を提供する。

【解決手段】正極活物質からなる正極と半導体基板とが、充電状態にある正極活物質のp型又はn型の種類と半導体基板のp型又はn型の種類とが同じ型になる組み合わせで直接積層されていて、半導体基板が集電体して用いられるリチウム二次電池。

(もっと読む)

磁気センサ

【課題】 トンネル型磁気抵抗効果素子(TMR素子)を用いて磁気センサに係り、特に、従来に比べて、ESD耐性を向上させた磁気センサを提供することを目的とする。

【解決手段】 外部磁界に対して電気抵抗値が変動する磁気抵抗効果を利用した素子部を備える磁気センサS1であって、素子部は、トンネル型磁気抵抗効果素子(TMR素子)21を有して構成され、TMR素子21の上下には電極層23,24が設けられており、TMR素子21の側方には前記電極間に位置しTMR素子21と並列に接続されるコンデンサ層42が設けられ、前記コンデンサ層42の静電容量C2は、前記TMR素子21の静電容量C1より大きい。

(もっと読む)

トリミング装置及び圧電デバイス

【課題】量産時の歩留まりの悪化を防ぎ、しかも生産時の工数を大幅に削減することがで

きるトリミング装置を提供する。

【解決手段】n個のヒューズトリミング選択回路21と、入力されるシリアルのデータを

パラレルのデータに変換してn個のヒューズトリミング選択回路21にトリミング信号を

出力するシリアルパラレル変換回路と、を備えたトリミング装置2であって、ヒューズト

リミング選択回路21には、第1のヒューズ切断回路33と、第2のヒューズ切断回路3

6と、セレクタ回路50とが設けられている。第1のヒューズ切断回路33は、ヒューズ

31と切断回路であるNPNトランジスタ32とにより構成される。また第2のヒューズ

切断回路36は、ヒューズ34とNPNトランジスタ35とにより構成される。

(もっと読む)

半導体装置

【課題】不揮発性メモリに格納された内部回路の動作特性を設定するチューン情報を、メモリセル微細化時においても、電源投入後、正確かつ安定に読出す。

【解決手段】2つのメモリアレイ(1a、1b)各々のメモリセルに互いに相補なデータをチューン情報としてツインセルモードで格納する。ツインセル(TW1、TW2)は、互いに相補なチューンデータを格納するメモリセル(MCA1,MCA2,MCB1,MCB2)で構成され、2つのツインセルが同一チューン情報を格納する。チューン情報読出モード時、ダブルツインセルモードでメモリセルの選択およびデータ読出を行い、2つのツインセルの記憶情報を読出す。読出回路(5)により読出されたデータ(Q)に従って、対象回路の動作特性を設定する。

(もっと読む)

半導体装置

【課題】バラクタ・ダイオードを備える半導体装置に関し、新たな構造のバラクタ・ダイオードを提案する。

【解決手段】基板と、前記基板内に形成された第1導電型の拡散層と、前記基板内に形成され、前記拡散層に接している第2導電型のソース拡散層と、前記基板内に形成され、前記拡散層に接している第2導電型のドレイン拡散層と、前記拡散層と前記ソース拡散層とのPN接合により形成された第1のバラクタ・ダイオードと、前記拡散層と前記ドレイン拡散層とのPN接合により形成された第2のバラクタ・ダイオードと、前記ソース拡散層上に形成され、前記第1のバラクタ・ダイオード用のコンタクト配線として機能する第1のコンタクト配線と、前記ドレイン拡散層上に形成され、前記第2のバラクタ・ダイオード用のコンタクト配線として機能する第2のコンタクト配線とを備えることを特徴とする半導体装置。

(もっと読む)

発振装置の製造方法及び発振装置

【課題】発振装置の発振周波数の調整において、歩留りを向上させやすくする。

【解決手段】半導体基板7に形成された第1電極に、圧電体で構成される圧電体膜を重ねて形成し、前記圧電体膜に、前記圧電体膜を挟んで前記第1電極に対向する第2電極を形成して、前記第1電極、前記圧電体膜及び前記第2電極を構成の一部として有する第1キャパシタを形成する工程と、容器3の底となる第3基板45に、容器3の内側及び外側の間を貫通する貫通孔61が設けられた容器3内に、半導体基板7を、半導体基板7が貫通孔61を塞ぐように、且つ平面視で、前記第1キャパシタが貫通孔61に重なるように実装する工程と、前記発振回路の発振周波数を測定した結果に基づいて、半導体基板7によって塞がれた貫通孔61内に容器3の外側から圧力P1を付与した状態で、貫通孔61を容器3の外側から塞ぐ工程と、を有する。

(もっと読む)

半導体装置

【課題】電界効果トランジスタの電流コラプスの影響をより効果的に低減することが可能な半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、半導体装置100は、ゲート電圧が印加される第1の端子101にゲートが接続され、電流が入力される第2の端子102に一端(ドレイン)が接続され、接地に他端(ソース)が接続された電界効果トランジスタ(FET)103と、第1の端子101とFET103のゲートとの間の接点104に一端(アノード)が接続されるとともに接地に他端(カソード)が接続された発光ダイオード(LED)105と、接点104と接地との間に、LED105と直列に接続された抵抗106と、を備える。半導体装置100において、LED105が出力する光が少なくともFET103に照射されるように、FET103とLED105とが配置されている。

(もっと読む)

半導体装置

【課題】チップの広範囲に渡りスキューの少ないクロックを供給でき、且つ消費電力を低減できる半導体装置を提供することを目的としている。

【解決手段】半導体装置は、クロック信号を出力するドライバ14と、クロック信号を受信するレシーバ15とが集積形成された半導体チップ11と、上記半導体チップに搭載された導波管13とを備えている。上記導波管内には、上記ドライバから供給されたクロック信号を上記導波管内に送出する送信アンテナ20と、上記導波管内を伝送されたクロック信号を受信して上記レシーバに供給する受信アンテナ21とが配置されている。

(もっと読む)

MIM素子および電子装置

【課題】製造容易で費用を低減できるヒステリシス特性を有するMIM素子を提供する。

【解決手段】MIM素子は、金属窒化膜よりなる下部電極23と、前記下部電極上に形成された、Nbを含む酸化膜24よりなるヒステリシス膜と、前記ヒステリシス膜上に形成され、窒化金属膜よりなる上部電極25と、を備える。ヒステリシス膜にNbを含む酸化膜を使い、上下の電極に金属窒化物膜を使うことにより、特に上部電極のパターニングを、ヒステリシス膜に対して高い選択比で実行することが可能となり、MIM素子、およびかかるMIM素子を使った電子装置の製造を、容易に実行することが可能となる。また、上下の電極に高価なPt膜の代りに安価な金属窒化膜を使うことができ、MIM素子およびかかるMIM素子を使った電子装置の製造費用が実質的に低減される。

(もっと読む)

電子装置およびその製造方法

【課題】ヒステリシスを有するMIM素子を配列した電子装置を、高い歩留まりで製造可能とする。

【解決手段】電子装置は、基板と、前記基板上に互いに平行に第1の方向に延在するように形成されたダミーパターンと、前記ダミーパターンの相対向する第1および第2の側壁面にそれぞれ形成された第1および第2の導電性側壁膜よりなり、各々前記第1の方向に延在する一対の下部電極パターンと、前記基板上に、前記ダミーパターンおよび前記一対の下部電極パターンを覆って形成された、金属酸化物よりなるヒステリシス膜と、前記ヒステリシス膜上に、前記第1の方向とは異なる第2の方向に延在するように形成された導電膜よりなる上部電極パターンと、よりなる。

(もっと読む)

プログラマブル論理回路

【課題】配線の複雑化なく、短時間かつ容易に、論理の再構成を行う。

【解決手段】本発明の例に関わるプログラマブル論理回路は、第1の電源ノードN1と出力ノードO1との間に接続され、磁気固着層と磁気記録層の磁化方向の相対関係に応じてコンダクタンスが変化する第1のトランジスタSPと、第2の電源ノードN2と出力ノードO1との間に接続され、第1のトランジスタSPのコンダクタンスの最大値と最小値との間の値にコンダクタンスが設定される第2のトランジスタSNと、第3の電源ノードN3と出力ノードO1との間に直列接続される第3のトランジスタT1及び抵抗素子R1とを備える。入力信号A,Bを与え、かつ、第1及び第3の電源ノードN1,N2の間にスピン注入電流を流している状態で、出力ノードO1に出力される出力信号Yの検証を行う。

(もっと読む)

温度調節集積回路、温度制御加熱回路及び温度制御装置

【課題】 一定の温度になるように効率的に加熱することができ、小型化を図ることができる温度調節集積回路、温度制御型加熱回路及び水晶発振モジュールを提供する。

【解決手段】 本発明の温度調節集積回路は、温度制御加熱機能を有し、ユーザーの設定により制御信号を生成する温度調整制御手段と、前記温度調整制御手段の制御信号により所定の温度に加熱するための加熱手段とからなる。

(もっと読む)

1 - 20 / 33

[ Back to top ]