Fターム[5F038BG07]の内容

Fターム[5F038BG07]の下位に属するFターム

Fターム[5F038BG07]に分類される特許

1 - 15 / 15

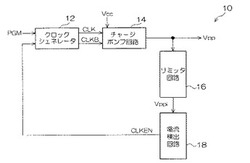

メモリ書込用電源回路

【課題】昇圧の際の消費電流を削減する。

【解決手段】チャージポンプ回路14が、クロックジェネレータ12から出力されたクロック信号CLK、CLKBに同期して動作し、電源電圧Vccを昇圧した昇圧電圧Vppを出力し、昇圧電圧の電圧値がリミッタ回路16に設定された設定電圧値Vtnを超えた場合に、リミッタ回路16が導通して昇圧電圧Vppが設定電圧値Vtnを超えないように制限し、電流検出回路18が、リミッタ回路16を流れる電流Vppiが設定電流値を超えている期間、クロック信号CLK、CLKBの出力を停止するためのローレベルの停止信号CLKENをクロックジェネレータ12へ出力する。

(もっと読む)

電圧制御回路

【課題】バイナリコードのビット数を増大させてもステップ幅ΔVPGMのばらつきが少ない電圧制御回路を提供する。

【解決手段】電圧制御回路は、ブースタと、電圧設定部とを備え、電圧設定部は、バイナリコード型設定部とサーモメータ型設定部とを含み、サーモメータ型設定部は、バイナリコード型設定部内のいずれかの抵抗素子とほぼ等しい抵抗を有する複数の抵抗素子を並列に接続した複数の抵抗体と、複数の抵抗体のそれぞれに対応しサーモメータコードにより制御される複数のトランジスタとを含み、複数の抵抗体と該抵抗体に対応する複数のトランジスタとをそれぞれ直列に接続した複数の第2の構造体を互いに並列に接続した構成を有し、サーモメータコードに応じて選択された少なくとも1つのトランジスタに接続された抵抗体に電流を流すことによって帰還抵抗に流れる電流を制御し、ブースタから出力される電圧を段階的に設定する。

(もっと読む)

半導体装置

【課題】ヒューズ素子のレイアウト面積を増大させることなく確実にヒューズを溶断するとともに、ヒューズ銅原子の拡散を防止する防護壁の配線層数を低減する。

【解決手段】ヒューズ(FU)を複数のメタル配線層のうちの上層のメタル配線層(M4)の配線を用いて形成する。ヒューズの直上および直下部においては、少なくとも2層の配線層をおいて配線が配置される。上層においては、電源電圧(VDD)を伝達する電源線(102)をヒューズ直上の防護壁構造の蓋部分として利用する。

(もっと読む)

DC−DCコンバータ

【課題】一半導体基板上で寄生構造を改良し、昇圧動作起動時に突入電流を十分に抑制でき、常時安定して昇圧動作する高性能なDC−DCコンバータを提供すること。

【解決手段】このDC−DCコンバータの場合、各昇圧用トランジスタTr5〜Tr8を形成するための各P−拡散領域部は、それらの全体を囲うように一領域部として配設されたN−ウエル領域部により素子分離されていると共に、電源電圧VDDの印加されるP−型半導体基板上の電荷伝送用トランジスタTr1、Tr3を形成するためのN−拡散領域部から電気的に遮蔽された状態となるため、電源を投入した昇圧動作起動時に各昇圧用トランジスタTr5〜Tr8の寄生バイポーラ構造に電流トリガが流れても、電源電圧VDD用入力端子と入力電圧VIN用端子との間で過大電流の流れが阻止される。

(もっと読む)

半導体装置

【課題】半導体装置において、少ないチップ部品で給電系の広帯域低インピーダンス化を実現することができる技術を提供する。

【解決手段】メモリLSI3の動作に応じて、メモリLSI3の給電系に接続された容量値可変のデカップリングコンデンサ部品5の容量値を動的に制御することにより、少ないチップ部品でメモリLSI3の給電系の広帯域低インピーダンス化を実現する。

(もっと読む)

集積回路装置、電気光学装置及び電子機器

【課題】回路の小規模化を図れ、効率的なレイアウトが可能な集積回路装置等の提供。

【解決手段】集積回路装置10は、第1の方向(D1)に沿って配置される第1〜第Nのデータドライバブロックを含み、第1〜第Nのデータドライバブロックの各データドライバブロックは、第1〜第Mのサブドライバブロック(SDB0〜SDB5)を含む。各サブドライバブロック(SDB0)は、画像データ(ID0)を受け、画像データのD/A変換を行うD/A変換回路(DAC0)と、D/A変換回路の第2の方向(D2)において第1の方向に沿って配置され、D/A変換回路を共用する第1〜第Lのデータ線駆動回路(GR0、GG0、GB0)を含む。

(もっと読む)

メモリの動的電圧調整

集積回路(10)上のメモリ(14)のための電力供給電圧は、メモリを作動する間、動的に調整される。メモリを作動することは、供給電圧(VDD1)でメモリに給電することを含む。メモリの作動中、集積回路のテストメモリ(16)は並行して電力を供給される。テストメモリおよびメモリは、各々第1のビットセル構成タイプのビットセルを含む。テストメモリのテストに基づいてメモリを作動させながら、供給電圧の電圧レベルが、調整される(30)。電圧レベルが、メモリの失敗した作動を保証しないだけでなく、供給電圧を正確に最小化した値とみなすように、外部の変化によって調整される。システム及び方法は、いかなる種類ものメモリでも実装されうる。メモリ(14)およびテストメモリ(16)は、分離されるか、または、集積回路上に散在して物理的に実装されうる。  (もっと読む)

(もっと読む)

昇圧電源回路

【課題】負荷状態に関係なく一定周期でチャージポンプの昇圧動作を行う。

【解決手段】チャージポンプ10を制御するレギュレータ30は、昇圧クロックの2倍周期の分周クロックを生成する分周回路31、電圧値が異なる複数の分圧電圧を生成する分圧回路33、それぞれの分圧電圧と基準電圧とを比較し、複数の比較結果信号を出力する比較回路34、分周クロックのエッジに同期して各比較結果信号の論理を読み込み、選択信号を出力する選択信号生成回路35、オンデューティが異なる複数のクロックを出力するDUTY変換回路32、選択信号に基づいて複数のクロックのいづれかまたは"H"レベルの論理をPWM信号として選択するセレクタ36、および分周クロックとPWM信号とを論理積して直並列切換の制御信号を生成するゲート回路37を有する。

(もっと読む)

半導体装置

【課題】パッケージング後であっても、端子容量を調整することができる半導体装置を提供する。

【解決手段】入出力回路10は、外部ピンと初段回路(入力バッファ200又は入出力バッファ300)間の信号配線に接続された端子容量調整回路100を備え、入力された命令をデコードし端子容量の調整のコマンドを検出するコマンドデコーダ20と、端子容量を制御するための情報を保持する端子容量調整レジスタ400を有し端子容量調整レジスタ400の情報を基に、端子容量調整回路100の容量値を制御する端子容量制御回路30を備え、コマンドデコーダ20からの出力に基づき、端子容量調整レジスタ400で保持する前記情報が設定される。

(もっと読む)

集積回路装置及び電子機器

【課題】 スリムな細長の集積回路装置及びこれを含む電子機器の提供。

【解決手段】集積回路装置10は、第1及び第2の電源線の間にプッシュプル接続され、チャージポンプ動作によりその接続ノードNDに第1及び第2の電源線のいずれかの電圧を出力するための第1及び第2のトランジスタNTr1、PTr1と、接続ノードNDと電気的に接続されると共に、その一端に所与の電圧が印加されるフライングコンデンサの他端と電気的に接続されるパッドPDとを含む。第1及び第2のトランジスタNTr1、PTr1の少なくとも一方の一部又は全部と重なるように、該第1及び第2のトランジスタNTr1、PTr1の少なくとも一方の上層にパッドPDが配置される。

(もっと読む)

半導体集積回路装置

【課題】 低電力で動作する半導体集積回路装置を提供する。

【解決手段】 半導体集積回路装置は、論理ブロックと、論理ブロックに供給される電力を制御する電力制御回路と、を含み、電力制御回路は、データ保持モード時に論理ブロックに格納されたデータを保持するのに必要な最小の動作電圧を供給するように構成される。

(もっと読む)

半導体集積回路およびそれを備えた電子機器

【課題】広範囲の検出結果を得ることが可能な半導体集積回路およびそれを備えた電子機器を提供する。

【解決手段】半導体集積回路101は、検出素子X1の検出結果に基づいて検出素子X1に電流を出力する第1のトランジスタM1と、第1のトランジスタM1の出力電流のn倍の電流を出力する第2のトランジスタM2と、検出素子X1から受けた電流を検出信号として出力するか、あるいは第2のトランジスタM2から受けた電流を検出信号として出力するかを切り替える切り替え回路SW1とを備える。但し、nは0<n<1または1<nを満たす実数である。

(もっと読む)

半導体集積回路および半導体集積回路の製造方法

【課題】 多様な機能を搭載する低消費電力型の半導体集積回路を提供すること。

【解決手段】 半導体集積回路の一例として、システムLSI1は、クリティカルパスを含まない第一回路ブロック41〜48と、前記クリティカルパスを含む第二回路ブロック51〜54と、第一回路ブロック41〜48に第一電源を供給する第一電源配線25と、第二回路ブロック51〜54に前記第一電源に比べて高電圧の第二電源を供給する第二電源配線26と備え、第二回路ブロック51〜54それぞれは、配線領域61〜64によって第二電源配線26と接続され、第二電源が供給される。

(もっと読む)

リーク管理システム及びシステム、方法、適応型リーク制御装置、負電圧調整器、チャージポンプ

集積回路の静的リークを最小化するため、チャージポンプは、前記集積回路の論理ゲートと縦続接続された「スリープ」トランジスターに印加されるべき負電圧を生成する。適応型リーク制御部は、負電圧を調整し静的リークを最小化するかどうかを連続的又は周期的に決定する。負電圧調整器は、負電圧を当該決定に従い調整する。いくつかの実施例は、前記スリープトランジスターの1つ以上のパラメーターを監視することにより、負電圧を調整するかどうかを決定する。いくつかの実施例は、エミュレートされたスリープトランジスターの1つ以上のパラメーターを監視することにより、負電圧を調整するかどうかを決定する。  (もっと読む)

(もっと読む)

ツェナー−ザップメモリ

本発明は、NPNトランジスタを通過する電流を駆動することにより、集積回路内に情報を電気的に、かつ永久的にプログラムするための集積回路に関する。この集積回路は、抵抗器を介して前記NPNトランジスタに接続された出力端、第1供給電圧に接続可能な供給ポイントおよび前記NPNトランジスタのプログラミングを制御するための制御入力端を有する第1電流供給回路を備える。更にこの集積回路は前記第1電流供給回路の供給ポイントに接続された出力端と、供給電圧に接続可能な供給ポイントと、前記NPNトランジスタのプログラミングを制御するための制御入力端を有する少なくとも1つの第2電流供給回路を備える。最後にこの集積回路は、前記NPNトランジスタをプログラムするのに必要な電圧を前記第1電流供給回路と少なくとも第2電流供給回路の両端に分割するよう設けられた第1電圧レベルコントローラを備える。  (もっと読む)

(もっと読む)

1 - 15 / 15

[ Back to top ]