Fターム[5F038BG08]の内容

Fターム[5F038BG08]に分類される特許

1 - 20 / 58

半導体装置

【課題】昇圧効率を向上させた昇圧回路を提供することを課題の一とする。または、昇圧効率を向上させた昇圧回路を用いたRFIDタグを提供することを課題の一とする。

【解決手段】単位昇圧回路の出力端子に当たるノード、または当該ノードに接続されたトランジスタのゲート電極をブートストラップ動作により昇圧することで、当該トランジスタにおけるしきい値電位と同等の電位の低下を防ぎ、当該単位昇圧回路の出力電位の低下を防ぐことができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】チップ面積を削減することのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施形態に係る不揮発性半導体記憶装置は、半導体基板と、半導体基板上に積層され、垂直方向に直列接続された複数のメモリセルを含むメモリセルアレイと、半導体基板上に設けられ、所望の電圧をメモリセルアレイに供給する電源回路とを備える。電源回路は、電圧を生成するポンプ回路と、ポンプ回路の出力端子に接続され、出力端子の電圧値が所定の値を下回った場合にポンプ回路へ制御信号を出力するリミッタ回路と、出力端子に一端が接続され、出力端子の電圧を調整するように構成されたキャパシタと、キャパシタの他端に接続され、制御信号に基づき所定の電流値の定電流を用いてキャパシタを充電するブースト回路と、ブースト回路の充電動作を停止させるスイッチとを備える。キャパシタは、メモリセルアレイの直下に設けられる。

(もっと読む)

昇圧回路を備えた半導体装置

【課題】回路面積を縮小でき、昇圧効率の高い昇圧回路を備える半導体装置を提供する。

【解決手段】出力電圧を監視するモニタ電圧MON1に基づいて、出力電圧を所定電圧に制御する制御回路と、出力電圧を通常動作時に第1電圧に設定し、評価時に第1電圧より高い第2電圧に設定するトランジスタTR4,TR5と、出力電圧の振幅をクロック信号の振幅としてクロック信号を発生するクロックドライバ11と、コンデンサ及びダイオードを含む単位回路21が直列に複数段接続され、コンデンサに入力されるクロック信号により電源電圧VCCを昇圧するチャージポンプ12とを備える。

(もっと読む)

半導体集積回路

【課題】不揮発性メモリを搭載した半導体集積回路において、外部端子を通して不揮発性メモリの特性テストを実施し、更に、その外部端子にサージ電圧が印加された場合であっても、そのサージ電圧が不揮発性メモリに伝わることを防止する。

【解決手段】半導体集積回路は、不揮発性メモリと、不揮発性メモリに対するデータ書き込み時、書き込み電圧が印加される書き込み制御線と、書き込み制御線に接続された第1ノードと、第1スイッチ回路を介して第1ノードに接続された外部端子と、スイッチ回路を介さずに外部端子に接続された第1ESD保護回路と、動作モードに応じて第1スイッチ回路をON/OFF制御する制御回路と、を備える。動作モードは、外部端子を用いて不揮発性メモリの特性テストを行うテストモードと、外部端子を使用しないユーザモードと、を含む。テストモードにおいて、制御回路は、第1スイッチ回路をONする。ユーザモードにおいて、制御回路は、第1スイッチ回路をOFFする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体集積回路内の抵抗素子の抵抗値のばらつきを抑制した半導体装置を提供する。

【解決手段】半導体装置は基板を備える。第1の絶縁膜は基板上に設けられる。第1の抵抗部は第1の絶縁膜上に設けられる。境界膜は第1の抵抗部上に設けられる。第2の抵抗部は境界膜上に設けられる。第2の絶縁膜は、第2の抵抗部上に設けられている。第1の導電部および第2の導電部は、第2の絶縁膜上に設けられ、互いに絶縁されている。第1の導電部は、第2の絶縁膜および第2の抵抗部を貫通して境界膜の表面に接触する第1のコネクト部を含む。第2の導電部は、第2の絶縁膜および第2の抵抗部を貫通して境界膜の表面に接触する第2のコネクト部を含む。第1の抵抗部は、一端において第1のコネクト部を介して第1の導電部に電気的に接続され、かつ、他端において第2のコネクト部を介して第2の導電部に電気的に接続された抵抗素子である。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体装置の小型化を図ること。

【解決手段】第1の領域IにフラッシュメモリセルFLを形成する工程と、第2の領域IIにキャパシタQの第1の電極11aを形成する工程と、第2の絶縁膜14として第1の酸化シリコン膜14a、窒化シリコン膜14b、及び第2の酸化シリコン膜14cをこの順に形成する工程と、第1の電極11aの一部領域CRにおける窒化シリコン膜14bと第2の酸化シリコン膜14cとを除去する工程と、第3の領域IIIHにおける第1の絶縁膜10と第2の絶縁膜14とをウエットエッチングする工程と、キャパシタQの第2の電極30aを形成する工程と、一部領域CRにおける第1の酸化シリコン膜14aをエッチングして除去する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置

【課題】キャパシタを形成する領域の占有面積を縮小する。

【解決手段】本実施形態の半導体装置は、半導体基板10内に設けられた半導体領域AACと、半導体領域AAC内に設けられる複数のキャパシタCm,Cnを含むキャパシタ群と、を具備し、キャパシタCm,Cnのそれぞれは、半導体領域AAC上のキャパシタ絶縁膜42Aと、キャパシタ絶縁膜42A上のキャパシタ電極34Am,34Amと、キャパシタ電極34Am,34Amに隣接する拡散層32Aとを有し、を有し、キャパシタ電極34Am,34Anに接続される配線29m,29nのそれぞれは、キャパシタCm,Cn毎に電気的に分離され、キャパシタ電極Cm,Cnのそれぞれに異なる電位Vm,Vnが印加されている。

(もっと読む)

チャージポンプ回路、不揮発性メモリ、データ処理装置、及びマイクロコンピュータ応用システム

【課題】複数の容量を互いに直列接続して一つの昇圧容量を形成した場合の中間ノードの帯電に起因するデバイス破壊を回避するとともに、当該中間ノードのリークパスを介して流れるリーク電流に起因するポンプ効率の低下を回避する。

【解決手段】チャージポンプ回路(1307)は、第1静電容量(Ca)とそれに直列接続された第2静電容量(Cb)とを含む昇圧容量(C(x−1),Cx)と、容量ドライバ(DRV(x−1),DRVx)と、保護回路(D1,D2)とを含む。上記保護回路は、上記昇圧電圧が形成されない状態においては導通状態とされて、上記第1静電容量と上記第2静電容量との直列接続ノードの蓄積電荷を放電し、上記昇圧電圧が形成される状態においては非導通状態を維持する。これにより、昇圧容量の耐圧緩和を図り、また、ポンプ効率の低下を回避する。

(もっと読む)

半導体装置

【課題】外部装置を駆動する駆動回路が形成されたチップの面積の増加を抑制することができる半導体装置を提供する。

【解決手段】フラッシュメモリ22がリード動作を実行する場合は、セレクタ26は、ロジック回路30から入力された選択信号SELに応じて基準電圧VREF1を選択する。VLCD昇圧回路28は、基準電圧VREF1を昇圧した駆動電圧VLCDをLCDパネルドライバ12に出力する。また、フラッシュメモリ22は、電源電圧VDDの供給のみでリード動作を実行する。プログラム動作またはイレース動作を実行する場合は、セレクタ26は、選択信号SELに応じて基準電圧VREF2を選択する。VLCD昇圧回路28は、基準電圧VREF2を昇圧した電圧VPPをフラッシュメモリ22に出力する。フラッシュメモリ22は、電圧VPPの供給を受け、プログラム動作またはイレース動作を実行する。

(もっと読む)

半導体集積回路装置

【課題】消費電力を低減することができる半導体集積回路装置の提供を図る。

【解決手段】入力電圧vddを昇圧し、出力電圧vhを出力する昇圧回路1と、前記昇圧回路から出力される前記出力電圧を検出し、動作モードに応じて複数の異なる電圧を、前記昇圧回路から発生させるように制御する検出器3と、を有するように構成する。

(もっと読む)

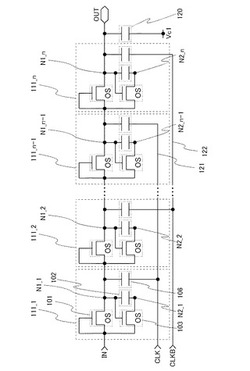

昇圧回路及び昇圧回路を用いたRFIDタグ

【課題】昇圧効率を向上させた昇圧回路を提供することを課題の一とする。または、昇圧効率を向上させた昇圧回路を用いたRFIDタグを提供することを課題の一とする。

【解決手段】単位昇圧回路の出力端子に当たるノード、または当該ノードに接続されたトランジスタのゲート電極をブートストラップ動作により昇圧することで、当該トランジスタにおけるしきい値電位と同等の電位の低下を防ぎ、当該単位昇圧回路の出力電位の低下を防ぐことができる。

(もっと読む)

電源電圧生成回路、及び半導体装置

【課題】外部から供給される電源の電圧に幅がある場合であっても、小さな面積で、リップルノイズを低減する電源電圧生成回路及び半導体装置を提供する。

【解決手段】第1の内部電源電圧を生成する第1のチャージポンプ回路と、第1の内部電源電圧よりも電圧値が大きい第2の内部電源電圧を生成する第2のチャージポンプ回路と、を備え、少なくとも第2のチャージポンプ回路の出力側である2次側の充電端子に第1のチャージポンプ回路の出力端子が接続され、第2のチャージポンプ回路の出力電圧は、第1の内部電源電圧の値から所定電圧値が加算された電圧値を出力する。

(もっと読む)

昇圧回路

【課題】従来の昇圧回路は、低耐圧トランジスタにより構成することができなかった。

【解決手段】本発明は、第1の電源電圧を昇圧する昇圧回路であって、第1のノードに接続される第1のトランジスタと、一端が第1のノードに接続され、第1のトランジスタの活性化時に第1のノードの電圧で充電される第1の容量素子と、第1のトランジスタの制御端子に第1の制御信号を出力する第1の制御信号生成回路を有し、第1の容量素子は、第1のトランジスタの非活性化時に、他端に印加される第1の電源電圧の1/2以下の電圧により第1のノードの電位を、第2の電圧に昇圧し、第1の制御信号生成回路は、第1のトランジスタの非活性化時の第1の制御信号の電位を、第2の電位とし、第1のトランジスタの活性化時の第1の制御信号の電位を、第2の電位との差が第1の電源電圧以内となる電位とする昇圧回路である。

(もっと読む)

チャージポンプ回路及び方法

【課題】回路に必要とされる基板面積を小さくする。

【解決手段】チャージポンプ回路及びその作動方法が記載されている。それぞれのステージの切り替え用デバイスが、第1と第2のノードのうちの一方を交互に充電し、その間他方のノードを放電させる。昇圧回路が、前記第1と第2のノードのうち放電させる側のノードの電位を昇圧する。ステージ(n)の第1のノードは、ステージ(n+1)の第1のノードへ放電する。1つの実施形態では、トリプルウェル・トライチャネル・パイプライン型チャージポンプが記載されている。

(もっと読む)

昇圧回路

【課題】昇圧回路の回路規模を小さくする。

【解決手段】昇圧動作終了後にリセットトランジスタM3がノードVgをリセットする場合、電源電圧によってリセットトランジスタM3が制御され、ノードVgがリセットされるので、リセットするための新たな昇圧電圧は不必要であり、これに伴う別の昇圧回路も不必要である。よって、その分、昇圧回路の回路規模が小さくなる。

(もっと読む)

内部電圧発生回路

【課題】安定に所望の補償範囲を有する温度補償された内部電圧を制御性よく生成する。

【解決手段】温度依存性を有しない参照電圧(VOUT16)から温度依存性を有する基準電圧(VREF16)を温度特性付加回路(10)により生成する。この基準電圧をアナログ/デジタル変換し、そのアナログ/デジタル変換値を内部電圧のレベルを規定する基準コード情報(TN_VREF<4:0>)と加算する。この加算値(TN_VREF2<4:0>)をデジタル/アナログ変換して温度依存性を有するオフセット電圧(Vrefos)を生成する。このオフセット電圧に基づいて、必要なレベルの内部電圧(VCPP)を生成する。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】不揮発性記憶素子と、容量素子若しくは抵抗素子とを有するシステムICの製造方法を提供する。

【解決手段】半導体基板の主面の素子分離領域5上に下部電極10cが設けられ、かつ下部電極10c上にONO膜11,12,13からなる誘電体膜を介在して上部電極19cが設けられた容量素子Cを有する半導体集積回路装置であって、半導体基板の主面の素子分離領域5と下部電極10cとの間に耐酸化性膜8、及び下部電極10cと上部電極19cとの間に耐酸化性膜12を有する。

(もっと読む)

半導体記憶装置

【課題】配線層を多層化することなく、第3配線層がユニットセルや基本セルの配線に使用できない領域にゲートアレイを配置して、該領域を有効利用することできる半導体記憶装置を提供する。

【解決手段】積層された3つの配線層を有する半導体記憶装置であって、メモリアレイ領域を第1配線層、第2配線層、及び第3配線層を複数のメモリセルの配線に用いることが可能な領域に形成し、第1配線層、第2配線層、及び第3配線層を複数の基本セルの配線に用いることが可能な領域に第1のゲートアレイ領域を形成し、第1及び第2配線層の2つの配線層を複数のユニットセルの配線に用いることが可能な領域に第2のゲートアレイ領域を形成すると共に、第2のゲートアレイ領域の複数の基本セルを、第3配線層を用いて配設すべき配線を第1配線層を用いて配設するために必要な間隔を隔てて配列する。

(もっと読む)

電圧生成回路及びその動作制御方法

【課題】従来の電圧生成回路は出力電圧のリップルを十分に抑制することができなかった。

【解決手段】本発明の電圧生成回路は、出力端子OUTに対して出力電圧を出力する複数の昇圧回路10〜13と、出力電圧をモニタし、予め定められた電圧範囲を超える出力電圧を検出して検出信号DNを出力する電圧検出部30aと、活性化させる昇圧回路の個数を記憶するレジスタを含み、検出信号DNに応じてレジスタに保持された値を更新し、レジスタに保持された値に応じた個数の昇圧回路に対して活性化指示を与える制御回路20aと、を有するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセルトランジスタに所定の電圧を供給するための効果的な手法を提供する。

【解決手段】基板と、前記基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された第1ゲート電極と、前記第1ゲート電極を挟むように前記基板内に形成されたソース・ドレイン領域と、前記第1ゲート電極上に形成され、開口を有するゲート間絶縁膜と、前記ゲート間絶縁膜上に形成され、前記開口を通じて前記第1ゲート電極と電気的に接続されている第2ゲート電極と、前記ゲート間絶縁膜上に形成され、前記第1ゲート電極及び前記第2ゲート電極と電気的に分離されているブースト電極とを備えることを特徴とする半導体装置。

(もっと読む)

1 - 20 / 58

[ Back to top ]