Fターム[5F038BG09]の内容

Fターム[5F038BG09]に分類される特許

1 - 20 / 261

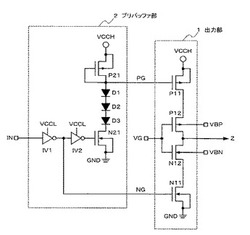

半導体装置

出力回路

【課題】高電圧信号を出力する回路を低耐圧トランジスタで構成しても、信頼性を向上させることのできる出力回路を提供する。

【解決手段】実施形態の出力回路は、出力部1が、高電圧電源端子VCCHと出力端子とZの間に接続されPMOSトランジスタP11、P12と、接地電位端子GNDと出力端子Zとの間に接続されたNMOSトランジスタN11、N12とを有し、低電圧入力信号INが入力されるプリバッファ部2が、PMOSトランジスタP11、NMOSトランジスタN11へ、VCCHよりも小さい振幅のゲート電圧PG、NGを出力する。PMOSトランジスタP12およびNMOSトランジスタN12のゲート端子へVCCHよりも低い定電圧VGが印加され、PMOSトランジスタP12の基板へVCCHよりも低い基板バイアス電圧VBPが印加され、NMOSトランジスタN12の基板へ接地電位よりも高い基板バイアス電圧VBNが印加される。

(もっと読む)

半導体装置及びアナログスイッチの制御方法

【課題】高い電圧を有する入力信号に対して適切に動作するアナログスイッチを有する半導体装置を提供する。

【解決手段】入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチと,入力端子に印加される入力電圧に応じて,Pチャネルトランジスタの第1ゲート電圧及び第1バックゲート電圧と,Nチャネルトランジスタの第2ゲート電圧及び第2バックゲート電圧とのそれぞれの電位を可変生成する可変電圧回路と,アナログスイッチを導通または非導通に制御する制御信号を可変電圧回路に供給する制御回路とを有する。可変電圧回路は,導通に制御する制御信号に応答して,可変生成される第1ゲート電圧と第2ゲート電圧とをPチャネルトランジスタとNチャネルトランジスタのゲートにそれぞれ出力する。

(もっと読む)

半導体装置

【課題】電源線と機能回路の間に電源スイッチとして接続されるMOSトランジスタのオン時のバックゲートの電圧を簡単な構造で調整することができる半導体装置を提供する。

【解決手段】一対の電源線2、3と、機能回路4a0〜4anと、一対の電源線2、3との少なくとも一方と機能回路4a0〜4anの間に接続されるスイッチング回路6a0〜6an、7a0〜7anとを有し、スイッチング回路6a0〜6an、7a0〜7anは、ソース/ドレインの一方が機能回路4a0〜4anに接続され、他方が前記一対の電源線2、3の一方に接続される第1のMOSトランジス11と、第1のMOSトランジスタ11のゲートとバックゲートを接続する抵抗素子12、21と、第1のMOSトランジスタ11のゲートに接続されるゲート電圧制御回路13と、を有する。

(もっと読む)

フィールドプログラマブルゲートアレイの性能を向上させるための装置および関連方法

【課題】性能が向上されたフィールドプログラマブルゲートアレイ(FPGA)を提供する。

【解決手段】フィールドプログラマブルゲートアレイ(FPGA)103であって、該FPGAは、該FPGA内の少なくとも1つの回路に対するプロセス、電圧、および温度の表示を提供するように適合された監視回路のセット115と、該少なくとも1つの回路に対するプロセス、電圧、および温度の該表示から該少なくとも1つの回路に対するボディバイアス値の範囲を導出するように適合されたコントローラ140と、該少なくとも1つの回路内の少なくとも1つのトランジスターにボディバイアス信号を提供するように適合されたボディバイアス生成器とを含み、該ボディバイアス信号は、該ボディバイアス値の範囲内の値を有する。

(もっと読む)

半導体装置及び分圧回路

【課題】複数の抵抗の変化率差を抑制すること。

【解決手段】分圧回路11は、直列接続された2つの抵抗R1,R2を有している。第1の抵抗R1は、入力電圧Vinを供給する配線21と出力ノードN1との間に接続されている。第2の抵抗R2は、基準電圧Vsを供給する配線22と出力ノードN1との間に接続されている。第1の抵抗R1は、P型の半導体基板に形成されたN型のウェル領域(基板領域)31と、このウェル領域31に形成されたP型の拡散領域33を含む。第2の抵抗R2は、P型の半導体基板に形成されたN型のウェル領域32と、このウェル領域32に形成されたP型の拡散領域34を含む。第1のウェル領域31には、入力電圧Vinが供給される。第2のウェル領域32は、第1の拡散領域33に設定された分圧ノードNdと接続されている。

(もっと読む)

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】チップ面積を削減することのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施形態に係る不揮発性半導体記憶装置は、半導体基板と、半導体基板上に積層され、垂直方向に直列接続された複数のメモリセルを含むメモリセルアレイと、半導体基板上に設けられ、所望の電圧をメモリセルアレイに供給する電源回路とを備える。電源回路は、電圧を生成するポンプ回路と、ポンプ回路の出力端子に接続され、出力端子の電圧値が所定の値を下回った場合にポンプ回路へ制御信号を出力するリミッタ回路と、出力端子に一端が接続され、出力端子の電圧を調整するように構成されたキャパシタと、キャパシタの他端に接続され、制御信号に基づき所定の電流値の定電流を用いてキャパシタを充電するブースト回路と、ブースト回路の充電動作を停止させるスイッチとを備える。キャパシタは、メモリセルアレイの直下に設けられる。

(もっと読む)

電源電圧判定回路

【課題】外部電源電圧の規格が異なるSDRAMの設計を共通化しつつ、該SDRAMの消費電流の増大を抑制できる電源電圧判定回路を提供する。

【解決手段】第1外部電源電圧と第2外部電源電圧間の電位差に比例する比例電圧と所定の一定電圧とを比較し、該比較結果を基に第1外部電源電圧がしきい値よりも低いとき、Pch基板電位設定回路は第1外部電源電圧をPチャネルトランジスタの基板へ供給し、Nch基板電位設定回路は第2外部電源電圧をNチャネルトランジスタの基板へ供給する。また、第1外部電源電圧がしきい値以上であるとき、Pch基板電位設定回路は第1外部電源電圧よりも高い電圧をPチャネルトランジスタの基板へ供給し、Nch基板電位設定回路は、第2外部電源電圧よりも低い電圧をNチャネルトランジスタの基板へ供給する。

(もっと読む)

チャージポンプ回路

【課題】寄生トランジスタが発生する場合であっても、目的レベルの出力電圧を生成できるチャージポンプ回路を提供する。

【解決手段】入力電圧に応じた出力電圧を生成するチャージポンプ回路は、入力電圧を積分した積分電圧を出力する積分回路と、積分電圧が印加される入力電極及び基板電極を有するNMOSトランジスタと、NMOSトランジスタに直列接続され、NMOSトランジスタと相補的にオンオフされるPMOSトランジスタと、NMOSトランジスタがオンされている場合に、クロック信号に基づいて充電され、PMOSトランジスタがオンされている場合に、クロック信号に基づいて放電される第1コンデンサと、PMOSトランジスタがオンされている場合に第1コンデンサから放電された電荷が充電され、出力電圧を生成する第2コンデンサと、を備えることを特徴とするチャージポンプ回路。

(もっと読む)

半導体装置

【課題】複数のフローティング領域の間の電位差の不均一を軽減することができる半導体装置を提供する。

【解決手段】半導体装置は、領域3(k)と領域3(k+1)間に、外部容量6(k)を備えている。複数の外部容量6(k)は、その容量がkの増加とともに(即ち、図1の紙面右側から紙面左側に向かうほど)大きくなるように選定されている。この構造により、領域3(k)と領域3(k+1)間の電位差の不均一を軽減することができる。

(もっと読む)

半導体集積回路装置

【課題】メーカーの設計負担を増加させることなくセルタイプの異なるICを実現することができるとともに、チップサイズおよび消費電力並びに動作速度が最適化された半導体集積回路を容易に実現可能な設計技術を提供する。

【解決手段】所望の機能を有する回路セルの設計情報を目的別にオブジェクトとして記述し、所定のオブジェクトの情報の削除もしくは追加のみで基体電位固定型セルと基体電位可変型セルのいずれをも構成可能なセル情報として、セルライブラリに登録するようにした。

(もっと読む)

単一のプロセスを用いて高性能ロジックおよびアナログ回路をイネーブルするプロセス/設計方法論

【課題】混合信号プロセスにおいてアナログ回路の性能を向上させる方法および装置を提供すること

【解決手段】順方向バイアスおよび修正された混合信号プロセスを用いた回路設計を用いて、アナログ回路性能を向上させる方法が提示される。複数のNMOSトランジスタおよびPMOSトランジスタを含む回路が規定される。NMOSトランジスタのボディ端子は、第1の電圧ソースに連結され、PMOSトランジスタのボディ端子は、第2の電圧ソースに連結される。回路内のトランジスタは、各選択されたNMOSトランジスタのボディ端子に該第1の電圧ソースを適用することと、各選択されたPMOSトランジスタのボディ端子に該第2の電圧ソースを適用することとによって、選択的にバイアスされる。一実施形態において、第1の電圧ソースおよび第2の電圧ソースは、順方向バイアスおよび逆方向バイアスをトランジスタのボディ端子に提供するように修正可能である。

(もっと読む)

半導体装置

【課題】電界効果型トランジスタのLSI製造後にしきい電圧の制御が可能で、かつ、回路面積を増大させず、かつ信頼性に優れるという特徴を有する技術を提供する。

【解決手段】シリコン半導体支持基板1の上面に設けられた積層膜(3nm以上4nm以下の第1のシリコン酸化膜2/0.3nm以上2nm以下のシリコン窒化膜3/5nm以上10nm以下の第2のシリコン酸化膜4/3nm以上20nm以下の膜厚)を有するSOI層5と、上記構造に所定の間隔を介して互いに対向して設けられたソース・ドレイン拡散層6と、当該ソース拡散層とドレイン拡散層の間の上記半導体基板の表面上に形成されたゲート絶縁膜7と、上記ゲート絶縁膜の上に形成されたゲート電極8を具備してなる電界効果型半導体装置において、シリコン支持基板1から電圧を印加することにより、直接トンネル効果によって電荷をシリコン窒化膜3に一定時間保持してしきい電圧を調整する。

(もっと読む)

半導体集積回路

【課題】外部電源電圧を降圧するレギュレータを内蔵することによるチップ面積の増大を抑え且つ降圧電圧の安定化を実現できる半導体集積回路を提供する。

【解決手段】外部電源電圧(Vext)よりも低い内部電源電圧(Vint)で動作する内部回路を持つ半導体集積回路において、内部電源電圧を生成するレギュレータ(150〜157)を、バッファ及び保護素子を配置するための第2の領域(2)に配置することにより、降圧電源回路のオンチップ化による面積オーバヘッドを低減する。降圧電圧を伝達するループ状の電源幹線(L20)を用い、電源幹線に外付け安定化容量を接続するための電極パッドを設ける等により、低消費電力を更に促進する。

(もっと読む)

トランスコンダクタンスアンプ及びそれを用いたGm−Cフィルタ

【課題】線形性能が優れたGmアンプ、このGmアンプを用いて高速動作が可能で、入力電圧範囲が広く、かつ線形性能の優れたGm−Cフィルタを提供する。

【解決手段】入力信号が端子17、18から供給され、ソース端子が電源端子に接続されるMOSトランジスタ11、12、同相制御信号がゲート端子から供給されるMOSトランジスタ13、14、出力信号を出力する出力端子対の平均電圧を一定にするためMOSトランジスタ13、14のゲート端子に同相制御信号を出力する同相制御アンプ15、入力信号を入力して、MOSトランジスタ11、12に入力される入力信号の大小に応じて基板電圧を制御する基板制御信号をMOSトランジスタ11、12の基板端子に供給する基板電圧制御回路21、22によってGmアンプを構成する。

(もっと読む)

制御電圧生成回路、定電流源回路及びそれらを有する遅延回路、論理回路

【課題】回路規模を増大させることなくトランジスタの閾値電圧に応じた制御電圧を精度良く生成することが可能な制御電圧生成回路を提供すること。

【解決手段】本発明にかかる制御電圧生成回路は、高電位側電源と低電位側電源との間に直列に接続された同一導電型の複数のMOSトランジスタを有し、何れかのMOSトランジスタのドレイン電圧を参照電圧Vp1として生成する参照電圧生成部11と、高電位側電源と低電位側電源との間に直列に接続され参照電圧生成部11と同一導電型の複数のMOSトランジスタを有し、何れかのMOSトランジスタのゲートに参照電圧が供給され、何れかのMOSトランジスタのドレイン電圧を制御電圧(バイアス電圧)として出力する電圧変換部12と、を備える。

(もっと読む)

昇圧回路およびブーストコンバータ

【課題】電力の消費を抑制すると共に供給された電圧をより適正に昇圧する。

【解決手段】トランジスタ回路14a,14bのトランジスタTr1,Tr3の半導体基板20には、それぞれトランジスタ回路14b,14cのドレイン接続端子Td2からの電圧V2,V3を順に印加し、トランジスタ回路14cのトランジスタTr1,Tr3の半導体基板20には、トランジスタ回路14cのドレイン接続端子Td2からの電圧V3を印加し、トランジスタ回路14b,トランジスタ回路14cのトランジスタTr2,Tr4のウェル30には、トランジスタ回路14a,14bのドレイン接続端子Tr1からの電圧V0,V1を順に印加する。これにより、電力の消費を抑制すると共に供給された電圧をより適正に昇圧することができる。

(もっと読む)

半導体集積回路

【課題】 電源ノイズを緩和しながら、内部回路が動作を開始するまでの時間を短縮する。

【解決手段】 内部回路は、基板電圧が供給されるトランジスタを含み、内部電源電圧を受けて動作する。電源スイッチは、内部回路を動作させるための電源オン信号の活性化中に外部電源線を内部電源線に接続する。基板電圧制御回路は、電源オン信号の活性化により上昇する内部電源電圧が目標電圧を超えたときに、基板電圧を第1電圧から第2電圧に変更する。第1電圧を基板電圧として受けているトランジスタのソース・ドレイン間電流は、第2電圧を基板電圧として受けているトランジスタのソース・ドレイン間電流より少ない。このため、電源スイッチがオンした後、内部電源電圧が低い期間にトランジスタのソース・ドレイン間電流を少なくでき、内部回路を流れる貫通電流を少なくできる。

(もっと読む)

スイッチ回路装置

【課題】従来技術によるスイッチ回路装置では、ドライバ回路がアンテナ端子とポートとの間に振幅の大きい高周波信号を入力した際に、ドライバ回路内部でリーク電流が発生し、スイッチ回路装置の消費電力が増大する、という問題がある。

【解決手段】ドライバ回路の出力部に、リーク電流抑制回路部を設ける。本発明のスイッチ回路装置によれば、リーク電流抑制回路部が高周波信号の侵入を抑制するので、ドライバ回路は出力状態を保持することが出来て、リーク電流の問題が解決される。

(もっと読む)

1 - 20 / 261

[ Back to top ]