Fターム[5F038CA17]の内容

Fターム[5F038CA17]に分類される特許

1 - 20 / 448

半導体装置

半導体集積回路の製造方法

【課題】常時動作領域と電源遮断可能領域とが混在する半導体集積回路を提供する。

【解決手段】半導体基板に設けられ、複数の基本セル(10)の配置が可能なセル配置領域と、空間的に前記セル配置領域と重なって設けられた基本電源配線(11)と、前記基本電源配線(11)から前記セル配置領域への電源供給を停止するスイッチセル(6)と、前記スイッチセル(6)に隣接して前記セル配置領域に配置され、前記スイッチセル(6)が前記セル配置領域への電源供給を停止した場合においても、前記スイッチセル(6)から電源供給を受ける常時動作セル(5)とを具備する。

(もっと読む)

半導体集積回路及びその設計方法

【課題】チップサイズを増大することなく、キャパシタの容量を増やすことができる半導体集積回路を提供する。

【解決手段】半導体基板10上にメインブロック11と周辺ブロック12とが混載された半導体集積回路において、半導体基板10上のメインブロック11に形成され、第1のトレンチキャパシタを有するメイン回路と、半導体基板10上の周辺ブロック12に形成され、第2のトレンチキャパシタを有するアナログ回路とを備える。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法及び設計装置並びにプログラム

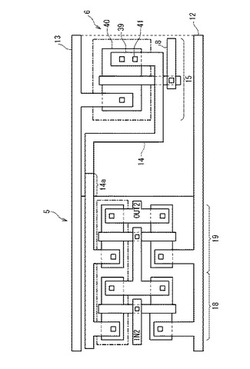

【課題】セルベースの半導体集積回路において、異なるセル高さを有するセルを効率良く配置するための技術を提供する。

【解決手段】半導体集積回路が、基準ハイトセル30、マルチハイトセル40、VDD電源配線、VSS電源配線を備え、マルチハイトセルは、Y軸方向に延伸するVDD側電源供給配線5B、VSS側電源供給配線6Bを備え、基準ハイトセルの高さをa、マルチハイトセルの高さをb、VDD、VSS電源配線の幅をwとしたときに、VSS側電源供給配線は、少なくとも、マルチハイトセルの下端からw/2高さ方向に離れた位置とマルチハイトセルの下端からb−a−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられ、VDD側電源供給配線は、少なくとも、マルチハイトセルの下端からa+w/2高さ方向に離れた位置とマルチハイトセルの下端からb−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられる。

(もっと読む)

クロック分配回路

【課題】フィードバックパスのバラツキの影響を最小限に抑え、クロックの位相の調整を高精度に行うことができるクロック分配回路を提供する。

【解決手段】クロック分配回路21は、クロック信号を生成するクロック生成回路、前記クロック信号が分配されるクロック分配網22、前記クロック分配網の分岐点N1を通じて分配されるクロック信号で動作する順序回路26、を有する。クロック分配回路は更に、前記分岐点から分岐した前記クロック信号をフィードバック信号として入力し、該入力したフィードバック信号とリファレンスクロック信号とに基づいて、前記クロック信号を前記クロック分配網へ出力するクロック生成回路を有する。前記分岐点は、前記クロック分配網の順序回路の前段のクロックドライバ25のうち、前記クロック生成回路の近傍にあるクロックドライバに設けられる。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法、および半導体集積回路の設計装置

【課題】配線層に形成される信号配線をなるべく迂回させずに配線できるように電源スタックビアが配置された半導体集積回路を提供すること。

【解決手段】半導体集積回路は、第1の方向に延伸された第1,第2の下層電源配線11A,11Bと、第2の方向に延伸された第1,第2の上層電源配線12A,12Bと、上層,下層電源配線を接続させる第1,第2接続部3A,3Bと、を備え、第1,第2接続部は、第1,第2の接続用配線26A,26Bと、第1,第2の位置変換用配線27A,27Bと、第1,第2の上側ビア28A,28Bと、を有して構成され、第1,第2の接続用配線は、第2の方向に沿った同一ライン上に配置され、第1,第2の位置変換用配線は、第1,第2の接続用配線を第2の方向に沿って延長した領域内に形成され、第1,第2の上側ビアは、第1の方向に沿った同一ライン上となる位置に配置される。

(もっと読む)

半導体集積回路システムおよび半導体集積回路システムの配置配線方法

【課題】EMI低減に有効な半導体集積回路システムを提供する。

【解決手段】バスライン8上に配置された中央演算処理装置1と、演算論理装置6と、デカップリングキャパシタ形成領域100・合成論理形成領域200・インピーダンス形成領域300を有する半導体集積回路400と、論理ライブラリ情報格納部22・デカップリングキャパシタ配置配線情報格納部24・インピーダンス配置配線情報格納部26・電源配線配置配線情報格納部28を有する記憶装置2とを備え、論理ライブラリ情報格納部22・デカップリングキャパシタ配置配線情報格納部24・インピーダンス配置配線情報格納部26のそれぞれの格納データに基づいて、それぞれ合成論理形成領域200・デカップリングキャパシタ形成領域100・インピーダンス形成領域300における配置配線を実行する半導体集積回路システム10。

(もっと読む)

フロアプラン作成情報生成方法、フロアプラン作成情報生成プログラム、フロアプラン作成情報生成装置、フロアプラン最適化方法、フロアプラン最適化プログラム及びフロアプラン最適化装置。

【課題】フロアプラン設計におけるイタレーションを防ぎ、設計期間を短縮する。

【解決手段】複数の回路モジュールの接続情報を含むネットリストと、前記複数の回路モジュールにグループを設定するためのグループ設定情報と、を記憶部に記憶し、ネットリスト及びグループ設定情報に基づき、複数の回路モジュールにグループを設定し(S21)、設定されたグループ間におけるタイミング制約を満たす距離を算出し(S23)、算出されたグループ間の距離を含み、フロアプランを作成するためのフロアプラン作成情報を生成する(S25)。

(もっと読む)

クロック設計方法、クロック設計プログラム

【課題】半導体集積回路のクロック設計において、異なる2種類のクロック間の「セル遅延と配線遅延の比率α」の差を抑制する。

【解決手段】半導体集積回路は、第1クロック(CLK1)が供給される第1素子群と、第1クロック(CLK1)と異なる第2クロック(CLK2)が供給される第2素子群と、を備える。クロック設計方法は、第1クロック(CLK1)に関するクロックツリーシンセシスを実施することによって、第1クロックツリー構造10を作成するステップと、第1クロックツリー構造10の少なくとも一部を流用することによって、第2素子群に第2クロック(CLK2)を供給する第2クロックツリー構造20を作成するステップと、を含む。

(もっと読む)

スタンダードセル回路、半導体集積回路、及び半導体集積回路装置

【課題】スタンダードセル回路のレイアウト面積を削減する。

【解決手段】配線導体Laは電源電圧VDDaを出力する電源に接続される。レギュレータ6aは、配線導体Laからの電源電圧VDDaを電源電圧VDDaより低い電源電圧VDDbに変換し、配線導体Lbを介してレベルシフタ2−1〜2−3,3,及びスタンダードセル4に出力する。レベルシフタ2−1は、入力されるデータの電圧レベルを電源電圧VDDaの電圧レベルから電源電圧VDDbの電圧レベルに電圧シフトしてスタンダードセル4に出力する。レベルシフタ3は、スタンダードセル4からの出力信号の電圧レベルを電源電圧VDDbの電圧レベルから電源電圧VDDaの電圧レベルに電圧シフトし、出力端子Tqを介して出力する。

(もっと読む)

半導体集積回路装置

【課題】チップ面積を増加させることなく、効率良くリーク電流を抑制することができる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は論理が同一のセルA−1,B−1,C−1を備えている。セルB−1はセルA−1よりセル幅W2が大きいが、MOSトランジスタのゲート長L1はセルA−1と等しい。セルC−1は、セルB−1とセル幅W2が等しいが、ゲート長L2が大きいMOSトランジスタを有しており、セルA−1,B−1と比べて回路遅延は遅くなるがリーク電流は小さくなる。このため例えば、空き領域に隣接したセルA−1をセルB−1に置き換え、タイミングに余裕があるパスにおけるセルB−1をセルC−1に置き換えることによって、チップ面積を増加させることなく、リーク電流を抑えることができる。

(もっと読む)

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

半導体集積回路,および,半導体集積回路の検査方法

【課題】故障検査のために観測用フリップフロップ回路を配置することなく,故障検査を可能とする半導体集積回路,その検査方法を提供する。

【解決手段】第2の論理回路51の試験の際に試験モードを示す制御信号TSMが,故障検査用回路41に入力され,この試験モードに対応するテスト値が,論理回路51に入力されると,故障検査用回路41により,論理回路51の出力論理が,論理回路13に対応するフリップフロップ回路14に入力される。さらに,通常モード時に,論理回路13の出力論理が,故障検査用回路41により,論理回路13に対応するフリップフロップ回路14にそのまま入力される。

(もっと読む)

ESD保護検証装置

【課題】 寄生バイポーラの生成を抑制しつつ、開発遅延を効果的に防止できるESD保護検証装置を提供する。

【解決手段】 回路図データを受け付ける回路図データ取得手段11aと、回路図データから外部端子を抽出する外部端子抽出手段11bと、回路図データからESD保護素子を抽出するESD保護素子抽出手段11cと、寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、第1判定条件を満たすESD保護素子を対象素子として設定する第1判定手段11dと、配置配線処理において、寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように対象素子の配置処理を実行して、レイアウトデータを作成するレイアウト作成手段11eと、レイアウトデータを出力するレイアウトデータ出力手段11fと、を備える。

(もっと読む)

半導体集積回路の設計装置及び半導体集積回路の設計方法

【課題】チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようにする。

【解決手段】熱解析部11は、設計する半導体集積回路のデータから熱解析を行い、温度分布を算出し、ベクトル生成部12は、算出された温度分布の温度勾配に応じたベクトルを生成し、ダミーパターン生成部13は、生成されたベクトルにしたがってダミーパターンを生成し、半導体集積回路のレイアウトデータに追加する。このようなダミーパターンを生成することで、温度分布が平均化され、チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようになる。

(もっと読む)

レイアウト方法及び半導体装置の製造方法

【課題】ダブルパターニングによるトランジスタの特性ばらつきを抑える。

【解決手段】並列に配置される複数のゲート電極パターン10〜15を交互に、ダブルパターニングの第1の露光工程で形成する第1のパターン及び第2の露光工程で形成する第2のパターンとして設定し(ステップS1)、第1のパターンと第2のパターンとを並列に接続したトランジスタ対を含む回路をレイアウトすることで(ステップS2)、ダブルパターニングによるトランジスタの特性ばらつきが抑えられる。

(もっと読む)

セルの配置構造、半導体集積回路、及び回路素子セルの配置方法

【課題】セルベース設計において複数の記憶素子セルが配置される構成において、効率的に且つ確実に複数ビットのソフトエラーの発生を抑制することが可能なセルの配置構造を提供する。

【解決手段】回路素子セルの配置構造は、第1の方向に延展するセル配置列上に並べられた複数の記憶素子セルと、複数の記憶素子セルの各々の領域において第1の方向に垂直な第2の方向に並べられた第1のNウェル及び第1のPウェルと、複数の記憶素子セルのうち少なくとも2つの互いに隣接する記憶素子セルの間に設けられ、セル配置列の幅に亘る長さを各々が有する第2のNウェル及び第2のPウェルとを含み、第1のNウェルと第2のNウェルとは一体であり、第1のPウェルと第2のPウェルとは一体である。

(もっと読む)

半導体集積回路および半導体集積回路の設計方法

【課題】半導体集積回路の面積を増大させることなく、配線性のよいテスト専用回路の電源遮断を実現する半導体集積回路を提供する。

【解決手段】テスト実行時のみ動作するテスト専用回路を有する半導体集積回路1であって、当該半導体集積回路1の内部回路領域(内部制御回路部100)に電源を供給する通常電源(通常動作用電源)104と、当該内部回路領域の全面にメッシュ状に配線され、テスト専用回路に電源供給するテスト用電源103と、テスト用電源103と通常電源104とを接続及び遮断して、通常電源104からテスト用電源103への電源供給を制御する電源遮断スイッチ109と、を備える。

(もっと読む)

半導体集積回路装置のレイアウト設計方法

【課題】チップサイズの増大を抑制できる半導体集積回路装置のレイアウト設計方法を提供する。

【解決手段】外部電源電圧が供給される第一電源線と第一電源線にスイッチとなる第二電源ドライバを介して接続される第二電源線とを備えた、SCRC方式を採用した半導体集積回路装置において、第二電源ドライバのレイアウト面積の増大を抑制するために、半導体集積回路装置の全回路を機能別回路に分割し、機能別回路領域毎に、SCRC方式による制御対象の回路であるSCRC使用動作回路のトランジスサイズに応じて第二電源ドライバとして用いるMOSトランジスタのサイズを決定する。

(もっと読む)

半導体装置および半導体装置設計方法

【課題】半導体基板においてダミーパターンの配置密度を高める。

【解決手段】半導体基板104には、配線パターン102とダミーパターン106がレイアウトされる。配線パターン102の周囲にはマージン領域がレイアウトされ、マージン領域の周囲にダミー領域がレイアウトされる。このダミー領域に、複数のダミーパターン106がレイアウトされる。ダミーパターン106は、ダミー領域の延伸方向に配列される。マージン領域とダミー領域は、配線パターン102を基準として交互にレイアウトされる。

(もっと読む)

1 - 20 / 448

[ Back to top ]