Fターム[5F038EZ14]の内容

Fターム[5F038EZ14]に分類される特許

1,181 - 1,200 / 1,200

集積回路、集積回路の製造方法及び集積回路を製造するための組立部品、並びに該集積回路を有する携帯電話

集積回路は、気密封止された空洞(64)内の能動面(58)と、前記空洞を気密封止するカバー(66)と、を有するオンチップ電子部品(32)と、追加の電子部品(74)とを含み、前記追加の電子部品は、前記カバーに固定される。  (もっと読む)

(もっと読む)

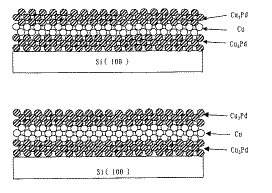

積層回路材料

【課題】特性インピーダンスを小さくできるために、超高周波又は超高速信号の伝送時においても反射や放射が少なく、かつ低損失である回路材料を提供する。

【解決手段】単一元素からなる原子層が単層若しくは複数層で構成する導体層と、導体層を構成する元素同士間の原子間結合よりもより安定な結合を形成する単一又は復数の元素からなる原子層が単層若しくは複数層で構成する拘束層とからなり、前記導体層と拘束層の原子同士が原子的整合状態(ヘテロ構造)で積層することを特徴とする回路材料の電気抵抗低下方法。

(もっと読む)

混合信号についての基板クロストークを低減する技術及びRF回路設計

集積回路は、半導体基板の上に形成された埋込絶縁層と、当該埋込絶縁層の上に形成された半導体メサとを有する。低抵抗率のガード・リングは、半導体メサを実質的に囲み、そして半導体基板と接触している。低抵抗率のガード・リングは、接地され、そして半導体メサをRF信号から分離する。  (もっと読む)

(もっと読む)

ダイ素子が積層された再構成可能なプロセッサモジュール

【課題】 集積回路(IC)ダイ素子が積層されたハイブリッド型の再構成可能なプロセッサモジュールを提供する。

【解決手段】 本明細書に開示する一実施形態に係る再構成可能なプロセッサモジュールは、薄いマイクロプロセッサダイ素子、メモリダイ素子および/またはFPGAダイ素子が積層され、ダイの厚み方向に貫通しているコンタクトによりこれらのダイ素子が相互接続される構造を持つとしてもよい。このようなプロセッサモジュールは、マイクロプロセッサとFPGA間でのデータ共有化速度を大幅に上げることができ、完成アセンブリの歩留まりを改善すると同時に完成アセンブリの製造コストを削減するという効果を奏する。

(もっと読む)

マイクロ波伝送線路

【課題】シリコン基板を信号伝播媒体とするマイクロ波伝送線路を長期安定性を維持しながら伝送損失の劣化を防止できるようにする。

【解決手段】高抵抗シリコンからなる基板1の主面上には、酸化シリコンからなる保護膜2、酸化アルミニウムからなる電位中和膜3及びストリップメタル4が順次形成されている。保護膜2は正の空間電荷を持ち、電位中和膜3は負の空間電荷を持ち、信号電界が基板1と保護膜2と電位中和とを伝播し、保護膜2及び電位中和膜3の各膜厚は、基板1の表面近傍における電位が中和されるように調整されている。

(もっと読む)

静電放電保護デバイスを備えた集積回路チップ

集積回路チップは、順に、基板材料から成る基板層、絶縁体から成る絶縁層、第1の導電体から成る第1導電層、誘電体からなる誘電層及び第2の導電体から成る第2導電層を有し、集積回路チップが少なくとも1つの集積回路及び少なくとも1つの集積静電放電保護デバイスを有し、静電放電保護デバイスが間隔を設けられた一対の中心電極及び周辺電極を有し、中心電極が第1導電層によって形成され、周辺電極が第2導電層によって形成され、電極対がステロイド・スパークギャップ空洞によって分離されており、ステロイド・スパークギャップ空洞の環状部が集積回路チップの絶縁層によって形成されたベース層、周辺電極によって形成された側壁、集積回路チップの誘電層によって形成されたカバー層、及び中心電極によって形成され絶縁層に接触するコンタクトパッドを有する環状部の中心部を有し、静電放電保護デバイスがまた、静電放電から保護されるべき入力回路パスに中心電極を電気接続する手段、及び回路グラウンド又は回路電源の何れかへの接続を有する静電放電パスに前記周辺電極を電気接続する手段を有する。本発明はまた上記集積回路チップの製造方法に関する。  (もっと読む)

(もっと読む)

集積トランジスタ、特に40ボルト以上の電圧用集積トランジスタ、およびその製造方法

本発明は、とりわけ、メイン領域からから遠い側に位置する接続領域(14)の方向に延伸する電気絶縁性を有する絶縁トレンチ(48)を有するトランジスタに関するものである。上記トランジスタは、メイン領域から、該メイン領域から遠い側に位置する接続領域(14)まで延伸する補助トレンチ(46)を有する。このトランジスタは、必要とするチップ面積が小さく、優れた電気的性質を示す。  (もっと読む)

(もっと読む)

高エネルギーESD構造および方法

同心リング状のESD構造(10)は、半導体材料の層(27)内に形成された第1p型領域(16)および第2p型領域(19)を含む。2つのp型領域(16,19)は、共に浮動n型埋込み層(26)に結合される。第1および第2p型領域(16,19)は、浮動n型埋込み層(26)と共にバックツーバック・ダイオード構造を形成する。1対の短絡されたn型(167,197)およびp型(166,196)の接触領域は、第1および第2領域(16,19)内にそれぞれ形成される。分離領域(17,32)は、第1および第2p型領域(16,19)間に形成される。  (もっと読む)

(もっと読む)

配線構造及びその製造方法

【課題】 高温で保持されても動作不良を起こさない、信頼性の高い多層配線構造を実現する。

【解決手段】 第1配線102Aと第2配線111とは、層間絶縁膜(SiO2 膜104及びFSG膜105)中に形成されたビア110Aを介して接続されている。第2配線111におけるビア110Aの接続部分の近傍にダミービア110Bが接続されている。ダミービア110Bは、実使用時において閉回路の一部分とはならない。

(もっと読む)

ミックスド・シグナル集積回路のための低クロストーク回路基板

高性能ミックスド・シグナル集積回路の応用に用いるための金属基板を有する集積回路ラミネート。金属基板は、大幅に改善されたクロストークアイソレーション、機能強化されたヒート・シンキング及び正確な低インピーダンス接地に対する容易なアクセスを提供する。一実施例では、金属ラガーは、チャネル又は空間に充填されている絶縁体及び金属基板とシリコン集積回路ラガーの間に配置されている非酸化多孔性シリコンのような絶縁体のラガーを伴う領域を有している。ラミネートもまた、金属基板に取り付けられていて、シリコン及び絶縁層を横断することによって、チップ上の雑音を生産する素子から雑音感応素子を分離する複数の金属壁又はトレンチを有している。他の実施例では、ラミネートは、チップの湾曲を制限する可撓性ベースに取り付けられている。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

底部電極(11)及び又はキャパシタ誘電体上に導電性平滑化層(16、19)を形成することにより、幾何学的に高くされた電場を低下させると共に、電極を平滑化することで、形成されるMIMキャパシタの信頼性を向上させることができる。一実施形態において、難溶性窒化物で形成された第1のキャッピング層(14)上には、難溶性金属又は難溶性金属リッチ窒化物を含む第1の層(16)が形成される。更に、キャパシタ誘電体上には、難溶性金属(18)又は難溶性金属リッチ窒化物を含む第2の層(19)が形成される。導電性平滑化層(16、19)は、例えば、ゲート電極とゲート誘電体との間のトランジスタ等の他の半導体装置にも使用される。  (もっと読む)

(もっと読む)

精密ポリシリコン・レジスタ・プロセス

【課題】 製造されるポリシリコン・レジスタのシート抵抗の許容誤差をより正確に制御する精密ポリシリコン・レジスタを製造するためのプロセスを提供する。

【解決手段】 プロセスは、一般に、部分的に形成されたポリシリコン・レジスタを有するウェハに対して、エミッタ/FET活性化高速熱アニール(RTA)を行うステップと、それに続いて、保護誘電体層をポリシリコン上に堆積させるステップと、ドーパントを該保護誘電体層を通して該ポリシリコンに注入して、ポリシリコン・レジスタの抵抗を定めるステップと、シリサイドを形成するステップとを含む。

(もっと読む)

基板上に多機能誘電体層を形成する方法

本発明は、多機能誘電体層を基板上、特に基板上に露出している金属配線系上に形成する方法に関する。本発明の目的は、銅による配線を形成するための多機能パッシベーション層を容易に形成する方法を提供するとともに、エレクトロマイグレーション、ストレスマイグレーション、および接着性を向上させる方法を提供することにある。本発明によれば、更なる金属層(5)を、露出した金属配線(3)の表面上に堆積することによって、本発明の目的は達せられる。この金属層は少なくともその一部が非導電性の金属酸化物に変換され、誘電体層となっている。  (もっと読む)

(もっと読む)

金属−絶縁物−金属キャパシタおよび配線構造

【課題】 金属−絶縁物−金属キャパシタおよび配線構造を提供する。

【解決手段】 ダマシン工程を利用してMIMキャパシタおよび配線構造を含む半導体装置を製造する。前記MIMキャパシタおよび配線構造は静電容量を増やしつつ同じ深さで形成する。

(もっと読む)

パンチスルー・ダイオードおよびそれを処理する方法

ショットキーのような動作を有するモノリシック集積パンチスルー・ダイオード。これは、ショットキー金属領域(16)が第1のpドープ・ウェル(9)の表面の少なくとも一部に堆積されるときに実現される。ショットキー金属領域(16)およびpドープ・ウェル(9)は、ショットキー・ダイオードの金属−半導体−遷移を形成する。順方向特性が0.5V未満の電圧降下を有するので、発明のPTダイオードの過電圧保護は改善される。  (もっと読む)

(もっと読む)

電極層および誘電体層を含む積層体ユニット

本発明にかかる積層体ユニットは、シリコン単結晶によって形成された支持基板と、支持基板上に、酸化シリコンによって形成されたバリア層と、バリア層上に形成され、c軸方向に配向されたビスマス層状化合物を含む誘電体材料よりなるバッファ層と、バッファ層上で、導電性材料をエピタキシャル成長させて形成され、c軸方向に配向された電極層と、電極層上で、ビスマス層状化合物を含む誘電体材料をエピタキシャル成長させて形成され、c軸方向に配向された誘電体層を備えている。  (もっと読む)

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】半導体素子の発熱に起因する半導体集積回路装置の温度上昇を低減する。

【解決手段】多層配線構造を備えた半導体集積回路装置において、多層配線構造を構成する接続孔及び金属配線層と同じ導電材料からなり、信号伝送用の接続孔及び金属配線層(領域C参照)とは異なる経路で上層側に延びる熱伝導部33,35,37を備えている(領域A,E,F参照)。領域Aにおいて、完全空乏型SOIトランジスタのゲート動作により発生した熱は、コンタクト層19、メタル配線層M1、ビア層21、メタル配線層M2に伝導され、さらに熱伝導部33を介して最上層のメタル配線層M6まで伝導され、絶縁層17の上面側から放熱される。これにより、半導体集積回路装置の温度上昇を低減することができる。

(もっと読む)

半導体装置

【課題】 半導体基板上のパターン密度の疎密によるトランジスタ特性のばらつきを抑制する。

【解決手段】 半導体基板1上の正規のPoly−R12等の回路素子に加えて、回路素子のパターン密度が均一になるように、半導体チップ内のほぼ全面にわたって、ダミーの機能素子となるPoly−R12aのパターンを配置する。さらに、このダミー用のPoly−R12aを、アルミ被りによる抵抗値の変動を抑制するためにLP−SiN膜17に覆われた構造とし、アルミ配線による抵抗値の変動を抑えるとともに、パターン密度の疎密による抵抗値、トランジスタ特性の変動を低減する。これにより、パターン密度の疎密によるトランジスタ特性のばらつきをなくし、さらに、アルミ被りによるPoly−Rへの影響や、赤外線吸収の素子疎密によるウェーハ内温度差を抑制する。

(もっと読む)

配線構造、インダクタ及びそれらの形成方法

【課題】 レイアウト設計上の自由度が大きく、しかも経済的に形成できる構成を備えた配線構造、インダクタ及びそれらの形成方法を提供する。

【解決手段】 本多層インダクタ60は、1層目のインダクタ64と、第1の層間絶縁膜66を介して1層目のインダクタ上に形成された2層面のインダクタ68と、第2の層間絶縁膜70を介して2層目のインダクタ上に形成された3層目のインダクタ72とを備えている。1層目のインダクタは、第1の層間絶縁膜を貫通するコンタクト76を介して2層目のインダクタに接続されている。2層目のインダクタは、第2の層間絶縁膜を貫通するコンタクト78を介して3層目のインダクタに接続されている。3層目のインダクタは、コイル巻線が接続配線74上をエアーブリッジ構造で跨いでいる。接続配線は、コイル巻線の下を通り、コイル巻線の中心部の接続端からコイル巻線に電気的に接触することなく多層インダクタの外部に出ることができる。

(もっと読む)

半導体装置の製造方法、強誘電体キャパシタ、およびその製造方法

【課題】 強誘電体キャパシタを有する半導体装置の製造において、強誘電体膜の自発分極を最大化する。

【解決手段】 下側電極を形成後、強誘電体膜を堆積する前に、前記下側電極を不活性雰囲気中において急速熱処理する。

(もっと読む)

1,181 - 1,200 / 1,200

[ Back to top ]