Fターム[5F043AA04]の内容

Fターム[5F043AA04]に分類される特許

1 - 18 / 18

半導体光素子の製造方法

【課題】過剰なエッチングを抑制するとともに半導体表面の突起物を除去する半導体光素子の製造方法を提供する。

【解決手段】半導体光素子の製造方法は、エッチストップ層13及び複数の半導体層を含み、半導体光素子のための半導体積層10を半導体基板11の主面11aにエピタキシャル成長させる半導体積層成長工程と、半導体積層10の最表面から突出する突起物の先端部が露出するように、最表面にマスク層を形成するマスク層形成工程と、マスク層を用いて、ウェットエッチングにより突起物をエッチングするウェットエッチング工程と、ウェットエッチングの後に、ドライエッチングにより突起物を除去するドライエッチング工程と、突起物を除去した後に、最表面からマスク層を除去するマスク層除去工程と、マスク層を除去した後に、半導体積層10に半導体光素子のための加工を行う加工工程と、を備えている。

(もっと読む)

エッチング液組成物およびエッチング方法

【課題】エッチングにより、適切に、エッチング対象物の表面に凹凸形状を形成して粗面化を行うことができるエッチング液組成物を提供する。

【解決手段】エッチング液組成物は、エッチング対象物の表面16をエッチングして凹凸形状を形成するエッチング液組成物であって、有機酸、有機酸塩、無機酸、無機酸塩、キレート剤、界面活性剤、糖アルコール類、フェノール類、アゾール類、および複素環化合物からなる群から選択される少なくとも一つと、酢酸と、フッ化水素酸と、硝酸とを含む。

(もっと読む)

発光素子

【課題】光取り出し効率を向上させることのできる発光素子を提供する。

【解決手段】発光素子1は、第1半導体層と、第2半導体層と、第1半導体層と第2半導体層とに挟まれる発光層とを有する半導体積層構造10と、半導体積層構造10の一方の面上に設けられ、線状表面電極部を有する表面電極50と、半導体積層構造10の表面電極50が設けられる側の反対の面側に設けられ、光を反射する反射層32と、半導体積層構造10と反射層32との間に設けられる誘電体層と、半導体積層構造10と反射層32とを電気的に接続し、線状界面電極部を有する界面電極40とを備え、線状表面電極部と線状界面電極部とがそれぞれ、平面視にて予め定められた方向に沿って延び、半導体積層構造10が、半導体積層構造10の反射層32の反対側の表面に、予め定められた方向とは異なる方向に沿って設けられる溝80を有する。

(もっと読む)

半導体基板の製造方法

【課題】厚みのある半導体基板に対し、正確な位置でのへき開を可能とするような十分な深さのガイド溝を形成する半導体基板の製造方法を提供する。

【解決手段】本発明に係る半導体基板の製造方法は、インジウムリン化合物半導体またはガリウムヒ素化合物半導体からなる基板本体の表面に、開口幅が略40um以下である開口部が形成されたマスクを、その開口部が基板本体のへき開線に沿って延びるように転写する工程と、基板本体の表面に臭素系のエッチング液を用いてウエットエッチング処理を施すことによって、縦断面で略V字型を有するガイド溝を形成する工程と、ガイド溝に反応性ガスを用いてドライエッチング処理を施すことによって、底部の縦断面形状を略V字型に保持したままガイド溝の溝深さを深くする工程と、を含むものである。

(もっと読む)

ウェハカセット及び半導体ウェハの表面処理方法

【課題】エピタキシャル成長前の表面処理(エッチング処理、洗浄処理、乾燥処理)において、半導体ウェハの表面パーティクル数が増大するのを効果的に抑制し、表面パーティクル数が少ない半導体ウェハを実現できる技術を提供する。

【解決手段】ウェハカセットを、当該ウェハカセットの前面を構成する前方支持体と、前方支持体に対向配置され、当該ウェハカセットの背面を構成する後方支持体と、収容される半導体ウェハを下方に案内する上溝部を有し、前方支持体と後方支持体を上部で連結する上側部フレームと、上溝部に対応して設けられ、収容される半導体ウェハを支持する下溝部を有し、前方支持体と後方支持体を下部で連結する下側部フレームとを備えた構成とする。上側部フレームと下側部フレームの間が開口し、側部周縁が開放された状態で半導体ウェハを収容可能となっている。

(もっと読む)

研磨具及び研磨装置

【課題】スクラッチの発生が少なく平坦な被加工面を得ることができ、しかも、基本的に触媒のみを交換できるようにすることで、安価かつ耐久性の良い研磨具を提供する。

【解決手段】表面に金属配線302を形成した光透過性の支持定盤300と、表面の少なくとも基板と接触する部分が触媒306からなり、光及びイオン電流の少なくとも一方を通過させるための複数の貫通穴304aを内部に有する触媒パッド308を有する。

(もっと読む)

エピタキシャルリフトオフを用いたフレキシブル光起電力デバイスの製造方法、およびエピタキシャル成長に用いる成長用基板の一体性を保持する方法

エピタキシャルリフトオフを用いる、フレキシブル光電(PV)デバイス等の感光性デバイスの製造方法が開示される。同様に、成長用基板を有する構造を含むフレキシブルPVデバイスを製造する方法が開示され、この方法では、保護層の選択的エッチングにより、再利用に好適な平滑な成長用基板が得られる。 (もっと読む)

半導体ウェハ及びこれを用いた半導体装置の製造方法

【課題】剥離面がナノオーダーの平坦性を持つ化合物半導体エピタキシャルフィルムを得る条件を備えた半導体ウェハ及びこれを用いた半導体装置の製造方法を提供する。

【解決手段】半導体ウェハ100は、半導体基板(例えば、GaAs基板101及びバッファ層102)と、この上に形成された剥離層103と、この上に形成された化合物半導体エピタキシャル層104とを有し、剥離層103の厚さを20nm以上200nm未満にしたものである。また、半導体装置の製造方法は、前記半導体ウェハを用意する工程と、エッチングマスクにより、化合物半導体エピタキシャル層をパターニングし、エッチング溝を形成する工程と、剥離層をエッチングし、化合物半導体エピタキシャル層を剥離することによって得られた化合物半導体エピタキシャルフィルムを基板上にボンディングする工程とを有するものである。

(もっと読む)

半導体基板

【課題】AlGaAs/InGaP界面の遷移層の形成を抑制する。

【解決手段】ヒ素化合物からなる第2半導体と、リン化合物からなる第3半導体とを含み、前記第2半導体と前記第3半導体とが接触しており、前記第2半導体が第1原子を第2濃度で含有し、かつ第2原子を含有し、前記第1原子が前記第2半導体に第1伝導型のキャリアを発生させ、前記第2濃度が、前記第2半導体にドープする前記第1原子の量を増加するに従い増加するキャリア数が飽和し始める前記第1原子の濃度以上の濃度であり、前記第2原子が前記第2半導体におけるフェルミ準位と電荷中性準位との差を小さくする半導体基板提供する。

(もっと読む)

電気絶縁材料の表面上の半導体層の厚さを減少しかつ均一化する方法

【課題】費用のかかる付加的露光装置を必要とせずに、SOIウェハの半導体層を均一化する方法を提供すること

【解決手段】電気絶縁性材料の表面上に存在する半導体層の厚さを減少しかつ均一化する方法において、半導体層の表面をエッチャントの作用にさらし、その酸化還元ポテンシャルを前記材料及び前記半導体層の所望の最終厚さの関数として調節して、前記半導体層の表面の単位時間当たりのエッチャントによる材料浸食を半導体層の厚さの減少と共に低下させ、かつ前記材料浸食は所望の最終厚さに達した場合に1秒当たり前記の厚さの0〜10%だけとなるようにし、その際、前記方法を光の作用なしで又は外部電圧の印加なしで実施する、半導体層の厚さを減少しかつ均一化する方法

(もっと読む)

パターン形成方法及びモールド

【課題】既存のリソグラフィ−技術よりも小さい寸法を有した様々な形状のパターンが形成できるようにする。

【解決手段】ガイドパターン702が形成された中性層801上に、例えば2種類のブロック鎖A及びブロック鎖Bから構成されたブロック共重合体(ジブロック共重合体)よりなるブロック共重合体薄膜703を形成する。中性層801は、表面自由エネルギーが、用いるブロック共重合体の各ブロック鎖の表面自由エネルギ−の範囲内に存在する材料から構成する。また、ブロック鎖Bは、ガイドパターン702の表面への親和性が高く、ブロック共重合体薄膜703をミクロ相分離させた場合、ブロック鎖Bが選択的にガイドパターン702の表面に接触するものとする。

(もっと読む)

半導体発光素子

【課題】 順テーパ型で対称性の高い均一なリッジ部を有する基板を用いた半導体発光素子を提供する。

【解決手段】 基板10上にマスクパターン11を形成し、まず、少なくとも {111}B面を含む結晶の面方位に対して依存性を持たない等方性ウエットエッチングを行う。次いで、少なくとも{111}B面を含んだ面方位に対して選択的に行われる選択性エッチングを行う。これら2種類のエッチングにより、両側面が{111}B面で構成されたリッジ部10aを有する基板10が作製される。この基板10上にSDH構造を形成して半導体発光素子が作製される。

(もっと読む)

基板の表面処理方法およびIII−V族化合物半導体の製造方法

【課題】 III−V族化合物半導体からなる基板をストイキオメトリにし、エピタキシャル成長後の表面の微小荒れを抑制する基板の表面処理方法およびIII−V族化合物半導体の製造方法を提供する。

【解決手段】 III−V族化合物半導体からなる基板を準備する工程(S10)と、基板を、pHを2以上6.3以下の酸性に調整するとともに酸化剤を添加した洗浄液により洗浄する洗浄工程(S20)とを備える。

(もっと読む)

半導体発光素子及びその製造方法、並びに半導体発光装置及びその製造方法

【課題】 半導体発光素子内部を循環したり側壁側へ漏れ出したりする光を減少させ、光取り出し面からの光取り出し効率を向上させることのできる半導体発光素子及びその製造方法、並びに半導体発光装置及びその製造方法を提供すること。

【解決手段】 III−V族化合物半導体層からなる半導体発光素子において、例えば、n型半導体層1の(001)面に光取り出し面20を形成し、活性層3を間に挟んで光取り出し面20の反対側に存在するp型半導体層4および5に、それぞれ(111)面および(11−1)面からなる、活性層3に達しない傾斜反射面24および25を形成する。傾斜反射面24および25は、同様にそれぞれ(111)面および(11−1)面からなる素子分離面21および22とともに、低温の塩酸をエッチャントとするウエットエッチングによって形成する。

(もっと読む)

半導体発光素子およびその製造方法

【課題】 端面がへきかいによって形成され、従来よりも基板面の利用率が高く容易に製造可能な半導体発光素子およびその製造方法を提供すること。

【解決手段】 結晶性の基板111と、基板111の一方の基板面上に設けられた、活性層を含む半導体層112と、基板111の半導体層112が設けられた基板面と反対側の基板面上に設けられた複数の第2の電極131a、131bと、半導体層112上の各第2の電極131a、131bに対向する位置に設けられた複数の第1の電極121a、121bとを備え、各第2の電極131a、131bが、へきかい位置を設定するへきかい位置指定領域134が隣り合う第2の電極131a、131b間に形成される形状を有し、へきかい位置指定領域134が、基板111の端の部分であるスクライブ領域132、133で広がり、へきかい位置指定領域134内に基板の一部が除去された溝を有する構成を有している。

(もっと読む)

グレーティングの製造方法及びグレーティング

【課題】 グレーティングの回折効率を向上させる。

【解決手段】 基板1上に第1の半導体層2aを、目的とするグレーティングの凹部の深さに相当する厚さまで成長させる(b)。次に、第1の半導体層2a上に第2の半導体層3aを形成する(c)。次に、グレーティングの凹部の形成予定位置に対応する第2の半導体層部位を除去する(e)。除去後に、第2の半導体層3c及び基板1に比べて第1の半導体層2cに対するエッチングレートが速いエッチャントを用いて、目的とするグレーティングのデューティ比に応じた時間だけ第1の半導体層2cをエッチングする(g)。

(もっと読む)

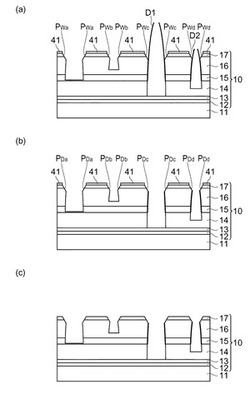

半導体装置の製造方法

【課題】InP層の成長に伴い形成された段差を平坦化する。

【解決手段】成長されたInP層に、少なくとも塩酸と酢酸とを含むエッチャントを使ったウェットエッチング工程を適用する。

(もっと読む)

HBTの製造方法

【課題】 オーバエッチングがべ一ス層まで及ぶことがなく、高速化を図ったHBTの製造方法を提供する。

【解決手段】 コレクタ層とベース層が同じエッチング液でエッチングされる材質で形成されている場合において、

を含んでいる。

(もっと読む)

1 - 18 / 18

[ Back to top ]