Fターム[5F044AA18]の内容

ボンディング (23,044) | ワイヤによるペレット電極との接続構造 (951) | 同一のパッド電極に複数本のワイヤ接続 (51)

Fターム[5F044AA18]に分類される特許

41 - 51 / 51

弾性表面波共振子

【課題】ワイヤ細線の共振現象による折損を抑え、信頼性の高い弾性表面波共振子を提供する。

【解決手段】弾性表面波素子の素子電極パッドと基板の接続用導体パターンの接続において、複数のワイヤ細線を介して接続を行う。また、複数のワイヤ細線は、互いに長さ、線径、材質を異ならせることで、機械的な固有振動数を相違させる。

(もっと読む)

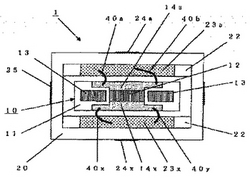

電力半導体装置

【課題】単位ワイヤ当たりの電流密度を小さくして、主電流ワイヤのボンド部の温度上昇を低減化することにより、スイッチング動作時に於ける熱サイクル疲労に対する寿命の向上化を図る。

【解決手段】主電流ワイヤ用ボンド部22aを有する主電流ワイヤ10のワイヤ群とは別に、電力用トランジスタ1のエミッタ電極13上と電力用ダイオード2のアノード電極14上とに、シングルボンド部21a,21bを有するボンディングワイヤ17aが、形成されている。加えて、電力用ダイオード2のアノード電極14の他端側上(エミッタ電極13とは反対側の端近傍の電極表面上)と第2主端子6の一端側寄り部分上とにシングルボンド部21c,21dを有するボンディングワイヤ17bが、形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ボンディング衝撃による不具合とプローブ動作時の不具合を改善するとともに、フェールセーフ的な構造とすることにより、直接能動領域上のボンディングパッド部へボンディングワイヤの接続を行うことを可能とした半導体装置およびその製造方法を提供する。

【解決手段】複数のパワー素子ユニットセルが、シリコン基板1の表層部に配置されたパ半導体装置H1であって、集電電極4上に、層間保護膜5が形成され、層間保護膜5に、複数個の開口部5kが互いに隣接して配置され、隣接する開口部5k間で層間保護膜5による衝撃吸収梁5hが形成され、複数個の開口部5kを介して、集電電極4に接続する厚膜電極6が設けられ、厚膜電極6へボンディング接続を行うために、複数個の開口部5kの上方において、最終保護膜7が開口されてなる半導体装置H1とする。

(もっと読む)

半導体装置

【課題】 チップの小型化に関わらず、ESD保護回路の容量を大きく維持したまま、I/O回路と信号伝送路との間のインピーダンス整合を高精度で維持し、チップに接続可能な信号線数を十分に多く確保する半導体装置、を提供する。

【解決手段】 第一と第二とのボンディングパッド(3、4)はチップ(2)上に、その周に沿って密に形成される。第一のボンディングパッド(3)はチップ(2)の周辺部に形成され、第二のボンディングパッド(4)はその周辺部より内側に形成される。第一のボンディングパッド(3)にはESD保護回路(7)が接続され、第二のボンディングパッド(4)にはI/O回路(8)が接続される。第一と第二とのボンディングワイヤ(5、6)は第一と第二とのボンディングパッド(3、4)を同じパッケージピン(1)に接続する。第二のボンディングワイヤ(6)は、第一のボンディングパッド(3)のピッチに関わらず、第一のボンディングワイヤ(5)より十分に長く設定される。

(もっと読む)

半導体モジュール

【課題】 二接続部間を複数のワイヤで接続する際各ワイヤの長さを同じ長さにする。

【解決手段】 ワイヤ接続部を含む配線及び外部電極端子を有するモジュール基板と、前記基板の上面側に固定され上面に電極を有する半導体チップと、半導体チップの電極とワイヤ接続部を接続する導電性のワイヤとを有し、半導体チップの所定の電極及び所定のワイヤ接続部は並列に配置されかつ長い形状となり、所定の電極及びワイヤ接続部は複数本の同じ長さのワイヤで接続され、所定の電極及び所定のワイヤ接続部のうちのいずれか一方の短辺の幅は、半導体チップの固定位置ずれによっても各ワイヤが接続できるようにワイヤを接続するに必要なワイヤ接続面積の数倍の大きさに相当する長さになっている。

(もっと読む)

電子装置

【課題】 高周波電力増幅回路を有する電子装置の高周波特性の合わせ込みを容易にする。

【解決手段】 携帯電話等に用いるRFパワーモジュールPMの増幅回路部を構成する半導体チップ15bが実装されたモジュール基板の主面の周囲に、平面蛇行形状の電極12E2を配置し、半導体チップ15bのボンディングパッドPと、上記電極12E2とを、その各々に接触した状態で接続されたボンディングワイヤBWによって電気的に接続する。ここで、上記電極12E2に対するボンディングワイヤBWの着地位置(接触位置)を変えることにより、RFパワーモジュールPMの出力電力および効率を調整する。

(もっと読む)

半導体装置並びにその製造方法及びそれを用いた電子機器

【課題】 低廉で信頼性の高い半導体装置を提供する。

【解決手段】 パワー素子である第1の半導体チップ1と、前記パワー素子を制御する制御回路が形成される第2の半導体チップ2とを備え、前記パワー素子が有する駆動端子の一つに電気的に接続される電極パッド1Aを第1の半導体チップ1の表面中央部に設けている半導体装置。

(もっと読む)

半導体装置、リードフレーム、及びその製造方法

【課題】 半導体チップからの複数のワイヤーを同一のリードに接続する接続構造において狭リードピッチを実現し、高集積度、高密度、小型の半導体チップを用いて高品質な半導体装置をコンパクトかつ安価に構成する。

【解決手段】 半導体チップ1をダイパッド2に搭載し、チップ表面の電極3とダイパッド2の周囲に配列されたリード4とをワイヤー5で接続し、半導体チップ1とワイヤー5とリード4のワイヤー接続部分とを一括して封止樹脂6で樹脂モールドした半導体装置を、少なくとも1本のリード4の先端部分に先端側が低くなるように段差部8が形成され、半導体チップ1上の同一または異なる電極3に接続した複数本のワイヤー5が前記段差部8の各段にそれぞれ接続された構造とする。これによって、半導体チップ1の縮小化、短ワイヤー化が可能となり、安定した電気特性を持った高信頼性の半導体装置をコンパクトかつ安価に構成できる。

(もっと読む)

半導体集積回路装置

【課題】 簡易な構成によって、チップ面積の増大を抑制し、パッケージのリード端子数の増大を抑え、さらには寄生インダクタンスを低減可能な半導体集積回路装置を提供する。

【解決手段】 本発明の半導体集積回路装置は、半導体基板上にもうけられた複数の回路ブロックのうち、互いに並列に動作状態になることのない第1の回路ブロック1と第2の回路ブロック2について、第1の回路ブロック1と第2の回路ブロック2のGNDラインG1を共通とした構成である。そして、一つのボンディングパッドPDとGNDラインG1とが電気的に結合されている。したがって、2つの回路ブロックのGND端子が1つとされるためリード端子数の低減が可能となる。

(もっと読む)

ワイヤーボンドを相互接続するための実装密度2倍化方法

集積回路パッケージ96において、第1ダイボンドパッド98に第1ワイヤー109をボンディングして第1ボンド108を形成し、ボンドポスト104に第1ワイヤー109をボンディングして第2ボンド106を形成する。第1ボンド108に第2ワイヤー111をボンディングし、このワイヤーをボンドポスト104に結合する。  (もっと読む)

(もっと読む)

マルチループ構成から形成されたインダクタンスループを有する集積回路パッケージ

集積回路パッケージが、リードワイアと1つまたは複数の入出力(I/O)パッケージピンとの接続から形成されるインダクタループを含む。一実施形態では、インダクタループは、集積回路チップ上の第1のボンディングパッドをパッケージの第1のI/Oピンに接続する第1および第2のワイアと、チップ上の第2のボンディングパッドをパッケージの第2のI/Oピンに接続する第3および第4のワイアとから形成される。インダクタループを完成するために、第1のI/Oピンと第2のI/Oピンは、ピン間の第3の導体によって接続される。第3の導体は、1つまたは複数のボンディングワイアを含むことができ、I/Oピンは、互いに隣接するものであることが好ましい。しかし、ループは、例えばループ長要件、空間の考慮すべき点、および/または他の設計要因もしくは機能要因に基づいて、I/Oピンの非隣接接続から形成することができる。他の実施形態では、第1のI/Oピンと第2のI/Oピンの間の接続が、I/Oピンに単一構造を持たせることによって確立される。他の実施形態では、第1のI/Oピンと第2のI/Oピンの間の接続が、パッケージ基板の表面上に、またはこの基板内に位置するメタライゼーション層によって確立される。集積回路パッケージの境界線内でインダクタループを形成することにより、空間要件における実質的な削減が実現され、これは小型化を促進する。また、集積回路は、その少なくとも1つのパラメータがパッケージのインダクタループの長さによって制御される様々なシステムのいずれか1つで実装することができる。

(もっと読む)

(もっと読む)

41 - 51 / 51

[ Back to top ]