Fターム[5F044AA20]の内容

ボンディング (23,044) | ワイヤによるペレット電極との接続構造 (951) | ワイヤ配置 (78)

Fターム[5F044AA20]に分類される特許

41 - 60 / 78

半導体装置

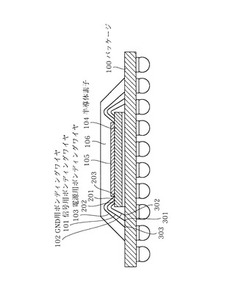

【課題】誤動作の原因となる電源・GNDノイズを低減し、信号に対する電源及びGND双方のリターンパスを確保する。

【解決手段】パッケージ100の上に半導体素子104が実装され、ボンディングワイヤ101〜103によってパッケージ100と半導体素子104の電気的接続をとる。半導体素子104においては、信号用パッド201の外側と内側にGND用パッド202と電源用パッド203が配置され、パッケージ100においては、信号用パッド301の内側と外側にGND用パッド302と電源用パッド303が配置される。信号用ボンディングワイヤ101を上下方向から電源用ボンディングワイヤ103とGND用ボンディングワイヤ102によって挟むことで、電源・GNDノイズに対するシールド及びリターンパスを構成する。

(もっと読む)

配線用チップ及び当該配線用チップを有する半導体装置

【課題】パッケージ全体としての配線インピーダンスを、配線経路によらず一定にする。

【解決手段】インターポーザ基板120と半導体チップ100とを接続するための配線用チップ110であって、前記半導体チップ100側に放射線状に設けられた複数の第1ボンディングパッド112と、前記インターポーザ基板120側に放射線状に設けられた複数の第2ボンディングパッド114と、前記複数の第1ボンディングパッド112と前記複数の第2ボンディングパッド114とを接続する複数の配線116と、を備え、前記複数の配線116は、それぞれ、同じ長さ及び同じ幅を有することを特徴とする配線用チップ110。

(もっと読む)

積層型半導体装置

【課題】複数の半導体素子を積層して樹脂封止するにあたって、上段側半導体素子に接続されたボンディングワイヤの樹脂封止時におけるワイヤ流れ等を抑制する。

【解決手段】積層型半導体装置1は、回路基板2上に積層して搭載された複数の半導体素子4、6、7を具備する。これら半導体素子4、6、7はそれぞれ金属ワイヤ5、8、9を介して回路基板2の接続パッド3と電気的に接続されている。上段側の半導体素子6、7に接続された金属ワイヤ8、9は、少なくともそれらの間に充填された樹脂固定部11で固定されている。積層された半導体素子4、6、7は金属ワイヤ5、8、9と共に樹脂封止部10で封止されている。

(もっと読む)

半導体パッケージおよびその製造方法

【課題】 ボンドパッドサイズとボンドパッドピッチ減少の限界を克服できる集積回路チップを提供する。

【解決手段】 集積回路チップ10は、センターパッド型チップ設計による集積回路が形成されたセル領域Acell1、Acell2の間に周辺領域Aperiを有する半導体基板11と、該半導体基板11上に集積回路と接続されるボンドパッド配線パターン12とを含む。ボンドパッド配線パターン12は、従来のボンドパッドが形成される層に所定のパターンを有するライン形態で形成され、一端が周辺領域Aperiに位置する。周辺領域Aperiの幅は、ボンドパッド領域が確保されていなくて、ライン形態である一部のボンドパッド配線パターン12だけが存在するので、従来と比べて狭くなっている。これにより、半導体基板11は、ボンドパッド領域のために必要な幅だけ減少された全体幅を有する。

(もっと読む)

半導体装置

【課題】メモリチップを複数積層する際の実装面積の増加を抑制する。

【解決手段】実装基板101の一方の面にこの順に搭載された第一メモリチップ103aおよび第二メモリチップ103bは、矩形の平面形状を有し、矩形の一辺に沿って一列にのみ配置された複数の電極パッドを含む。第二メモリチップ103bの電極パッド列は、第一メモリチップ103aの電極パッド列に平行に配置される。電極パッド列の一方の端部にチップセレクトパッドが配置される。第一メモリチップ103aのコントロール、アドレスまたはデータパッド113aが、矩形の一辺に沿って一列に配置された第一ステッチ109にワイヤボンディングされ、チップセレクトパッド121aおよびチップセレクトパッド121bは、チップセレクトパッド121aの側の隣接辺に沿って一列に配置された第二ステッチ111にワイヤボンディングされる。

(もっと読む)

半導体装置およびその製造方法

【課題】IGBT等のパワー半導体装置においてチップ面内の発熱による温度分布を均一化し、パワーサイクル寿命の向上を企図した半導体装置およびその製造方法を提供する。

【解決手段】この半導体装置10は、半導体チップ(IGBT素子11等)の表裏のチップ面に電極を備え、オン動作時に一方のチップ面の電極と他方のチップ面の電極の間で電流が流れる半導体装置であり、半導体チップの一方のチップ面の電極(エミッタ電極22−1〜22−6)には複数のワイヤ15が不均一な配置分布で接続され、かつ、所定の基準に基づいて、一方のチップ面の周辺部に接続されるワイヤの本数は一方のチップ面の中央部に接続されるワイヤの本数よりも多くされるように構成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】第1パッドを有する半導体チップに対しても、不必要な端子を増やすことなく検査を行うことのできる技術を提供する。

【解決手段】第1半導体チップに設けられた第1パッドを、少なくとも仮ボンディングワイヤを介して外部と電気的に接続させる仮ボンディング工程と、前記仮ボンディング工程の後に実施され、外部から前記仮ボンディングワイヤを介して電気信号を前記第1パッドに入出力させ、前記第1半導体チップを検査する検査工程と、前記仮ボンディングワイヤを取り外す仮ボンディング離脱工程と、前記仮ボンディング離脱工程の後に実施され、前記第1半導体チップを、少なくとも前記第1パッドが被覆される様に、封止する封止工程と、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】密集して配置される金属細線のレイアウトが工夫された半導体装置を提供する。

【解決手段】半導体装置10は、リード16と一体で設けられたアイランド14と、アイランド14の上面に固着された半導体素子18と、アイランド14に一端が接近して他端が外部に露出するリード16と、半導体素子18の上面に設けられたボンディングパッドとリード16とを接続する金属細線20と、これらの構成要素を被覆して一体的に支持する封止樹脂12とを概略的に具備する構成となっている。そして、半導体素子18の上面のボンディングパッド24は、複数の金属細線20を経由してリードの接続領域30と接続され、線長が長い金属細線20を、他の金属細線よりも半導体素子18の側辺に対して直角に近い角度で引き出している。

(もっと読む)

半導体装置の製造方法

【課題】金属細線の垂れ下がりに起因したショートの発生を防ぐ半導体装置の製造方法を提供する。

【解決手段】本実施の形態の半導体装置の製造方法は、アイランド14に半導体素子18を実装する工程と、半導体素子18の上面に設けたボンディングパッドとリード16とを金属細線20により接続する工程とを具備する。更に、本実施の形態では、金属細線20を形成する工程に於いて、アイランド14とリード16との間で、保持部50により金属細線20の中間部を保持している。このことにより、ワイヤボンディングの工程における金属細線20の垂れ下がりを防止して、金属細線20と半導体素子18とのショートを防止できる効果が得られる。

(もっと読む)

半導体装置及びその製造方法

【課題】ワイヤ数及び長を低減し、接合信頼性を実現することを目的とする。

【解決手段】一方の端部が第1ボンディング点にボールボンディングされ、他方の端部が第2ボンディング点にボンディングされてなる第1のワイヤループを有する半導体装置であって、前記第1のワイヤループのボール部の上面は、頂上部分がワイヤの一部を含めて潰された状態であり、前記ボール部の上面と第3のボンディング点とを架橋する第2のワイヤループを有する半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】多ピンの半導体チップを用いる半導体装置のボンディングワイヤどうしの接触をなくし、歩止まりを向上させる。

【解決手段】半導体チップ2の1主面上に形成された複数の電極3と前記半導体チップ2の周囲に配された導体部の内部電極4とを接続して互いに上下に配されるワイヤ5a,5b,5cの内、最下位のワイヤ5aに剛性が最も小さいものを用い、上位のワイヤ5b,5cに剛性がより大きいものを用いる。最下位のワイヤ5aは剛性が最も小さいことから、ワイヤ高さを低くできる。それよりも上位のワイヤ5b,5cの剛性が大きいと、ボンディング時にループ形状の制御が容易であるだけでなく、ボンディング後のループの変形が抑えられる。このため、ワイヤ5a,5b,5cどうしの接触を回避することが可能である。

(もっと読む)

半導体パッケージの設計・製造システムおよびプログラム

【課題】 設計側と製造側の作業負担や作業分担の適正化、設計・製造の効率化、時間短縮、コスト削減を図ることができる半導体パッケージの設計・製造システムを提供する。

【解決手段】 プロセス技術者が作成したプロファイルタイプやループパラメータ等のボンディング用データをCADシステム20へ送信し、CADシステム20でボンディング用データを用いてワイヤ隙間検査を行う。また、ワイヤ隙間検査後のデータをワイヤボンダ装置40または仮想ワイヤボンダ制御手段60に送信し、ワイヤボンダ装置40のワイヤボンダ制御手段42または仮想ワイヤボンダ制御手段60によりキャピラリ軌跡座標データを作成し、キャピラリ軌跡座標データをCADシステム20へ送信または出力し、CADシステム20でキャピラリ軌跡座標データを用いてキャピラリ干渉検査を行う。

(もっと読む)

半導体装置

【課題】 基板上に半導体チップが搭載され、半導体チップ上の接続パッドと基板上の上層接続パッドとがボンディングワイヤを介して接続され、半導体チップを含む基板上に封止膜が設けられた半導体装置において、ボンディングワイヤの基板に平行な方向のピッチが狭くなっても、封止膜を形成するための液状樹脂からなる封止膜形成用膜中の気泡がボンディングワイヤに引っかからずに大気中に抜け出るようにする。

【解決手段】 ボンディングワイヤ11、12とは1本おきに配置されている。ボンディングワイヤ12の最高点はボンディングワイヤ11の最高点よりも30μm以上高い位置にある。これにより、ボンディングワイヤ11、12の基板1に平行な方向のピッチが狭くなっても、相隣接するボンディングワイヤ11、12の各最高点間の間隔をピッチよりも大きくすることができる。

(もっと読む)

半導体装置及びワイヤーボンディング方法

【課題】半導体チップの各電極パッドと、半導体チップの周囲に配列されて相互に隣り合う2つのリードのそれぞれとを接続する複数本のワイヤーのうち、相互に最も近づくワイヤー同士の間で電気的な短絡が発生することを防止できるようにする。

【解決手段】各リード7,9における3本のワイヤー11〜13,15〜17のセカンドボンドをリード7,9の長手方向に並べ、一方のリード7に接続される3本の第1のワイヤー11〜13をリード7,9の配列方向に並べられた第1列の電極パッド19〜21に接続し、他方のリード9に接続される3本の第2のワイヤー15〜17を第1列よりもリード7,9から遠い位置に並べられた第2列の電極パッド23〜25に接続し、一方のリード7の最後方に接続される第1のワイヤー13を第2列の電極パッド23〜25に最も近い第1列の電極パッド21を除く第1列の他の電極パッド20に接続した半導体装置1を提供する。

(もっと読む)

アナログ・デジタル混載半導体装置

【課題】クロストークノイズの低減、チップサイズの小型化等を可能にする。

【解決手段】アナログ・デジタル混載半導体装置は、アナログ回路部32とデジタル回路部31とが混載された半導体チップ30と、この半導体チップ30の周辺部に配設され、デジタル回路部31に接続された複数のデジタルパッド35と、半導体チップ30においてデジタルパッド35の内側に配設され、アナログ回路部32に接続された複数のアナログパッド33と、半導体チップ30の近傍に設けられ、デジタル回路部31にデジタルワイヤ37を介して接続される複数のデジタルポスト21と、半導体チップ30の近傍に設けられ、アナログ回路部32にアナログワイヤ38を介して接続される複数の第2のアナログポスト22とを有している。そして、デジタルポスト21とアナログポスト22とを異なる配列に配置している。

(もっと読む)

半導体装置及びその製造方法

【課題】解読、偽造、捏造等が困難な安全性の高い識別情報を付与した半導体装置及びその製造方法を提供すること。

【解決手段】半導体素子5と配線基板のリード2とを電気的に接続する複数のボンディングワイヤ3を用いて、半導体装置1に識別情報を付与する。各ボンディングワイヤ3は、所定の複数の形態のうちのいずれかの形態を有すると共に識別情報を構成する識別要素の1つである。識別情報は、ボンディングワイヤ3の複数の形態の所定の配列ないし組み合わせにより形成される。

(もっと読む)

半導体チップ搭載基板

【課題】半導体チップ搭載基板で、ワイヤーボンディング接続するときの金属ワイヤーの長さに制限をなくし、基板製造コストの上昇を防止する手段を提供する。

【解決手段】ボンディングワイヤー15により基板11上電極13とチップ12上電極14とを接続する過程で、基板上電極とチップ上電極の中間位置にて金属ワイヤーの一部がワイヤー固定手段16を介して基板に接する構造を形成する。これにより金属ワイヤーの形状が安定し長い金属ワイヤーが使えるため、離れた位置にある細密ではない形状の基板電極と接続が可能になり、基板製造コストが削減される。

(もっと読む)

電子デバイス

【課題】低コストで製造される電子デバイスを提供する。また平面サイズの小型化をするとともに、薄型化した電子デバイスを提供する。

【解決手段】電子デバイスは、基板側パッド24を並べて基板20上に配設し、IC側パッド14が上面に並べて設けられたICチップ12を、IC側パッド14の並べられた方向と基板側パッド24の並べられた方向とを交差させて基板20上に設け、基板側パッド24とIC側パッド14とをワイヤ32で接合した構成である。このワイヤ32は、逆ボンディング法を用いて接合されている。そして電子デバイスには、IC側パッド14の並べられた方向に沿うICチップ12の側辺に隣接して電子部品が基板20上に設けられ、複数の基板側パッド24のうちの少なくとも一部と電子部品とが導通している。

(もっと読む)

半導体装置

【課題】ボンディングパッドの配置変換を簡易的確に行う。

【解決手段】ダイパッド31上には、複数個のボンディングパッド41を有する半導体チップ40が固着されている。半導体チップ40上には、中継チップ50が固着されている。中継チップ50は、複数個のボンディングパッド51を有し、この複数個のボンディングパッド51が、多層配線構造の配線パターン52によって相互に接続され、半導体チップ40側のボンディングパッド41の配置を異なる方向に変換する。ボンディングパッド41は、ワイヤ61によってボンディングパッド51に接続され、このボンディングパッド51が、ワイヤ62によってリードフレーム30側のボンディングパッド33に接続されている。

(もっと読む)

半導体装置

【課題】ボンディングパッドの配置変換を簡易的確に行う。

【解決手段】ダイパッド31上には、複数個のボンディングパッド41を有する半導体チップ40が固着されている。半導体チップ40上には、これよりもサイズの小さな中継チップ50が固着されている。中継チップ50は、複数個のボンディングパッド51を有し、この複数個のボンディングパッド51が、多層配線構造の配線パターン52によって相互に接続され、半導体チップ40側のボンディングパッド41の配置を異なる方向に変換する。ボンディングパッド41は、ワイヤ61によってボンディングパッド51に接続され、このボンディングパッド51が、ワイヤ62によってリードフレーム30側のボンディングパッド33に接続されている。

(もっと読む)

41 - 60 / 78

[ Back to top ]