Fターム[5F044AA20]の内容

ボンディング (23,044) | ワイヤによるペレット電極との接続構造 (951) | ワイヤ配置 (78)

Fターム[5F044AA20]に分類される特許

61 - 78 / 78

電子装置

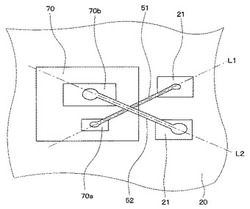

【課題】2つの部材を複数本のボンディングワイヤにより接続するとともに、これら複数本のボンディングワイヤをゲル部材により封止してなる電子装置において、ダミーのボンディングワイヤを用いることなく、ゲル部材によるボンディングワイヤのダメージを抑制する。

【解決手段】パワーICチップ70と回路基板20とを接続する第1のワイヤ51と第2のワイヤ52とにおいて、第1のワイヤ51におけるゲート用のパッド70aとの接続部および第1の回路基板20のパッド21との接続部を結ぶ線L1と、第2のワイヤ52におけるソース用のパッド70bとの接続部および第1の回路基板20のパッド21との接続部を結ぶ線L2とが交差した位置関係にある。

(もっと読む)

半導体装置およびその製造方法

【課題】複数のワイヤループと1本の隣接するワイヤループとの間のクリアランスを広く取りワイヤ間ショートを防止する。

【解決手段】第1,第2のワイヤループ12,13が上部から見ると重なる構造に形成して、これにより第1,第2のワイヤループ12,13と1本の隣接するワイヤループ14との間でクリアランスが広く取れ、封止時において樹脂によるワイヤ流れによって生じるワイヤ間ショートを防止することができる。さらに、パッド10においてボンディング部分を重ねることでパッド10のサイズを変えることなく、また、1つのパッド10と1つのリード端子11に第1,第2のワイヤループ12,13をボンディングすることで、半導体素子8の縮小を可能とする。

(もっと読む)

半導体装置に配設される中継部材及び半導体装置

【課題】 半導体装置に配設される中継部材のボンディングパッドの配列及び当該ボンディングパッドを結ぶ配線を任意に設定できるようにして、異なる構造を有する他の半導体装置に対しても適用することができる当該中継部材及び当該中継部材を備えた半導体装置を提供する。

【解決手段】 半導体装置に配設される中継部材50は、第1の端子51と第2の端子52とを備える。第1の端子51に接続される第1端子用配線56の端部及び第2の端子に接続される第2端子用配線57の端部のうち少なくとも1つにより連結部60が形成される。少なくとも前記連結部に接続部材61が形成され、第1の端子51と第2の端子52が接続される。

(もっと読む)

発振トランジスタ及び発振回路

【課題】 発振トランジスタのベース及びエミッタ用ボンディングワイヤ間の相互インダクタンスを低減して、発振周波数近傍における位相雑音特性の良好な数ギガヘルツ帯の発振回路を提供する。

【解決手段】 発振トランジスタのベースとベース端子12とを接続する第1のボンディングワイヤ15と、エミッタとエミッタ端子13とを接続する第2のボンディングワイヤ16とを備え、ベース端子とエミッタ端子の配線方向が直角であり、且つ第1及び第2のボンディングワイヤの配線方向が直角であるようにする。ボンディングワイヤ間もしくはベース端子とエミッタ端子との間に磁気シールド材を挿入しても良い。ボンディングワイヤ間の相互インダクタンスが低減され発振周波数近傍における位相雑音特性の良好な発振回路が得られる。

(もっと読む)

高速シリアル伝送用半導体装置とその製造方法

【課題】 周波数が1GHz以上の高速差動伝送に使用されるワイヤーのワイヤー長を等しくするという手段を採ることにより、IC設計の際に、問題となる個々のワイヤーのインダクタを考慮して設計する必要のない、設計容易な半導体装置とその製造方法を提供する。

【解決手段】 周波数1GHz以上の高速差動伝送を行う半導体装置において、基板7の配線に垂直な方向から見て、同一機能内の送信、受信、送受信に使用する差動信号ペアに使用されるボンディングワイヤー3、4、5、6のワイヤー長を全て等しくする。

(もっと読む)

半導体装置およびその製造方法

【課題】パッド上に形成したバンプにワイヤループの途中部分を接続することで、安定した接続を行いながらループを低くして半導体装置の薄型化を図る。

【解決手段】外部に露出する端子部をもつベース部33と、前記ベース部33に固着されるチップ32と、前記チップ32のパッド40上に形成されるバンプ41と、前記ベース部33と前記チップ32のパッド40との間を接続するワイヤ38と、全体を覆う封止樹脂39とを備えた半導体装置であって、ワイヤ38の1本以上がパッド40からベース部33に至る途中でバンプ41に接続される構成とすることで、ループ高さを低くすることが可能となり、半導体装置の薄型化を実現する。

(もっと読む)

積層化集積回路を備えた集積回路パッケージとそのための方法

集積回路パッケージ内で集積回路ダイを積層化するための改良された技術が開示される。これらの改良された技術によれば、集積回路パッケージ内の集積回路ダイの積層化密度をより大きくすることができる。更に改良した積層化技術によれば、従来の接合技術を用いて種々の集積回路ダイを互いに、又は基板に電気的に接続することができる。これら改良された方法は、同じサイズ(多くの場合同じ機能)の集積回路ダイを集積回路パッケージ内に積層化するのに特に有用である。そのような集積回路パッケージの一例として、積層体内に配置される複数の類似したサイズのメモリ保存集積回路ダイを備えた不揮発性メモリ集積回路パッケージが挙げられる。  (もっと読む)

(もっと読む)

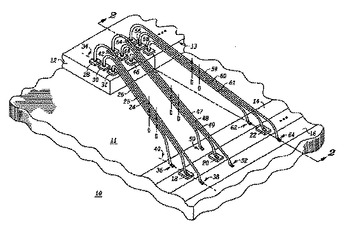

細長い電極を有する半導体デバイス用のワイヤボンドデバイスパッケージ

デバイスパッケージは、細長い長さの少なくとも1つの電極を有する、少なくとも1つの半導体デバイスを含んでいる。デバイスパッケージはまた、電極の細長い長さに平行に延びる、少なくとも1つの導電性パッドも含んでいる。端子リードは、導電性パッドと一体であるのがよい。複数の大体同じ長さのワイヤボンドにより、導電性パッドおよび半導体デバイスの細長い電極に電気的に接続するのがよい。別の案として、第2半導体デバイスを、導電性パッドに取り付け、複数のワイヤボンドを、この第2デバイスおよび第1半導体デバイスの細長い電極に電気的に接続するのがよい。 (もっと読む)

半導体装置

【課題】接続信頼性の高い半導体装置を提供する。

【解決手段】受光素子4に設けられた電極パッド10と、制御素子5に設けられた電極パッド10とを導通接続する2本のワイヤ8であって、第1のワイヤ11は、ファーストボンド11aが受光素子4の電極パッド10に接続され、かつセカンドボンド11bが制御素子5の電極パッド10に接続され、第2のワイヤ12は、第1のワイヤ11のセカンドボンド11bとした位置にセキュリティボンドとしたファーストボンド12aが接続され、かつ第1のワイヤ11のファーストボンド11aが接続された位置とは異なる位置にセカンドボンド12bが接続されている。

(もっと読む)

半導体装置

【課題】チップサイズを増大することなく、周辺回路と電極パッドとを接続する配線幅を大きくして電力供給能力を増大することを可能にした半導体装置を提供する。

【解決手段】内部回路3と、内部回路の周囲に配列した複数の周辺回路ユニットからなる周辺回路4と、周辺回路ユニットにそれぞれ配線で接続され、半導体チップの周辺に沿って配列した複数の電極パッド2とを備える半導体装置であって、周辺回路ユニット4A,4Bを半導体チップの周囲に沿って複数列の千鳥状に配置し、電極パッド2A,2Bはそれぞれ対応する周辺回路ユニット内に配置する。周辺回路ユニットの周方向の幅寸法を大きくでき、周辺回路ユニットと電極パッドとを接続する配線の配線幅を増大し、半導体装置の電極パッドにおける電力供給能力を改善する。

(もっと読む)

半導体装置

【課題】半導体チップ上にスイッチング電源などのようにスイッチング動作により機能する回路を形成した場合でも、1次電源側にノイズ除去用部品をつけることなく、高周波電流成分による高周波ノイズの半導体チップ外への漏れを低減することができる半導体装置を提供する。

【解決手段】半導体チップ上の電極パッドを複数並べ、それぞれの電極パッドとこれに対応する内部端子とを結線するワイヤ線を、同じ方向に電流が流れる向きのもの同士で組合せ、それぞれのワイヤ線の組内では、ワイヤ線がほぼ平行でほぼ同一の長さになるようにワイヤボンディングする。

(もっと読む)

半導体装置

【課題】 チップの小型化に関わらず、ESD保護回路の容量を大きく維持したまま、I/O回路と信号伝送路との間のインピーダンス整合を高精度で維持し、チップに接続可能な信号線数を十分に多く確保する半導体装置、を提供する。

【解決手段】 第一と第二とのボンディングパッド(3、4)はチップ(2)上に、その周に沿って密に形成される。第一のボンディングパッド(3)はチップ(2)の周辺部に形成され、第二のボンディングパッド(4)はその周辺部より内側に形成される。第一のボンディングパッド(3)にはESD保護回路(7)が接続され、第二のボンディングパッド(4)にはI/O回路(8)が接続される。第一と第二とのボンディングワイヤ(5、6)は第一と第二とのボンディングパッド(3、4)を同じパッケージピン(1)に接続する。第二のボンディングワイヤ(6)は、第一のボンディングパッド(3)のピッチに関わらず、第一のボンディングワイヤ(5)より十分に長く設定される。

(もっと読む)

電子装置

【課題】 高周波電力増幅回路を有する電子装置の高周波特性の合わせ込みを容易にする。

【解決手段】 携帯電話等に用いるRFパワーモジュールPMの増幅回路部を構成する半導体チップ15bが実装されたモジュール基板の主面の周囲に、平面蛇行形状の電極12E2を配置し、半導体チップ15bのボンディングパッドPと、上記電極12E2とを、その各々に接触した状態で接続されたボンディングワイヤBWによって電気的に接続する。ここで、上記電極12E2に対するボンディングワイヤBWの着地位置(接触位置)を変えることにより、RFパワーモジュールPMの出力電力および効率を調整する。

(もっと読む)

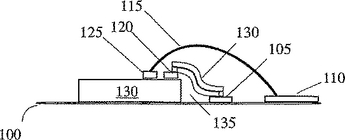

高密度パッケージ相互接続パワー及びグラウンドストラップならびにその方法

本発明の一態様は、デバイスのパワーまたはグラウンドとBGAパッケージとを接続する経路のインピーダンスを減らすことに関する。一つの特定の実現例では、シグナルボンドワイヤ(115)から所定の距離を置いてグラウンドストラップ(130)を配置することによって、シグナルボンドワイヤのインピーダンスを制御する。関係する実施形態では、ワイヤボンド(115)の近傍でデバイスダイ(140)とパッケージとの間に低インピーダンスのパワーまたはグラウンド接続を設ける。集積回路(140)は、複数のグラウンドパッド、シグナルパッド、パワーパッド、及び前記集積回路を実装するためのパッケージを含む。パッケージ(100)は、複数のパッドランディング(110)、集積回路(140)を取り囲むグラウンドリング(105)、及び集積回路のグラウンドパッド(120)にグラウンドリング(105)を結合するグラウンドストラップ(130)を備える。  (もっと読む)

(もっと読む)

リードフレーム基盤及び基板基盤半導体パッケージ用ボンディング構造とその製造方法

【課題】 リードフレーム基盤及び基板基盤半導体パッケージ用ボンディング構造とその製造方法を提供する。

【解決手段】 本発明は、半導体素子パッケージのボンディング構造において、チップダイのサイズが増加されないながらボンディングワイヤーのボンディング角が許容限界内に維持されるダイ−対−パッケージボンディング構造に関するものである。これにより、隣接したボンディングワイヤーの間の短絡発生が緩和されるか、或いは除去され、製造中の素子ネットダイカウント(ネットダイ数)を増加することができる

(もっと読む)

多層ボンディング構造の半導体デバイスのワイヤスイープを低減又は除去する方法とその方法によって製造された装置

【課題】 低い製造コストと高い信頼性で半導体デバイスを製作する方法を提供する。

【解決手段】 多層ワイヤボンディング半導体デバイスをパッケージ化する方法は、多層ワイヤボンディング半導体デバイスにおいて各層で素子間の接続をする複数の導線の少なくとも2本の一部のみを横切って絶縁材料を適用することを含む。その方法は、又、導線と素子を封止することにより、半導体デバイスをパッケージ化することを含む。

(もっと読む)

交差導電体アセンブリを備えた半導体パッケージ及びその製造方法

半導体パッケージでは、ボンドワイヤを介してダイボンドパッドと接続する様々な形態の導電性トレースが用いられる。一形態では、隣接するボンドワイヤが、その中間点付近で意図的に交差することで、導電体の自己インダクタンスが低減され、自己インダクタンスが最小化される。更に別の形態では、介入する関連しないボンドパッドを有するボンドパッドと接続したボンドワイヤ同士が交差する。更に、導電性トレースは、個別の部分に分割され、交差ジャンパワイヤやボンドワイヤによって、電気的に接続される。各トレースに対し、任意の数の個別部分を形成してもよいが、偶数が好ましい。更に別の形態において、あるトレースが連続性で、別のトレースが二つ以上の部分に分割される。複数の部分が、それを覆うボンドワイヤによって接続される。裸のボンドワイヤ及び被覆ボンドワイヤのいずれを用いてもよい。  (もっと読む)

(もっと読む)

ワイヤ・ボンドの位置付けを最適化した半導体パッケージ

密接配置したボンディング・ワイヤを種々の異なるパッケージング用途に用いると、電気的性能の向上を図ることができる。一実施形態では、ワイヤ群内にある2本の隣接するボンディング・ワイヤが密接配置されているのは、2本の隣接するワイヤのうちの短い方の長さの少なくとも50パーセントで、これら2本の隣接するワイヤ間において分離距離Dが満たされる場合である。一実施形態では、分離距離Dは、2本の隣接するワイヤのうちの直径が大きい方のワイヤの直径の多くとも2倍である。別の実施形態では、分離距離Dは、2本の隣接するワイヤ間のワイヤ間ピッチの多くとも3倍である。各ワイヤ群は、2本以上の密接配置ワイヤを含むことができる。密接配置ボンディング・ワイヤのワイヤ群を用いると、例えば、電力−信号−接地の三重組、信号−接地対、信号−電力対、あるいは差動信号対または三重組を形成することができる。  (もっと読む)

(もっと読む)

61 - 78 / 78

[ Back to top ]