Fターム[5F044KK07]の内容

ボンディング (23,044) | フェイスダウンボンディング用配線基板 (5,003) | 基板 (2,939) | 多層配線基板 (95)

Fターム[5F044KK07]に分類される特許

81 - 95 / 95

電子部品搭載基板の製造方法およびその方法により製造された電子部品搭載基板

電子部品搭載基板は以下のような方法によって製造される。まず、金属製の支持基板(1)の表面(1a)に、ビルドアップ絶縁層(21a〜21f)およびビルドアップ配線パターン(22a〜22f)を交互に形成する(ビルドアップ積層工程)。次に、前記支持基板(1)の裏面(1b)から表面(1a)に至る貫通孔(11)を形成して、最内層のビルドアップ絶縁層(21a)の裏面(211a)を露出させる(孔形成工程)。さらに、前記支持基板(1)の前記貫通孔(11)を介して前記最内層のビルドアップ絶縁層(21a)の裏面(211a)に電子部品(3)を搭載する(実装工程)。  (もっと読む)

(もっと読む)

半導体装置

【課題】熱膨張による熱ストレスが生じてもはんだバンプの断線や半導体チップのはがれのない信頼性の高いBGA構造の半導体装置を提供する。

【解決手段】積層された複数の絶縁層13、該複数の絶縁層それぞれの上面に設けられた複数の配線9、および異なる絶縁層上面に設けられた複数の配線を電気的に接続するために絶縁層に設けられた複数のビアホール12からなるBGA基板1と、前記複数の配線にそれぞれ接続される複数の電極を有する半導体チップ2とを含んでなる半導体装置であって、前記複数の絶縁層の材料が、半導体装置が実装される実装基板の熱膨張特性にあわせられた有機系材料からなる半導体装置。

(もっと読む)

はんだ接合を持つパッケージを使用した信頼できる印刷配線盤アセンブリおよび関連アセンブリ技術

例示的なアセンブリ(100)は、第一の表面を有する印刷配線盤(102)、はんだ球のようなパッケージの一つの表面にある、複数のはんだ接合を含むパッケージ(104)を備える。アンカーバイア(116,118)は印刷配線盤の第一の表面を通じて画定され、アンカーバイアに位置する伝導材料は、パッケージ(104)のそれぞれのはんだ接合と接続されるかそれぞれのはんだ接合と一体となる。本発明のアセンブリは、例えば第一の表面を有する印刷配線盤と、パッケージであって、該パッケージの少なくとも一つの表面上に複数のはんだ接合を含むパッケージと、該印刷配線盤の該第一の表面を通じて画定される少なくとも一つのアンカーバイアと、該少なくとも一つのアンカーバイアに位置する伝導材料であって、該複数のはんだ接合のうちの少なくとも一つと接続された伝導材料とを備える。  (もっと読む)

(もっと読む)

半導体装置、半導体装置の接続構造および半導体装置の実装方法

【課題】 接続相手の回路基板において制約の少ない配線形成を可能とし、高集積化、高信頼性化が可能な半導体装置およびこの半導体装置とこれと接続される回路基板からなる接続構造を提供する。

【解決手段】 半導体装置は半導体チップ(1)と、この半導体チップを支持し、前記半導体チップの接続電極が下面側に形成されると共に、階段状の突出部分を有する基板(2a,2b,2c,2d)とを備え、前記基板の前記階段状の突出部分は前記基板の外周に向かうにしたがって段階的に突出量が減少することを特徴とする。接続構造はこのような半導体装置と、その突出部分を収納する階段状に形成された凹部であって、その表面に前記突出部分に形成された接続電極と接続される配線パッドを有する配線基板とを備えたことを特徴とする。

(もっと読む)

パッケージ基板及びその製造方法

【課題】 部品実装パッド部を小径化すると共に、当該パッド部の接続強度を向上させたパッケージ基板の提供。

【解決手段】 部品実装パッド部の表層部にランド部が存在せず、かつ当該部品実装パッド部において回路面及び層間接続ビア面が絶縁層部面と同一平面上に形成されているパッケージ基板;ニッケルめっきを支持体として当該ニッケル支持体の上に絶縁層と層間接続ビアを形成する工程と、当該ニッケル支持体の剥離により層間接続ビアを表層部とした部品実装パッド部を形成する工程とを含んでいるパッケージ基板の製造方法。

(もっと読む)

配線構造および電子機器

【課題】配線パターンの形状が変化する場合の特性インピーダンス不整合を抑制すること。

【解決手段】本発明は、絶縁基板1の表面に形成される配線パターン11(第1の配線パターン)と、配線パターン11の幅が変化する部分に対応して絶縁基板1の内部に形成され、配線パターン11と電気的に並列接続される補助配線パターン12(第2の配線パターン)とを備える配線構造である。また、この配線構造の配線パターン11と導通する電極ランド10に電子部品を接続してなる電子機器である。

(もっと読む)

外部のボード上の組立部品及び組立部品を設ける方法

はんだ接続(18)でキャリア基板(10)の第1面(11)に取り付けられた電子装置(20)を含む組立部品。前記基板(10)の前記第1面(11)は、接続パッド(15)及びはんだレジスト層(16)を備える。前記基板(10)と前記電子装置(20)の間のどの空間にも封止材料(19)が充填される。前記基板(10)は、さらに、外部のボードに対する接続のためのコンタクトパッドを含む。前記はんだレジスト層(16)は、第1接続パッド(15)に隣接する開口(16)を含むパターンに従ってパターニングされる。この開口(161)はリング状で、前記第1接続パッドの外周を形成する。このようにして、ビア(142)が接続パッド(15)の下の基板(10)内に存在する場合にも、層間剥離を防ぐ。  (もっと読む)

(もっと読む)

回路基板の実装構造

【課題】第1の回路基板と第2の回路基板に配線された差動伝送路が、第1の基板の少なくとも一方の面に設けられたパッドと、それに対向する第2の回路基板の面に設けられたパッドと、そのパッド間に挿入された導体バンプによって接続する回路基板の実装構造において、半導体装置と回路基板、或いは回路基板同士で高周波信号の差動伝送をする際に生じる反射を低減し、高密度接続の容易性を損なうことなく、信号信頼度の高い回路基板の実装構造を提供する。

【解決手段】第1の回路基板の信号用の前記パッドに対面する位置における第1の回路基板のグランドプレーンは排除され、信号用の前記パッドに近接するグランドプレーンの排除された輪郭の一部が、対応するパッド形状の相似形であることを特徴とする回路基板の実装構造。

(もっと読む)

電子装置及びキャリア基板

電子装置は、半導体装置(10)、特に集積回路と、第1の面(21)及び第2の面(22)上に導電層を有すると共に、チェス盤パターンに従って相互に配列された電圧供給接続部(62)及び接地接続部(61)を有するキャリア基板(20)とを備える。これらの接続部(61、62)は、垂直相互接続部及びバンプ(41、42)を経由して、集積回路のボンド・パッドまで直通路の形で延び、集積回路のボンド・パッドは対応するチェス盤パターンで配列される。その結果、直通路のアレイが形成され、電圧供給接続部(62)が、できるだけ多くの同軸構造の同軸中心導体を形成する。  (もっと読む)

(もっと読む)

集積型電子チップ及び相互接続デバイス、並びにそれを製造するための方法

【課題】 集積型電子チップ及び相互接続デバイス、並びにそれを製造するための方法を提供すること。

【解決手段】 半導体デバイスと、マザーボードに接続するためのコネクタとを含む集積構造を形成するための方法が説明される。第1の層(26)が除去用放射線を通すプレート(23)上に形成され、第2の層(32)が半導体デバイス(31)上に形成される。第1の層は、マザーボードへの接続に必要とされる間隔に応じた第1の間隔距離だけ離されたボンディング・パッド(27p)に接続される導体の第1の組(27)を有する。第2の層は、半導体デバイスに接続される導体の第2の組(33)を有する。第1の層及び第2の層は、ボンディング・パッドの間隔より短い間隔を有するスタッド/バイア・コネクタ(29、36)を用いて接続される。このようにして、半導体デバイスが第1の層に取り付けられ、導体の第1の組と第2の組とがスタッドを通して接続される。第1の層とプレートとの間の界面が、該プレートを透過する除去用放射線(45)によって除去され、それによって該プレートが分離される。次いで、コネクタ構造(47、48、49)がボンディング・パッドに取り付けられる。本方法は、低コストで、高密度にパッケージされたデバイスを製造することを可能にする。

(もっと読む)

配線基板、半導体パッケージ、基体絶縁膜及び配線基板の製造方法

【課題】 半導体デバイス等の各種デバイスを高密度に搭載することができ、高速配線化及び高密度微細配線化が容易で、信頼性が優れた配線基板、この配線基板を使用する半導体パッケージ、及びこの配線基板の製造方法を提供する。

【解決手段】 配線基板13において、基体絶縁膜7を設ける。基体絶縁膜7の膜厚は3乃至100μmとし、温度が23℃のときの破壊強度を80MPa以上とし、温度が150℃のときの弾性率を2.3GPa以上とする。また、温度が−65℃のときの破断強度をa(MPa)、温度が150℃のときの破断強度をb(MPa)とするとき、比(a/b)の値を2.5以下とし、温度が−65℃のときの弾性率をc(GPa)とし、温度が150℃のときの弾性率をd(GPa)とするとき、破壊強度a及びb並びに弾性率c及びdが下記数式を満たすようにする。 (もっと読む)

(もっと読む)

電子装置

【課題】基体に対する電力増幅回路素子の接合強度を向上させることができるとともに、常に安定して動作させることが可能な電子装置を提供する。

【解決手段】基体1aの上面に枠体1bを取着させて枠体1bの内側にキャビティ4を形成するとともに、該キャビティ4内に、基体上面に設けられた接続パッド7に導電性接着剤9を介して電気的に接続される接続電極5を下面に有する電力増幅回路素子2を収容し、更に前記電力増幅回路素子2の直下に位置する基体1a上面に凹部8を設けた電子装置10であって、前記枠体1bの上面に、電力増幅回路素子2の上面に当接される金属製の放熱板3を接合する。

(もっと読む)

LSIパッケ−ジ及びそれに用いる内部接続工法

【課題】 ベアチップへのはんだバンプ形成・インタポ−ザへの実装という製造工程を不要とするLSIパッケージを提供する。

【解決手段】 ベアチップ4に設けられたベアチップI/O(入出力)端子3に接続する配線パタ−ン6を基板1のビルドアップ層2に形成し、ベアチップ4をLSIパッケージに実装する。その際、配線パタ−ン6は基板1の外部I/O端子7に接続するように形成される。

(もっと読む)

半導体チップ搭載用基板、半導体装置、およびその製造方法

【課題】 電気特性および放熱特性にすぐれた半導体チップ搭載用基板およびこの基板にパッケージングされた半導体装置を低コストで提供する。

【解決手段】 半導体チップ搭載用基板は、第1配線層と、第1配線層の下方に位置し、連続した無機補強材を有さない樹脂層から成る第1絶縁層と、第1絶縁層の下方に位置する第2配線層と、第2配線層の下方に位置し、連続した無機補強材を有する樹脂層から成る第2絶縁層と、第2絶縁層の下方に位置する放熱用金属板を有する。このような積層構造の基板は、第1配線層側に開口を有する半導体チップ搭載用のキャビティを有する。第2絶縁層の厚さ、あるいは第2絶縁層と、そのさらに下方にある任意の絶縁層の厚さの合計は、キャビティの深さの30%以上、98%以下を占める。

(もっと読む)

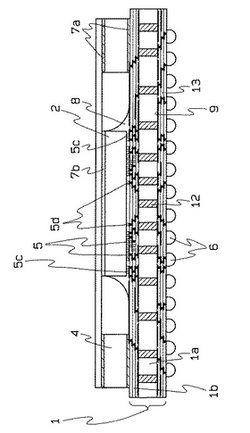

フリップチップ搭載用多層プリント配線板

【課題】 内層金属芯と外層金属箔との接続性、放熱性、吸湿後の耐熱性等に優れたフリップチップボンディング用多層プリント配線板を得る。

【解決手段】 表面は台形状の金属突起、裏面は複数個の円錐台形状金属突起を有する金属芯を用いたボールグリッドアレイの半導体プラスチックパッケージ用プリント配線板であって、多層積層時に表面平坦な両面銅張多層板とし、表面の半導体チップを搭載する台形状突起部上に流れ出した樹脂層をサンドブラスト法で除去して露出し、裏面は円錐台形状突起部先端が裏層銅箔と接続するように形成された熱放散用ハンダボールパッドとする。さらに、熱硬化性樹脂として多官能性シアン酸エステル系樹脂組成物を用いる。

【効果】 内層金属芯と裏面外層金属箔層との接続性、熱の放散性、吸湿後の耐熱性、プレッシャークッカー後の絶縁性、耐マイグレーション性などに優れ、大量生産性に適した新規な構造のフリップチップ搭載用プリント配線板を得ることができた。

(もっと読む)

81 - 95 / 95

[ Back to top ]